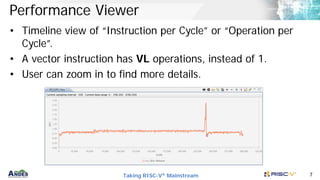

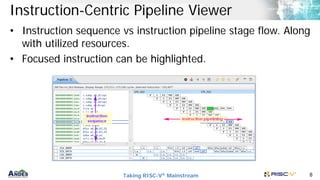

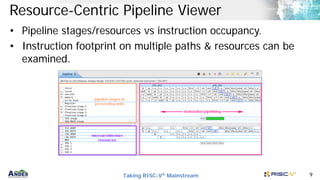

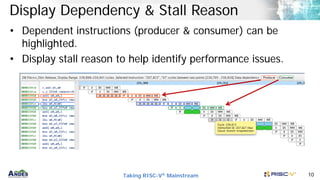

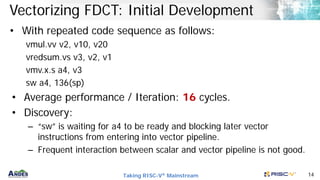

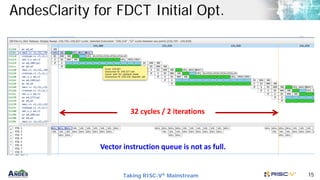

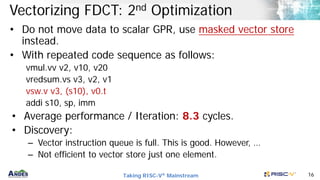

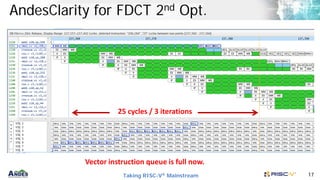

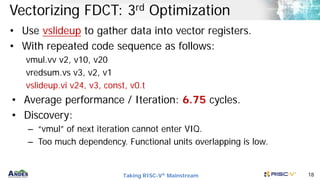

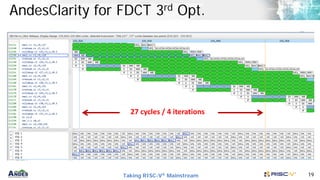

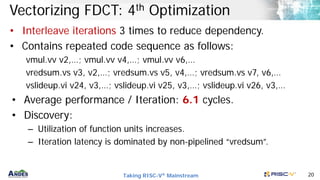

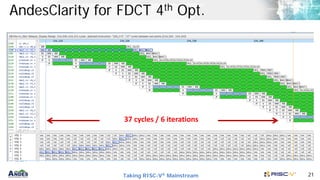

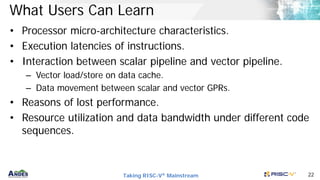

AndesClarity is a pipeline visualizer and analyzer for Andes V5 vector processors. It graphically represents instruction execution and pipeline stages with performance information. It helps optimize algorithms by identifying bottlenecks and stalls. The document provides an example of using AndesClarity to optimize a fast discrete cosine transform algorithm through four iterations. Each optimization interleaves instructions to better utilize the vector processor's functional units and reduce dependencies between iterations.