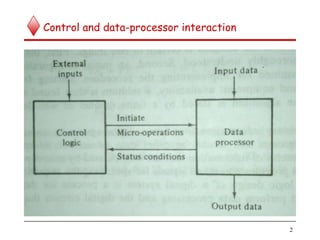

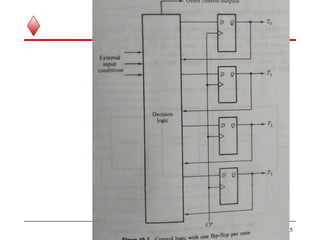

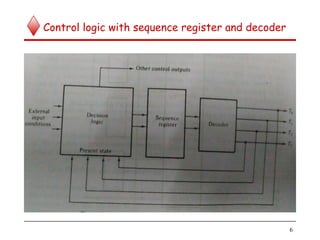

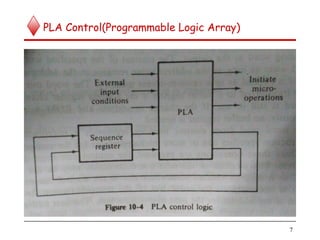

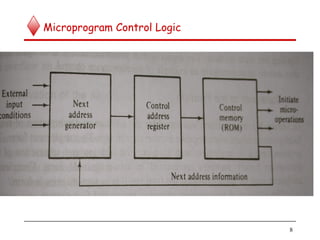

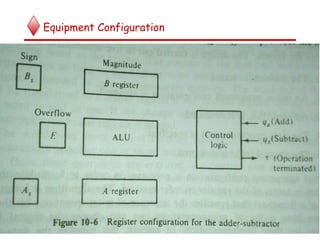

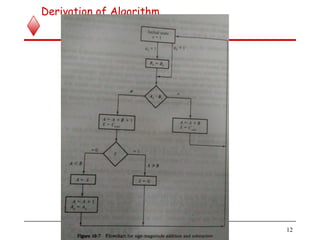

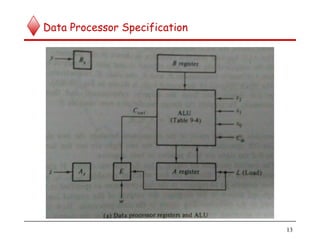

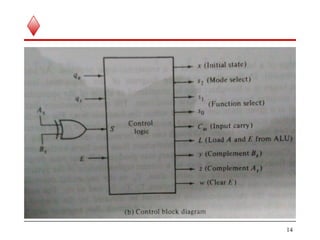

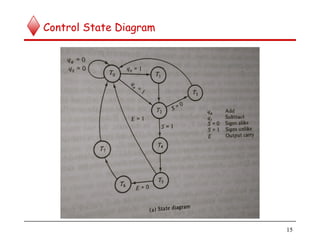

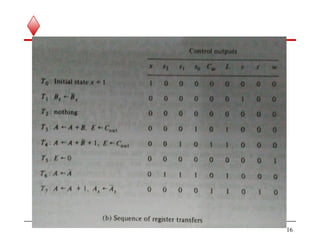

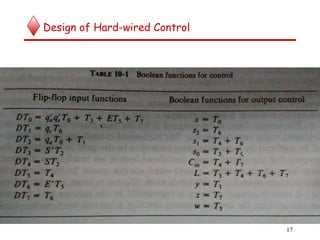

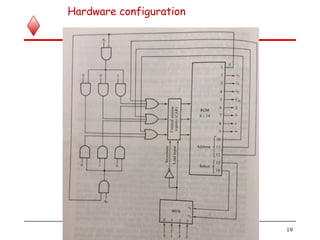

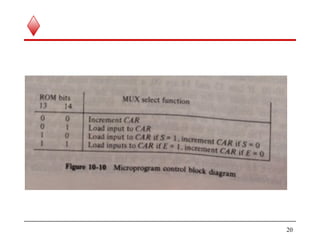

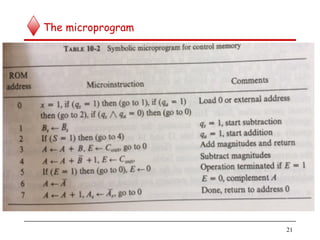

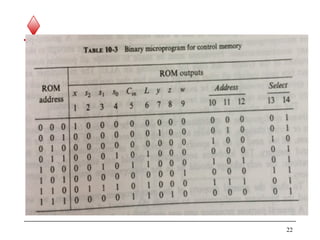

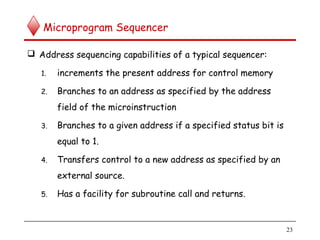

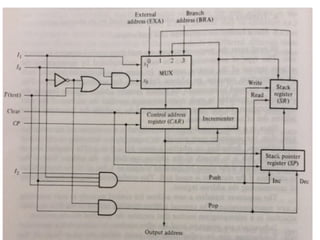

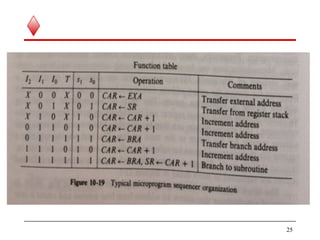

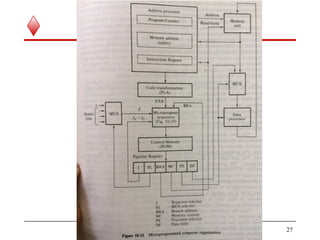

This document discusses different methods for control logic design including one flip-flop per state, sequence register and decoder, PLA control, microprogram control, and hard-wired control. It also describes the steps to design hard-wired control which are to state the problem, assume an initial equipment configuration, formulate an algorithm, specify the data processor, and design the control logic. Finally, it provides details on microprogram control including the hardware configuration, the microprogram, microprogram sequencer, and microprogrammed CPU organization.