The document discusses processor logic design and register transfer logic. It describes registers, their functions, and how data is transferred between registers. There are four categories of microoperations - interregister transfer, arithmetic, logic, and shift. Interregister transfer moves data between registers without changing it. Arithmetic operations perform math on register data. Logic operations perform AND, OR, etc on register bit values. Shift operations serially move data within a register. The document also discusses conditional control statements that allow different microoperations to be selected based on register values.

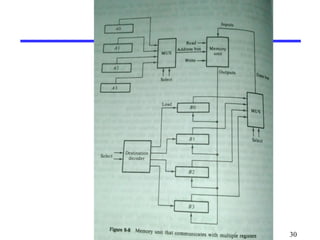

![Memory Transfer

Memory read : Transfer from memory

Memory write : Transfer to memory

Data being read or wrote is called a memory word (called

M)

It is necessary to specify the address of M when writing

/reading memory

This is done by enclosing the address in square brackets

following the letter M

Example: M[0016] : the memory contents at address

0x0016

25](https://image.slidesharecdn.com/module5-part1-170527041953/85/Module-5-part1-25-320.jpg)

![ Assume that the address of a memory unit is

stored in a register called the Address

Register AR

Lets represent a Data Register with DR,

then:

Read: DR ← M[AR]

Write: M[AR] ← DR

27](https://image.slidesharecdn.com/module5-part1-170527041953/85/Module-5-part1-27-320.jpg)

![CONDITIONAL CONTROL STATEMENTS

Conditional control statement is symbolized by an if-then –

else statement as follows:

P: If (condition) then [microoperation(s)] else

[microoperation(s)]

• It means that if the control condition stated within the

parentheses after the word if is true, then the

microoperation enclosed within the parentheses after

the word then is executed.

• If the condition is not true, the microoperation listed

after the word else is executed.

• In any case the control function P must occur for

anything to be done.

46](https://image.slidesharecdn.com/module5-part1-170527041953/85/Module-5-part1-46-320.jpg)