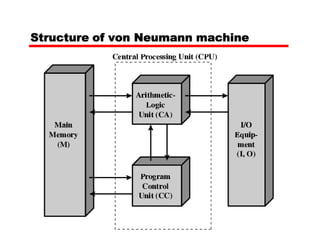

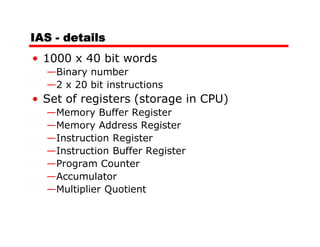

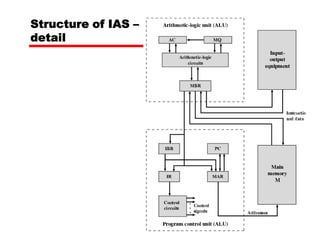

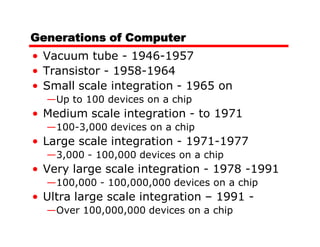

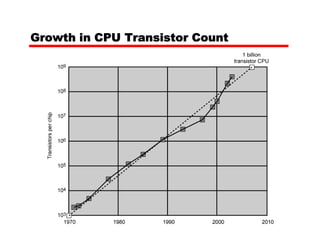

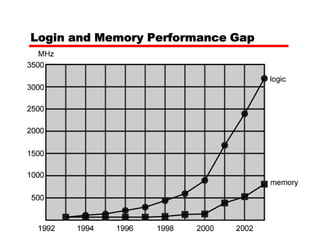

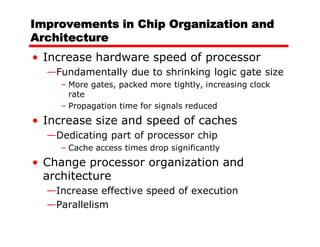

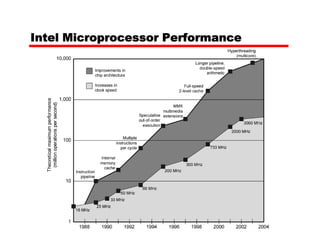

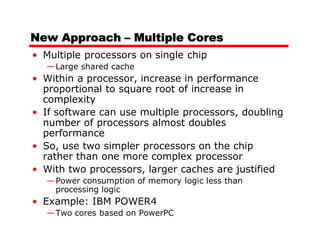

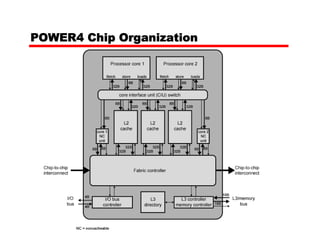

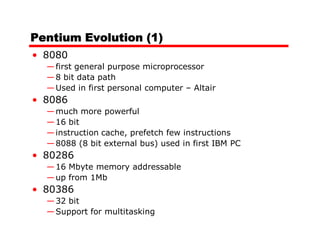

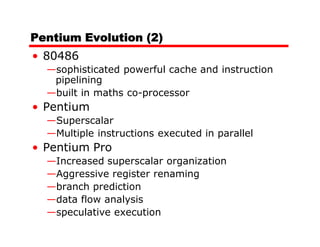

This document summarizes the evolution of computer architecture from early computers like ENIAC through modern multi-core processors. It discusses key developments like stored programs, transistors replacing vacuum tubes, integrated circuits, memory hierarchies, and parallelism through pipelining and multiple cores. Moore's Law of increasing transistor counts is also summarized.