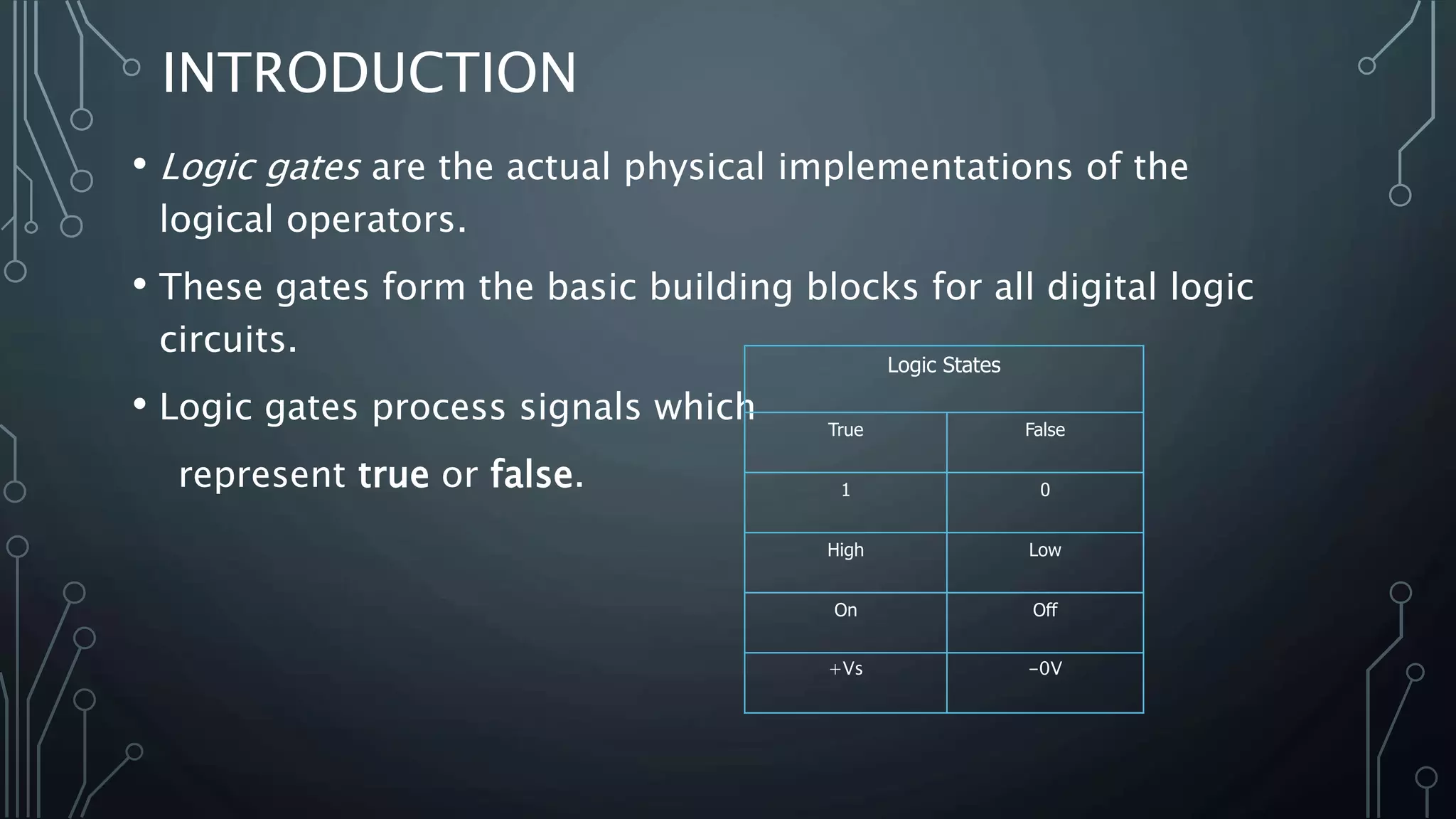

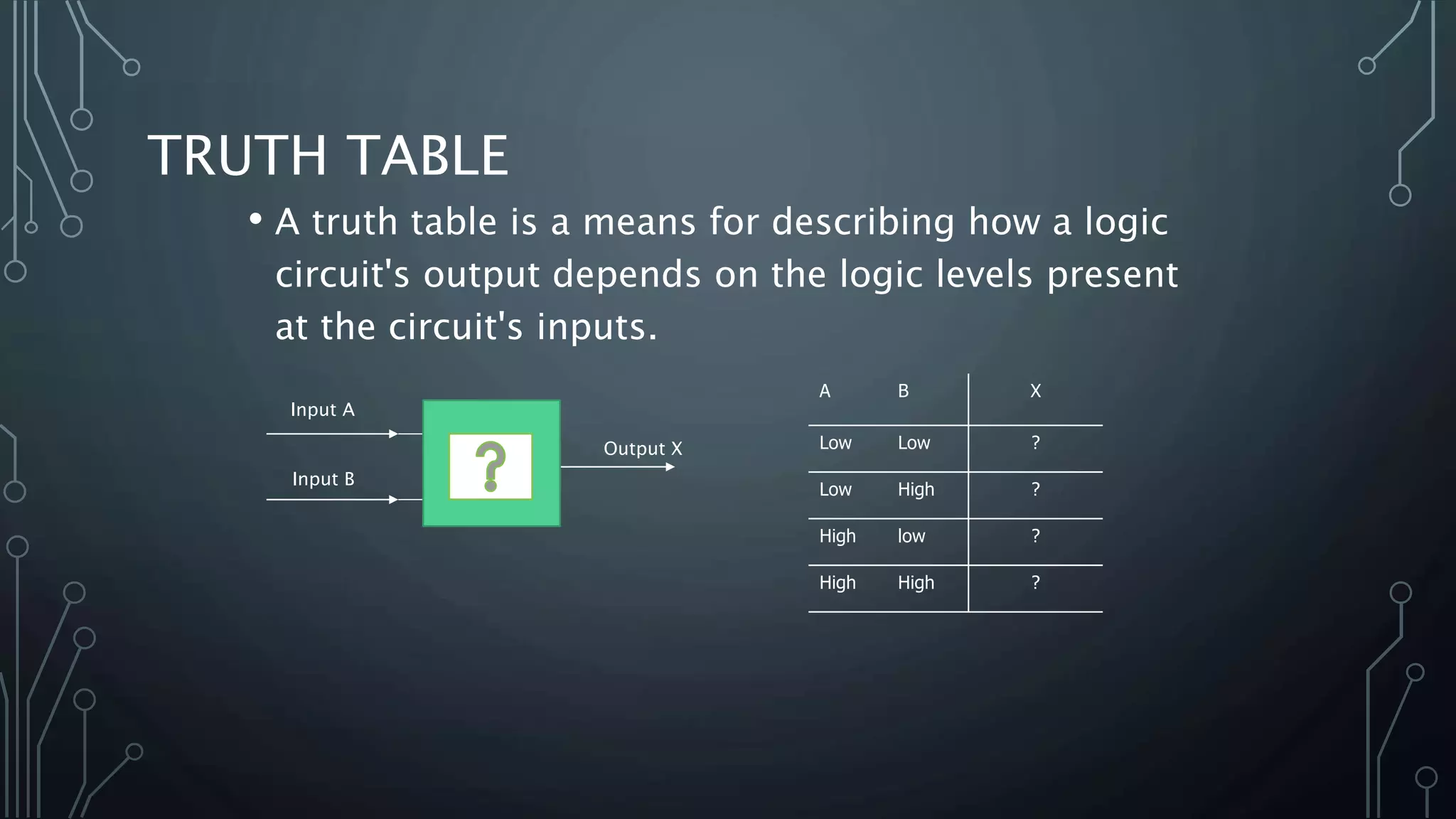

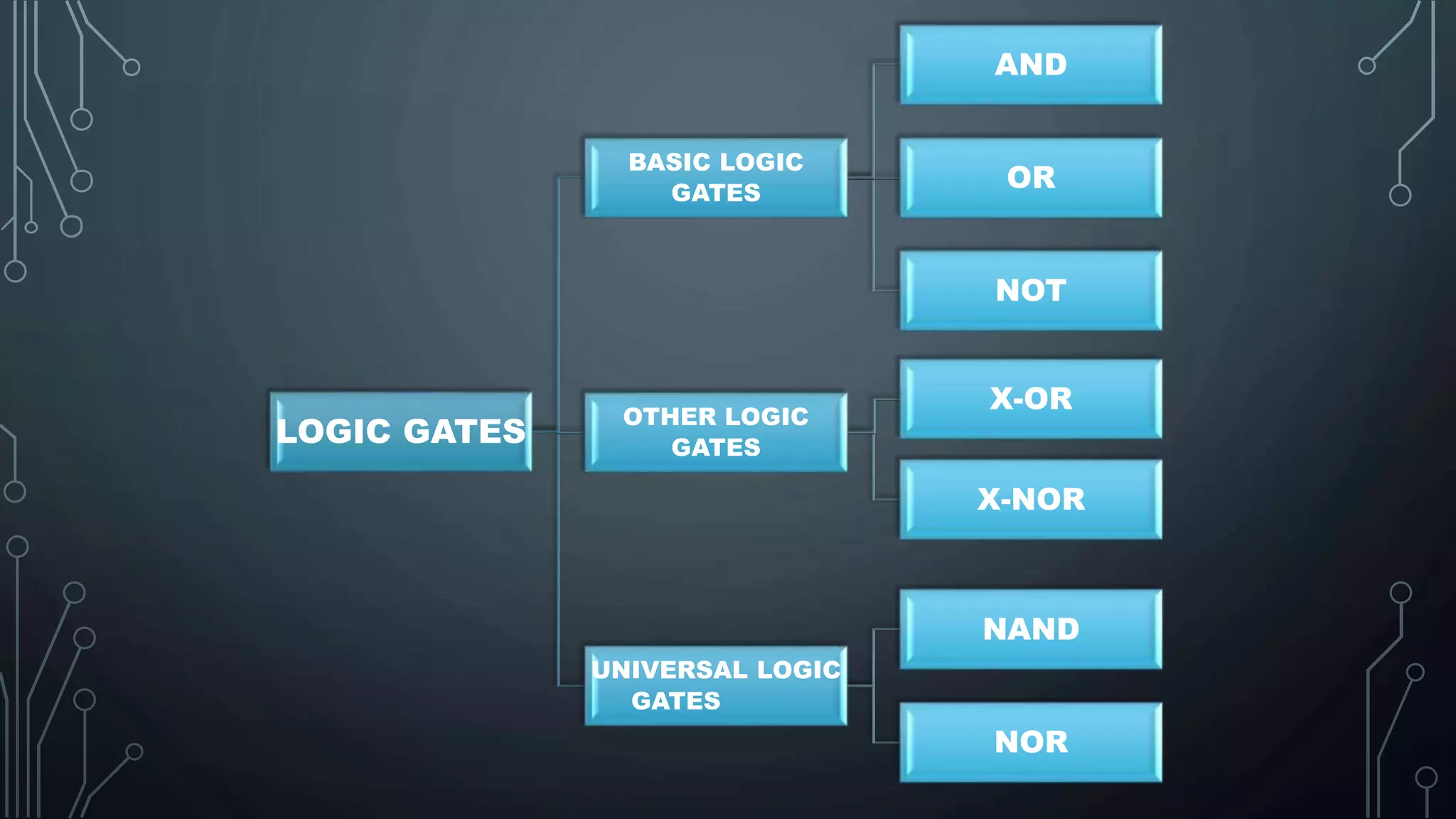

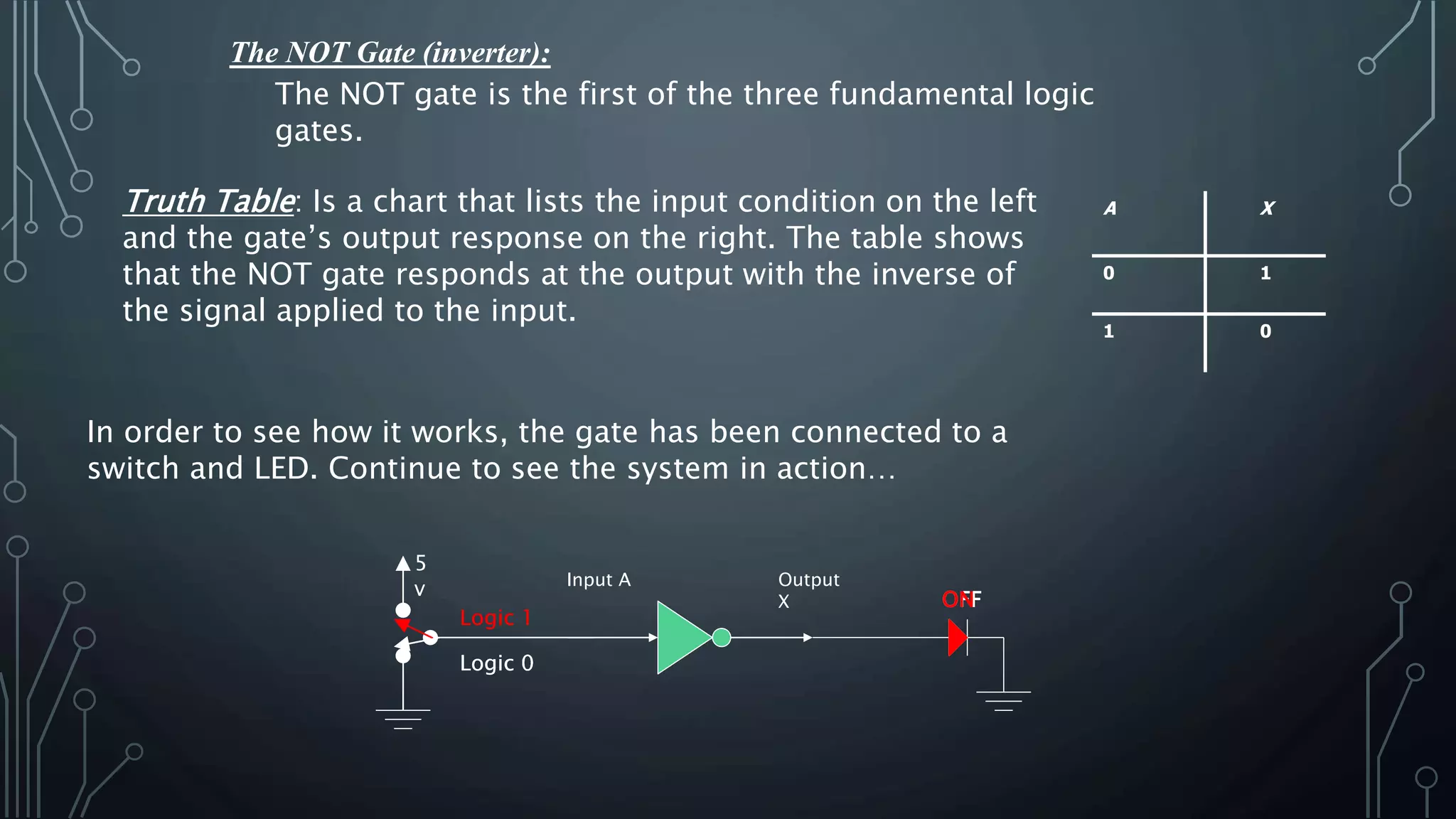

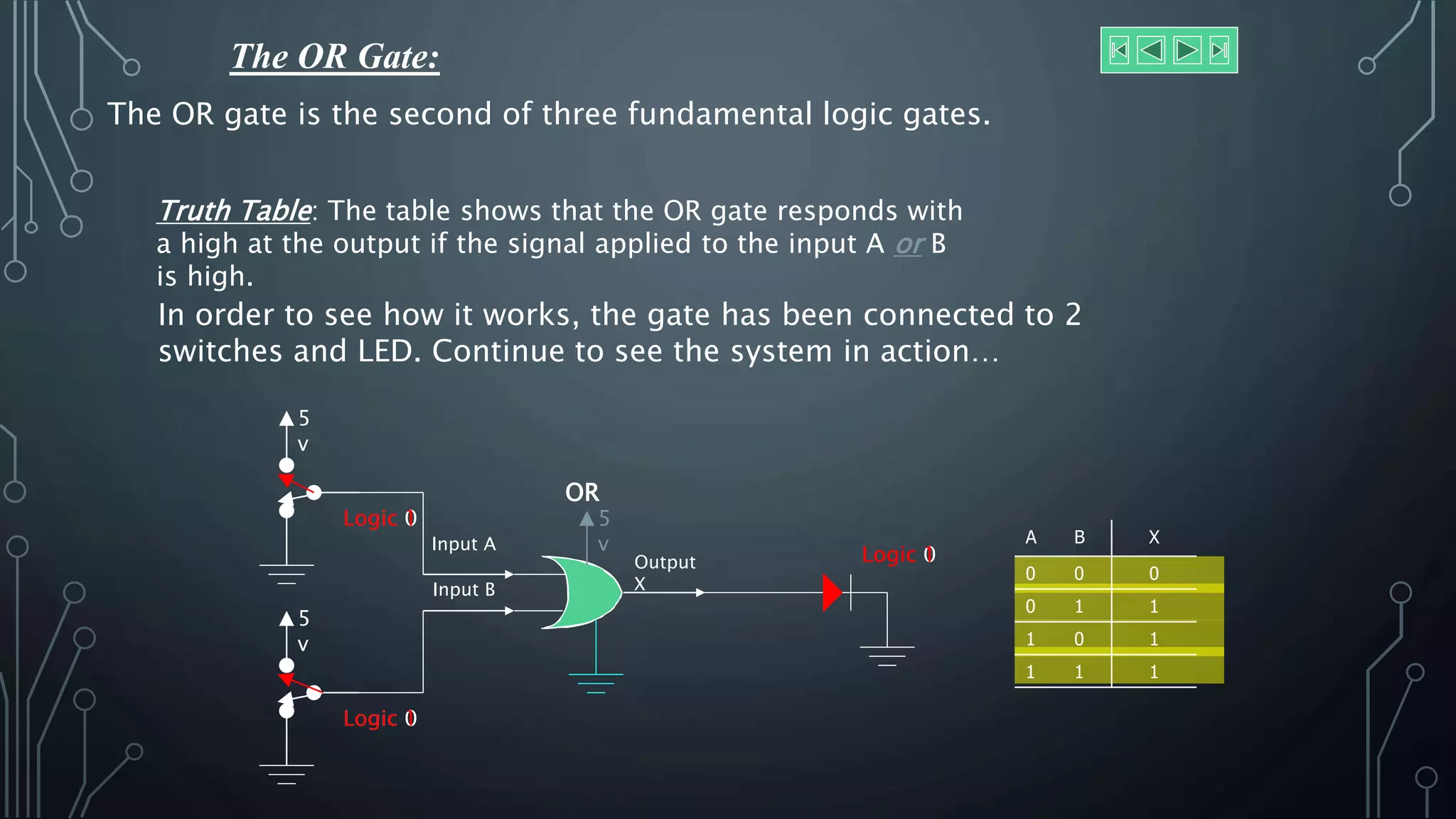

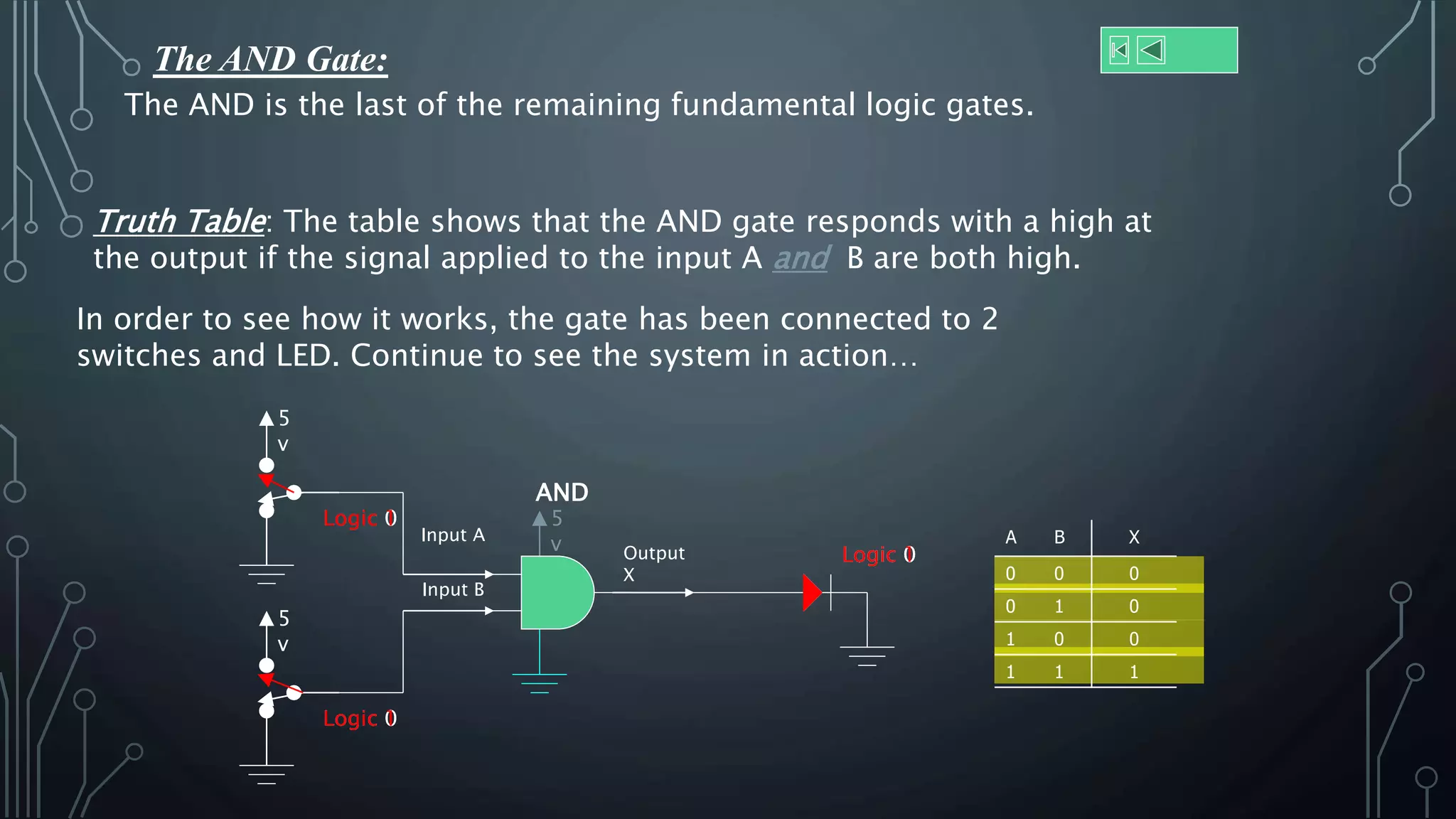

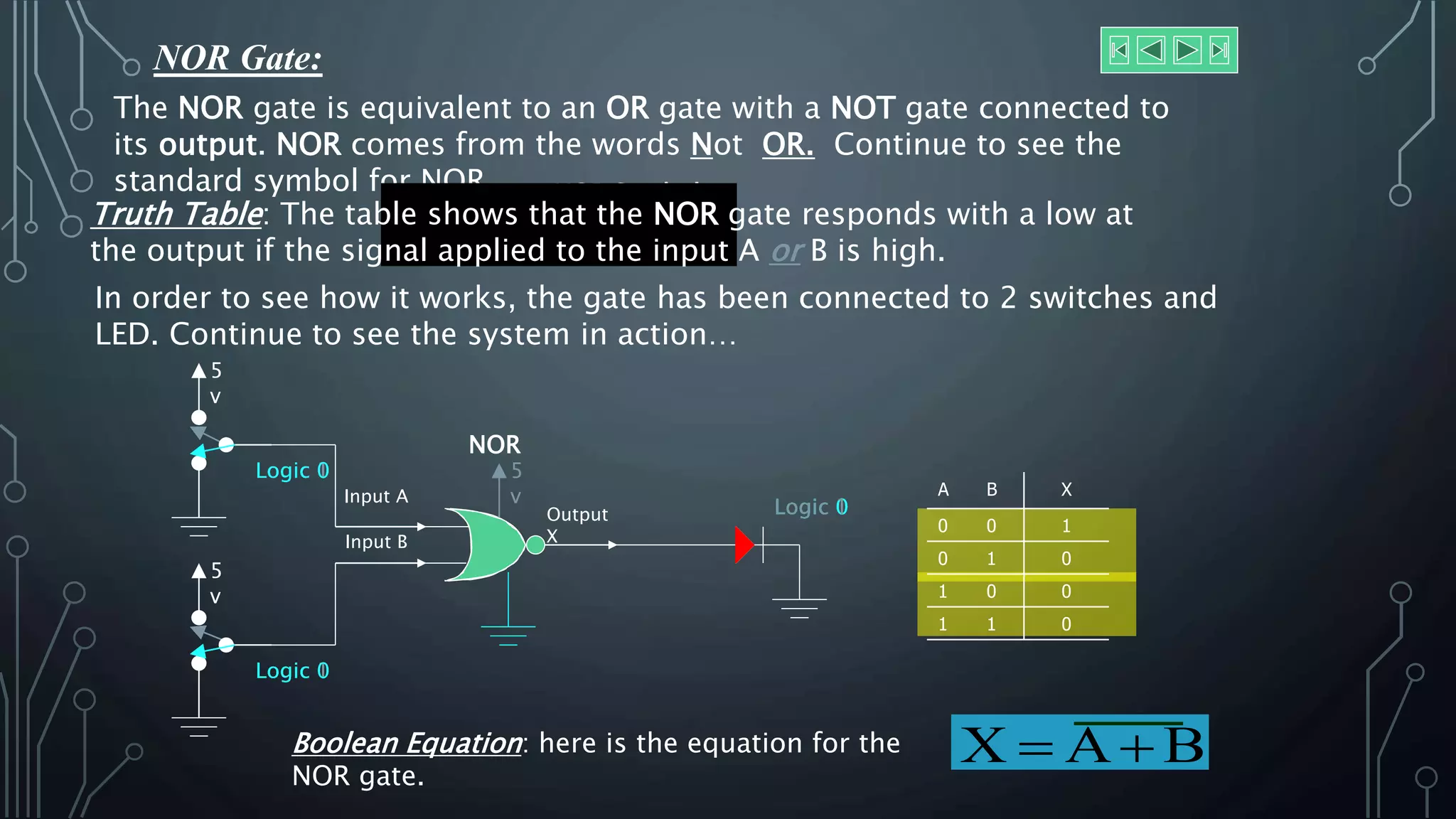

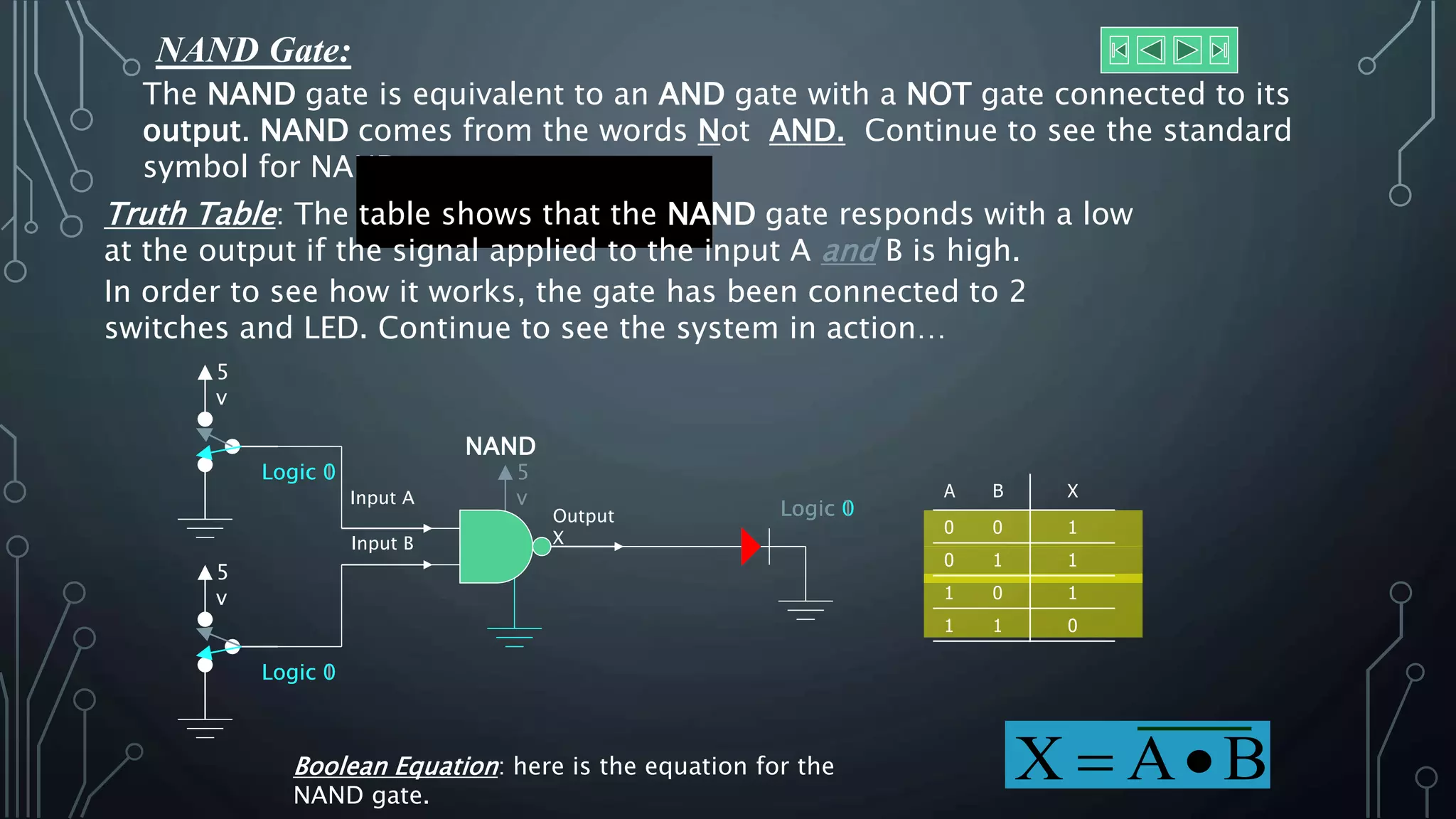

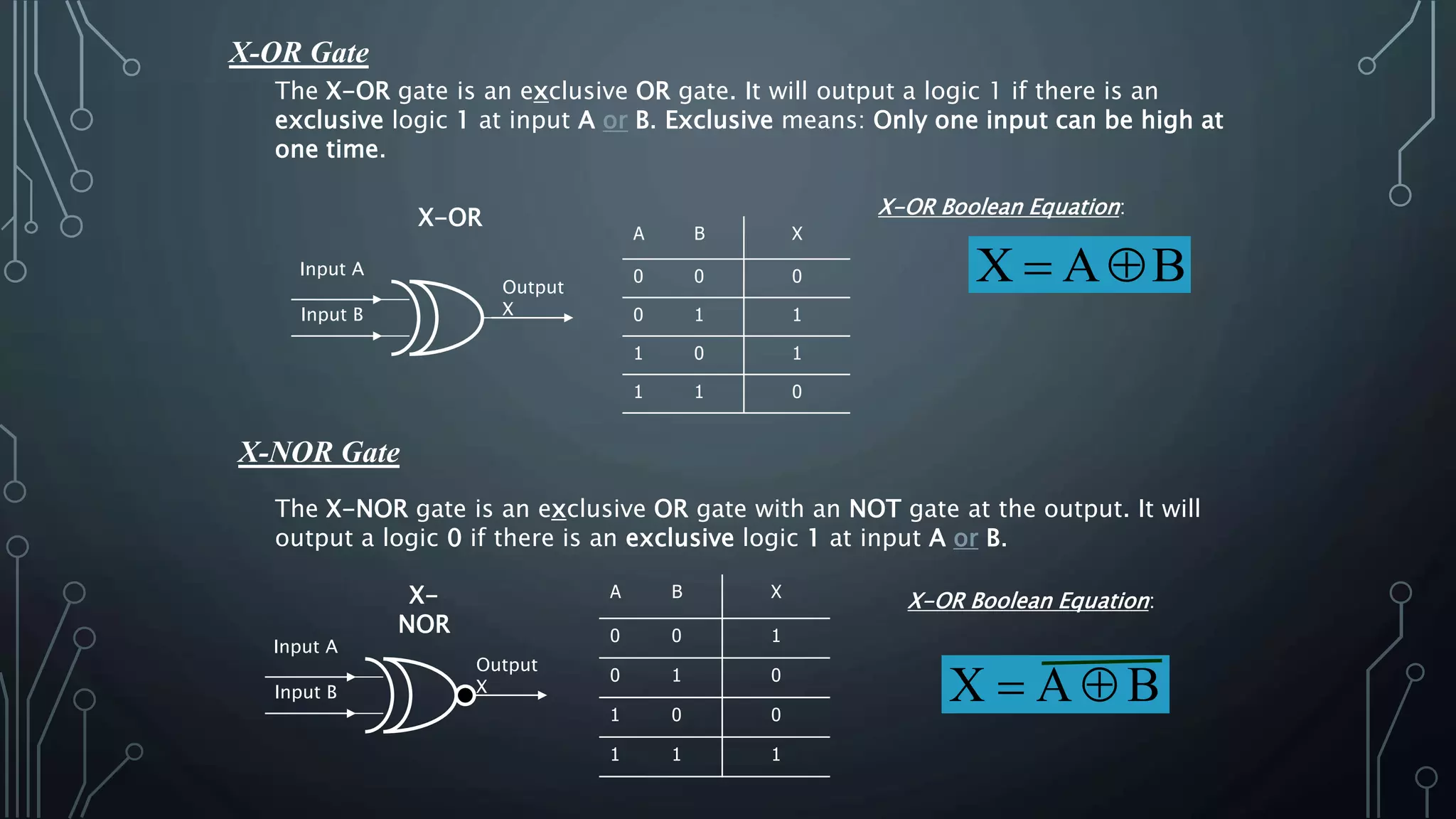

The document provides an overview of logic gates, which are fundamental components in digital circuits that implement logical operations on binary signals. It covers the basic gates such as AND, OR, NOT, as well as their respective truth tables, operational principles, and examples of their configuration using switches and LEDs. Additionally, it discusses other gates like NOR, NAND, XOR, and XNOR, explaining their functions through truth tables and Boolean equations.