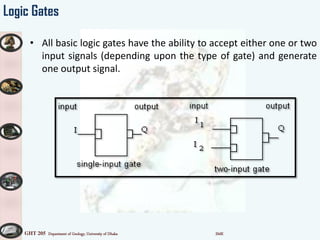

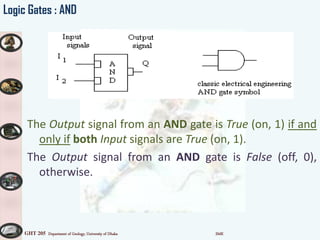

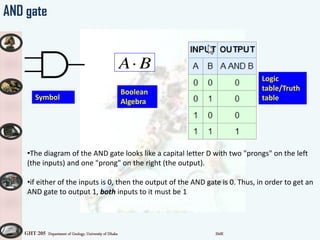

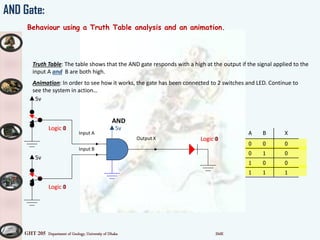

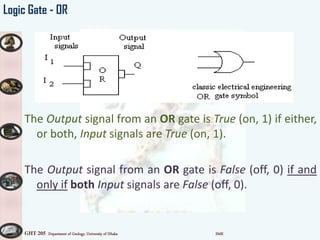

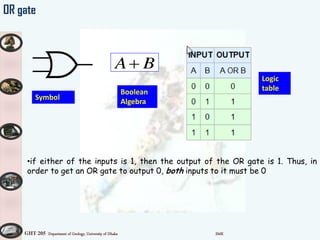

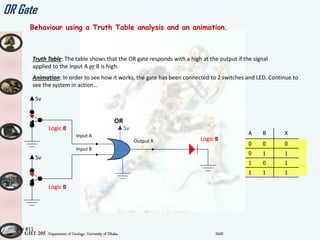

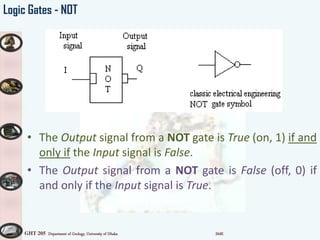

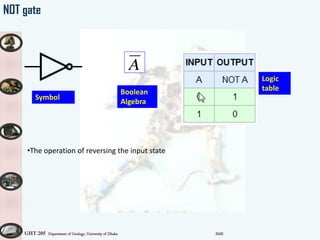

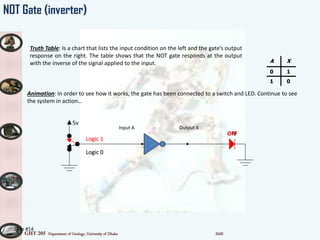

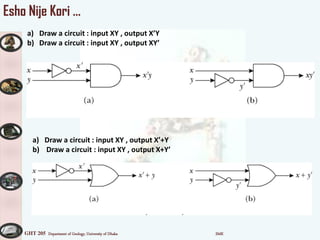

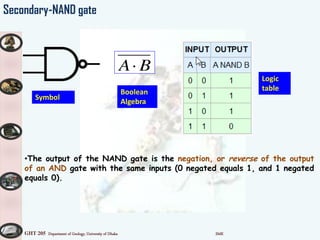

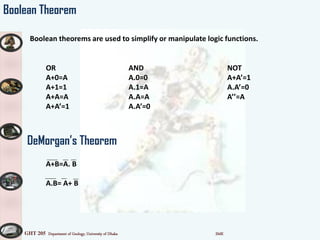

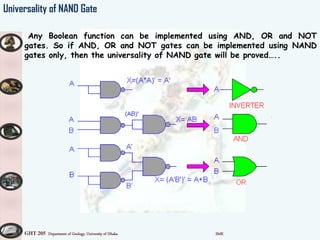

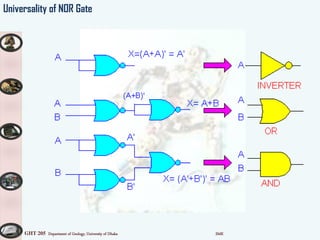

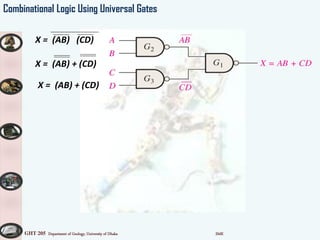

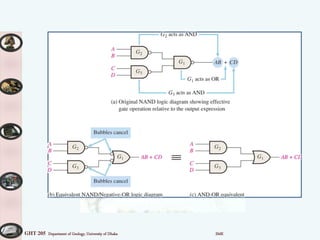

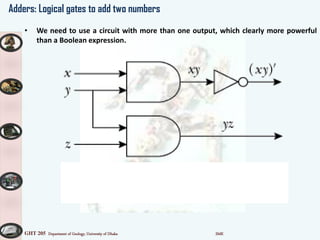

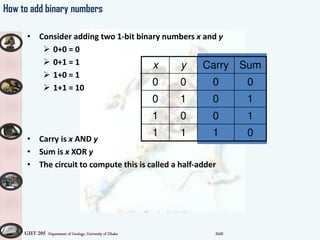

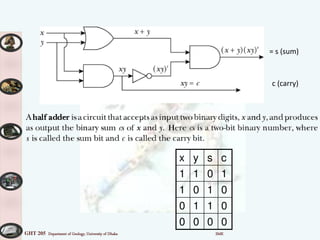

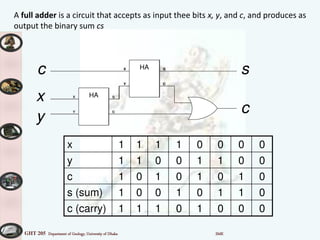

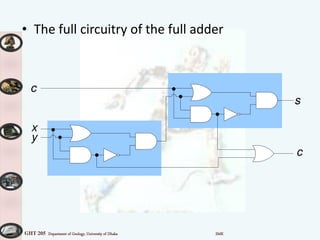

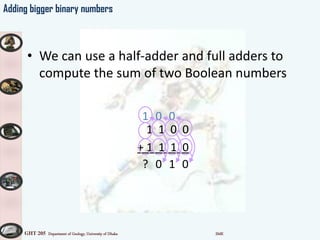

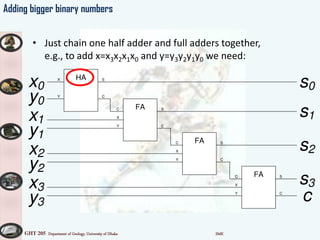

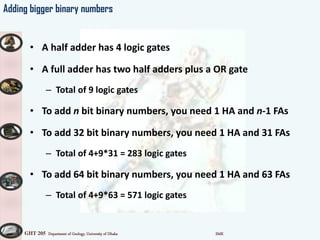

The document discusses digital logic gates and their usage in computers. It describes that logic gates combine electrical pulses following logical rules and are the basic components used to move data and instructions through a computer. The three basic logic gates are AND, OR, and NOT. These gates can be combined to perform more complex logic functions and operations like addition. Adders are constructed using networks of half adders and full adders to add binary numbers.