The document summarizes the evolution of computers from ENIAC to modern multi-core processors. Some key points include:

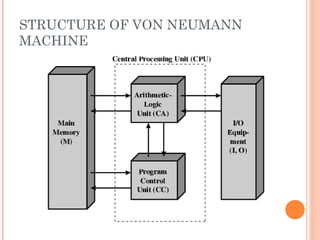

- ENIAC was one of the earliest general-purpose electronic computers built in the 1940s. It led to the development of the stored-program concept by Von Neumann.

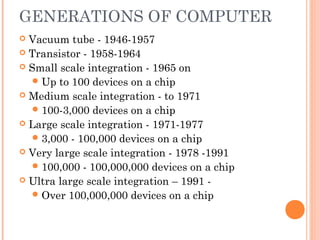

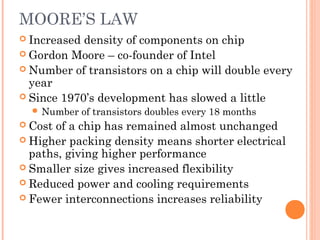

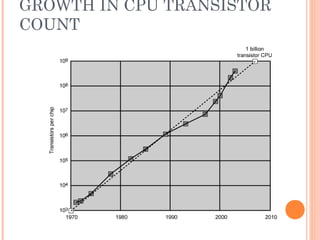

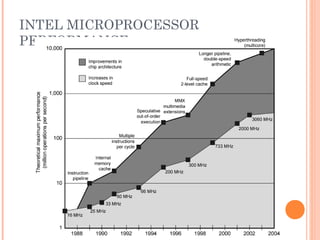

- Advances like transistors, integrated circuits, and microprocessors allowed computers to become smaller, cheaper, and more powerful over time. Moore's Law predicted exponential growth in transistor counts.

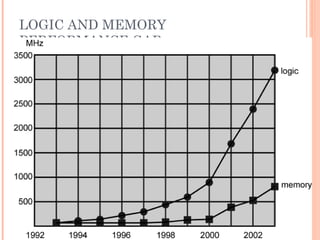

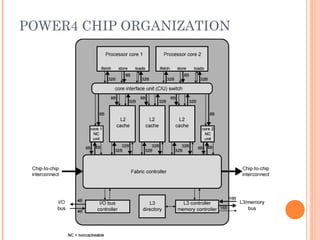

- Modern multi-core CPUs pack multiple processor "cores" onto a single chip to improve performance through parallel processing. Cache size has also increased significantly to bridge the processor-memory speed gap.