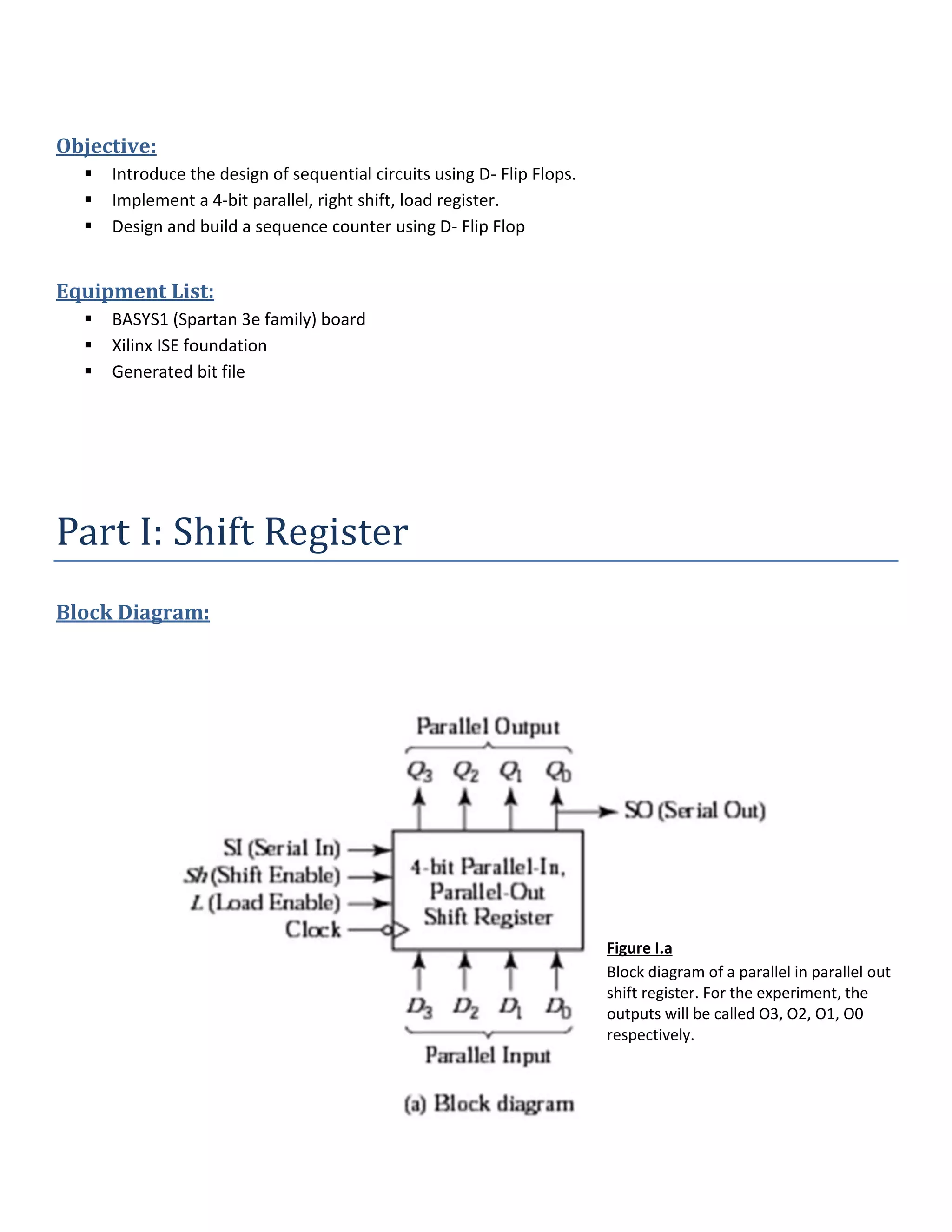

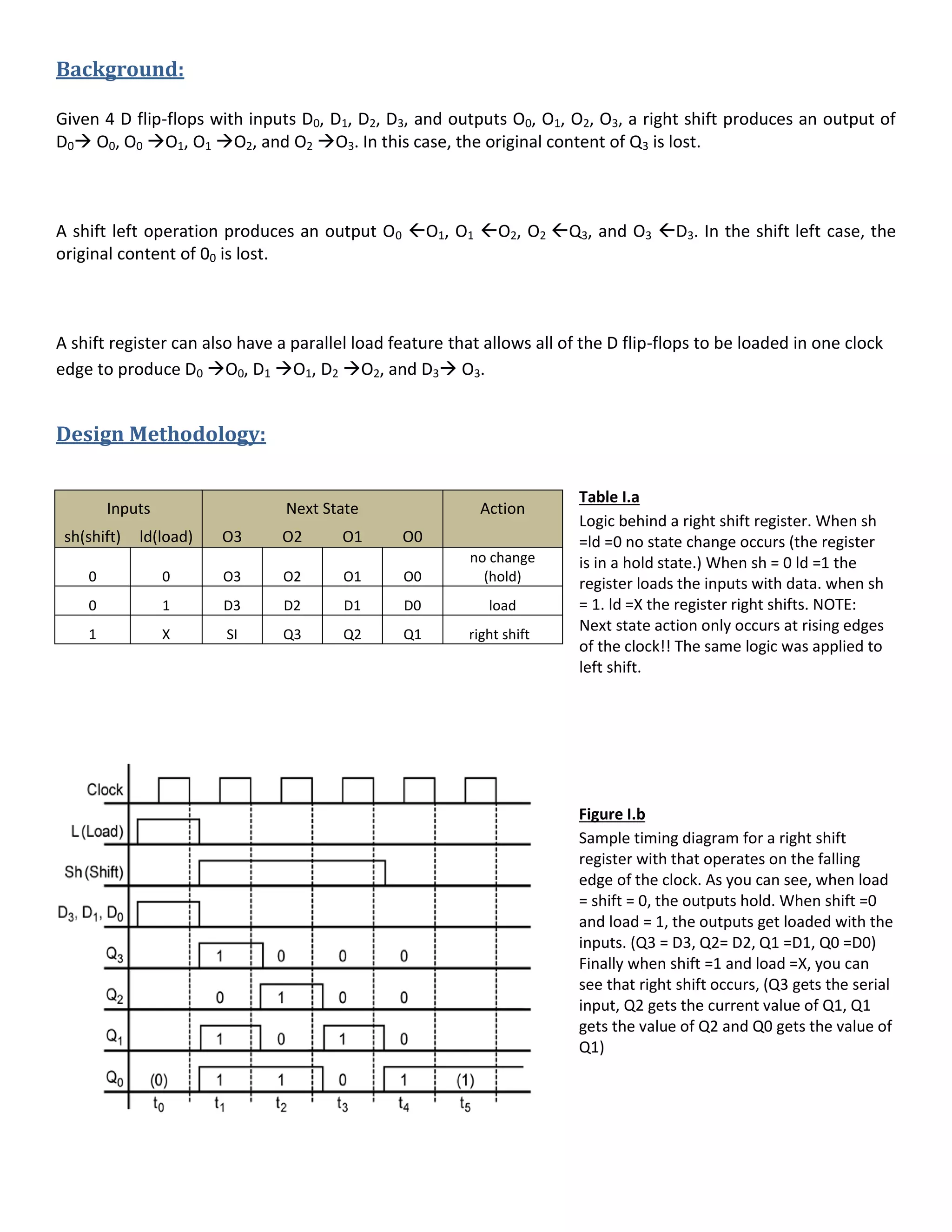

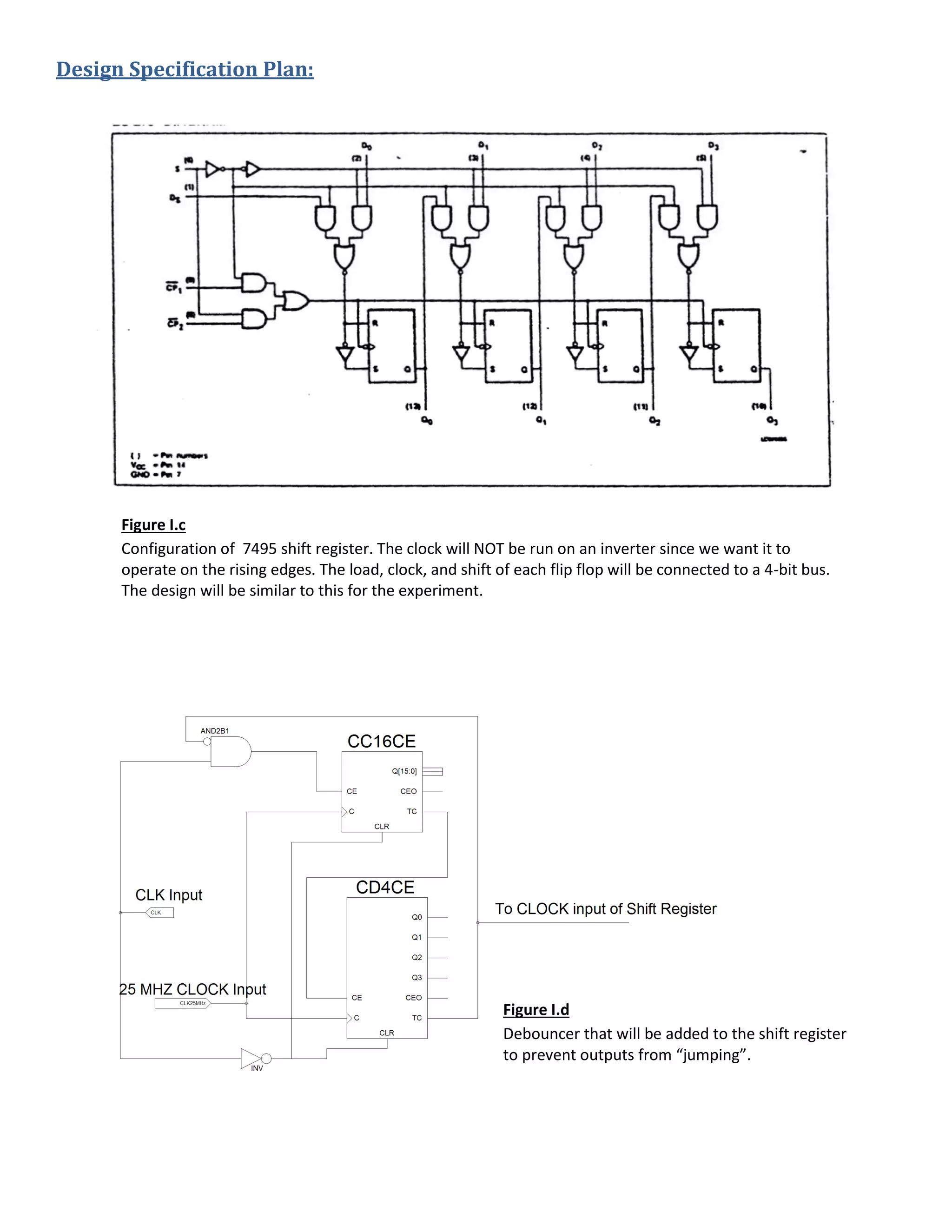

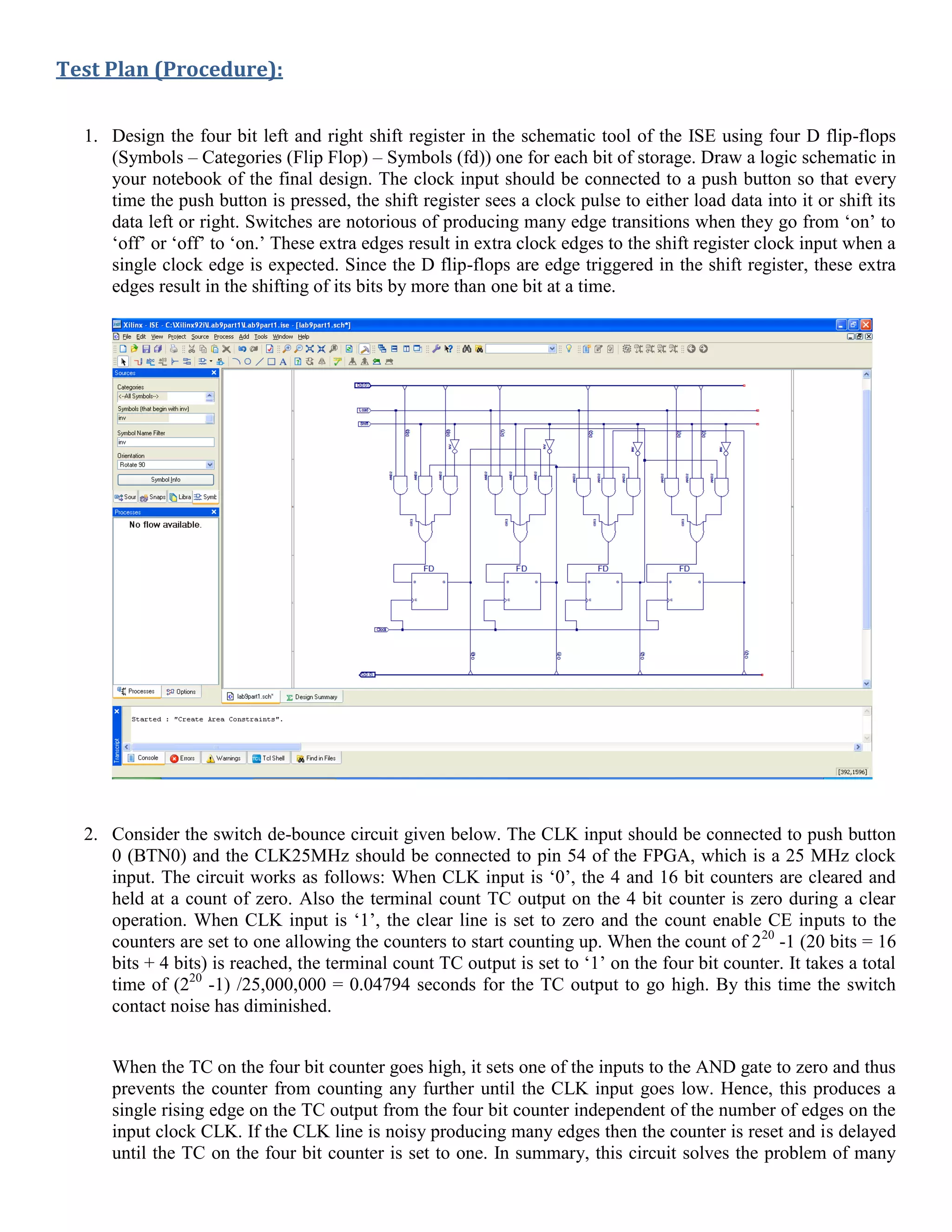

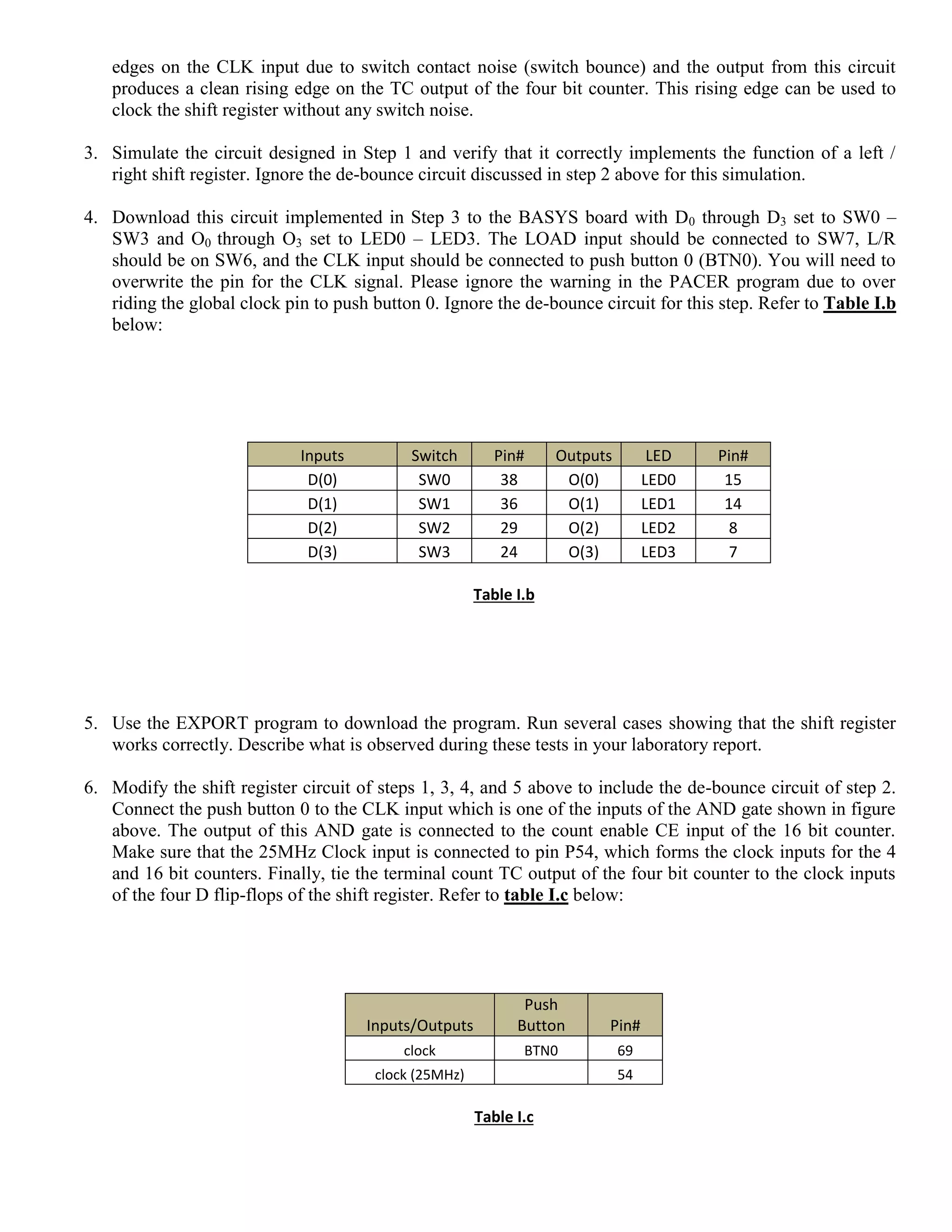

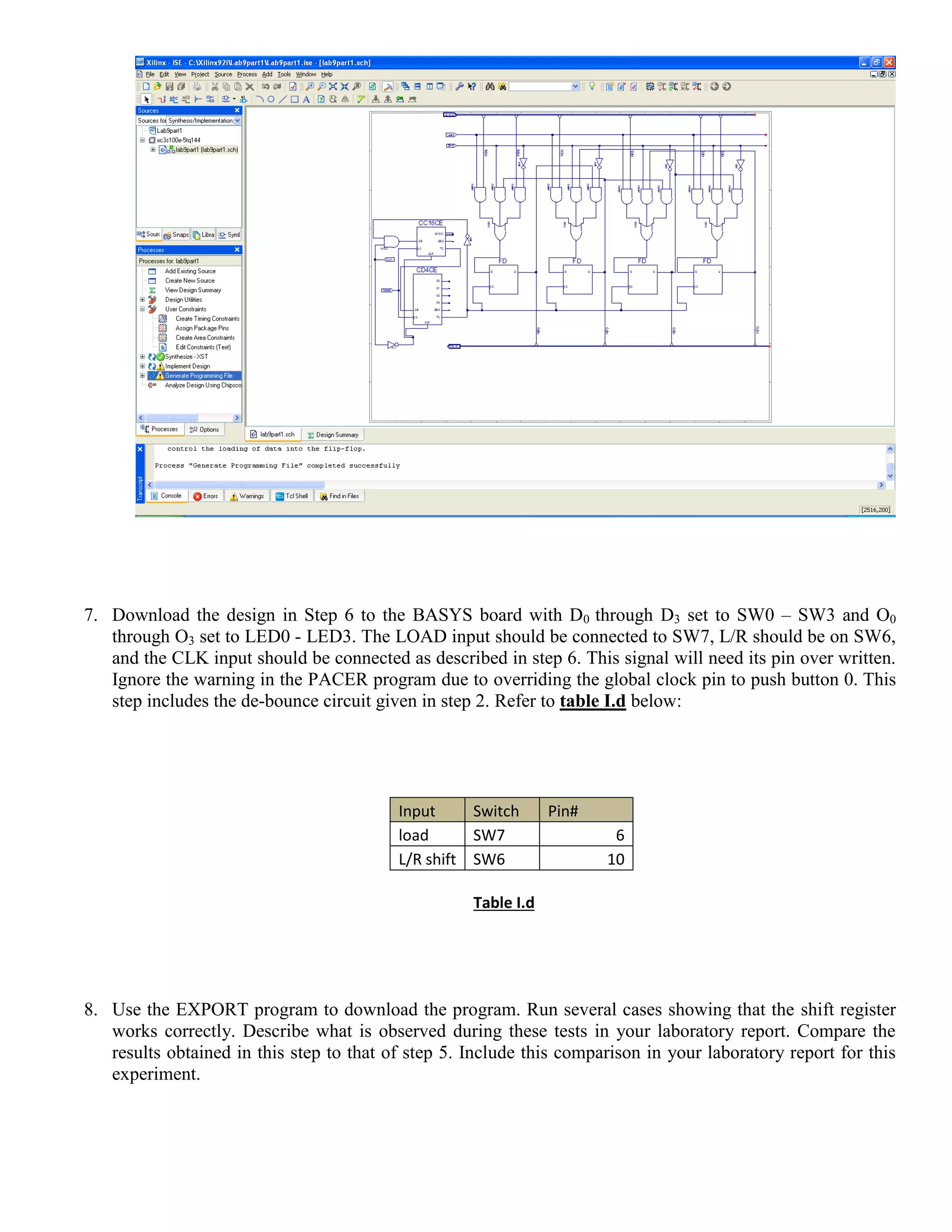

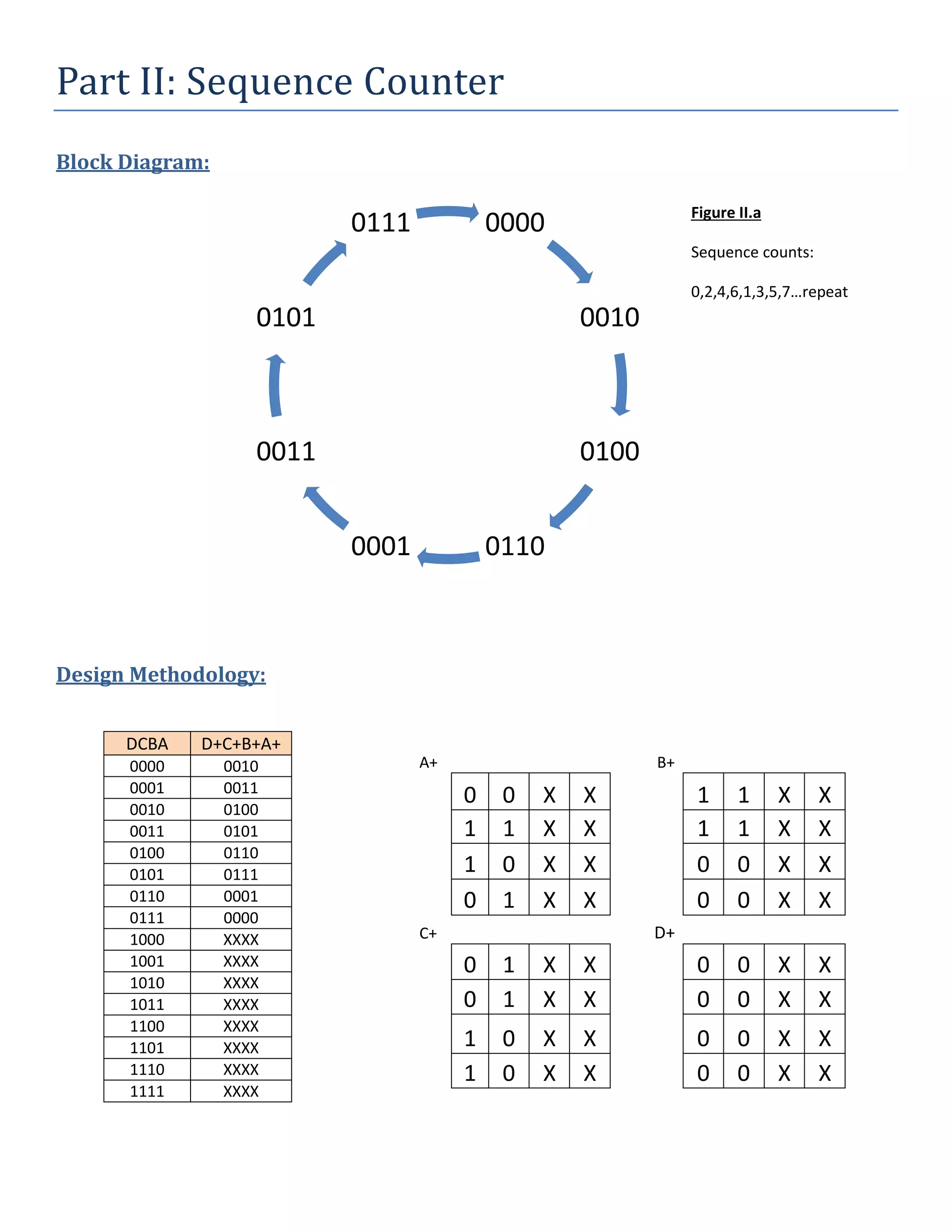

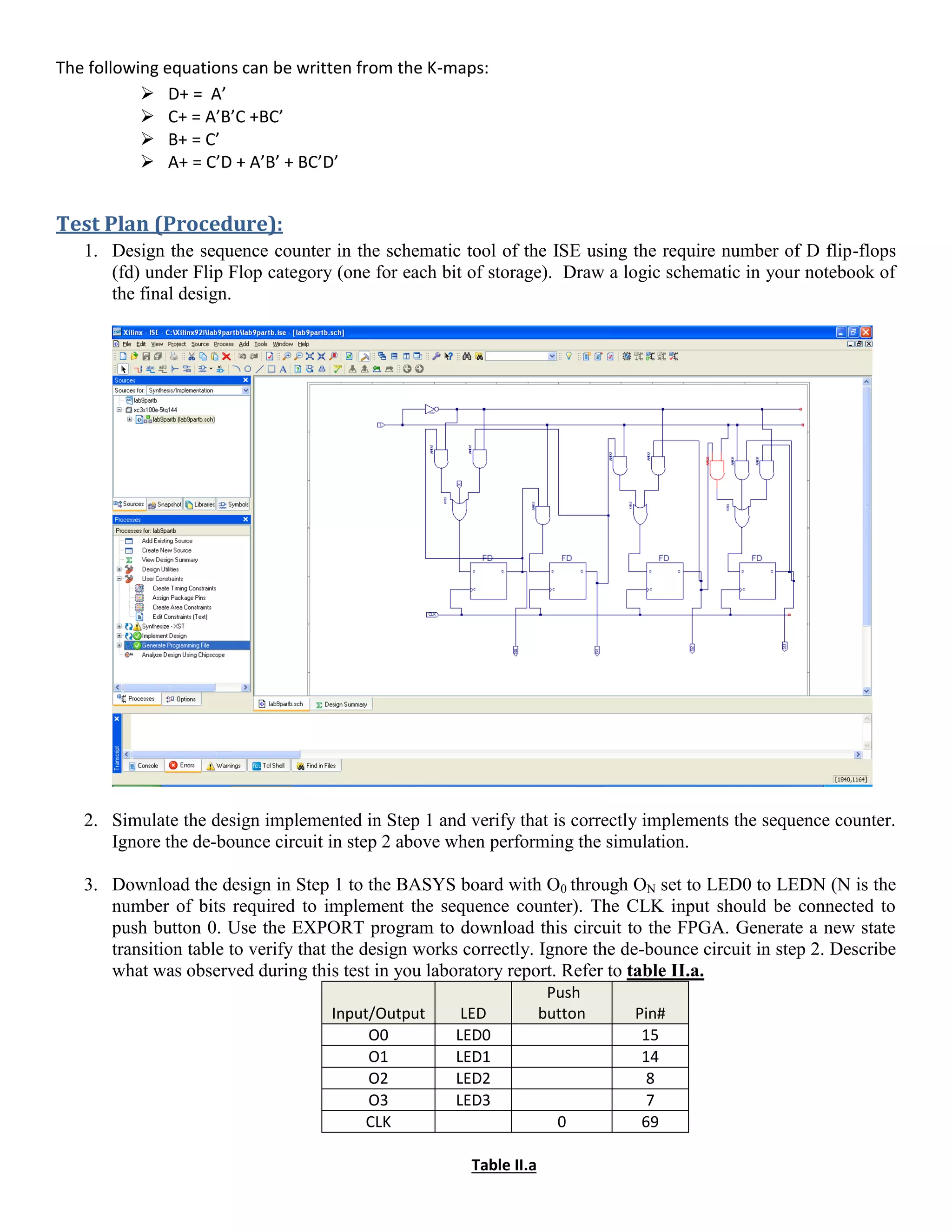

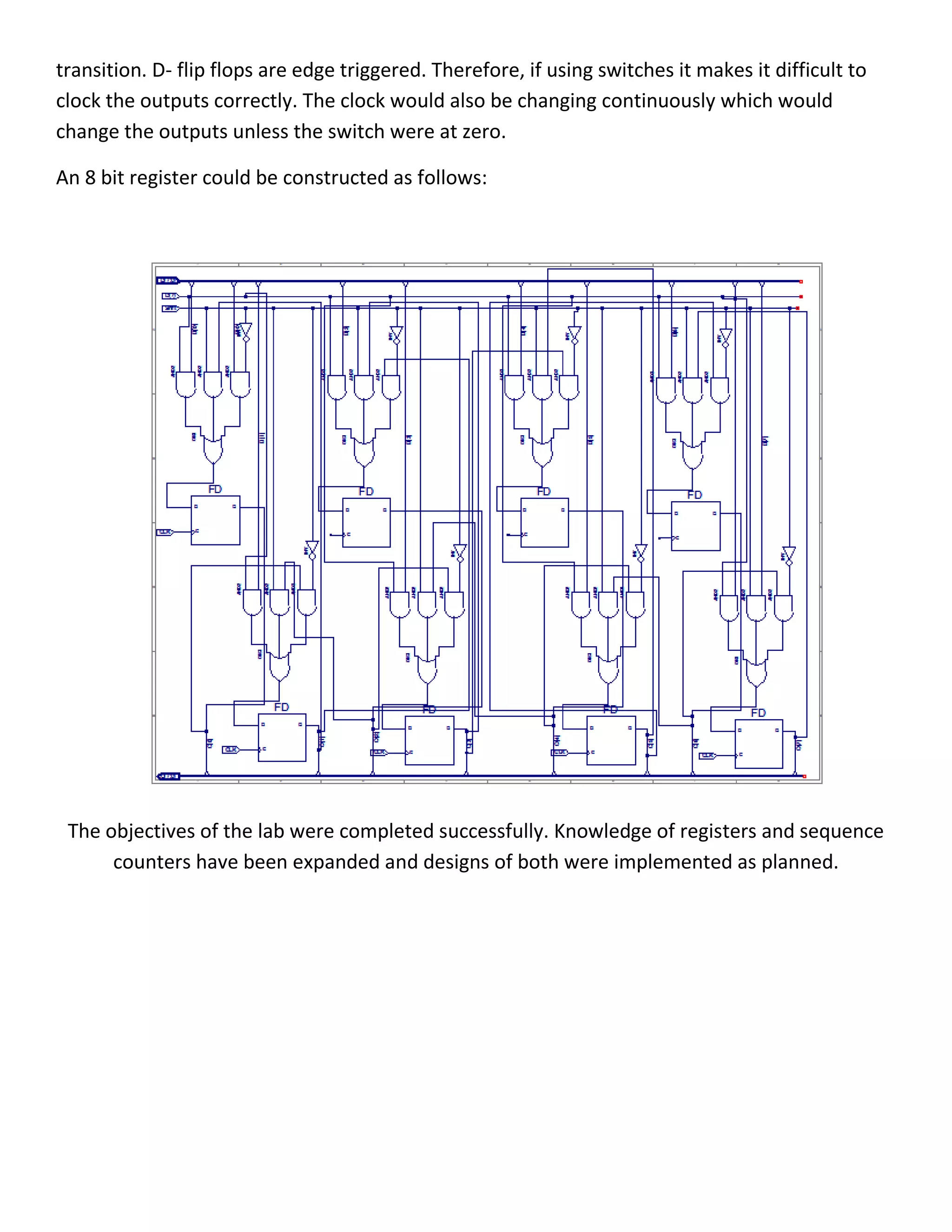

This document describes an experiment involving designing a 4-bit shift register and sequence counter using D-flip flops. It includes building the circuits in an FPGA tool, simulating their operation, and downloading them to a development board. A debouncing circuit is added to prevent erroneous output from noisy button inputs. The objectives of introducing sequential circuit design and implementing a shift register and sequence counter are met.