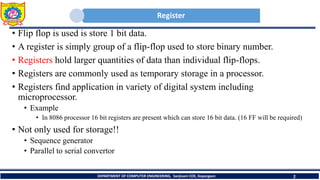

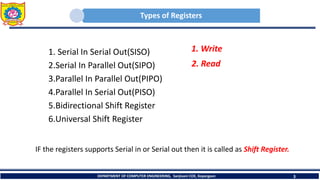

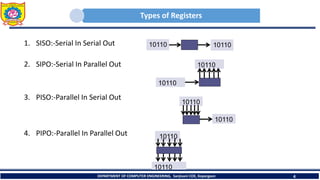

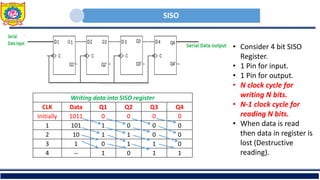

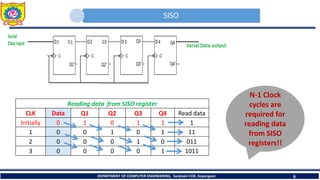

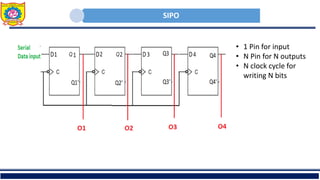

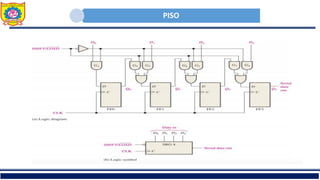

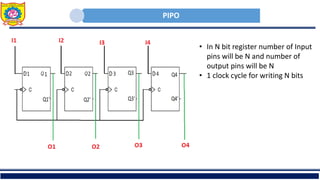

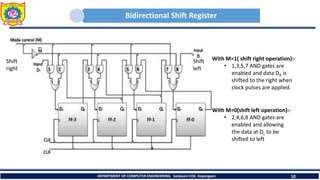

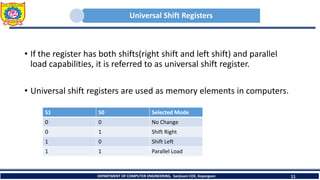

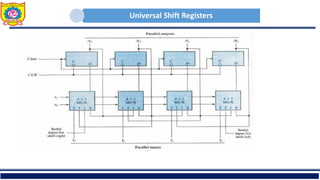

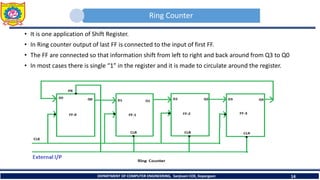

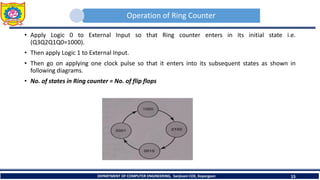

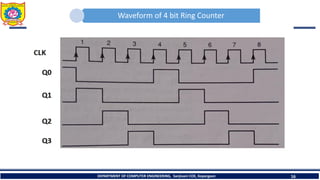

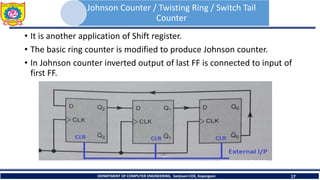

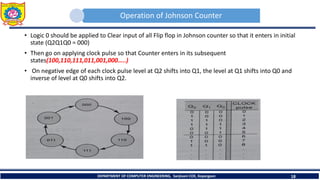

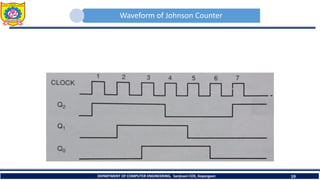

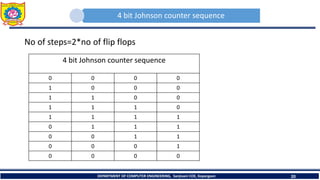

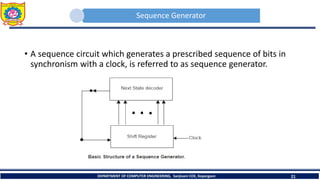

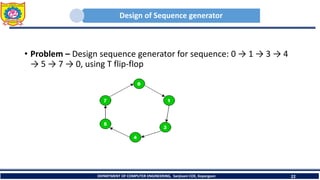

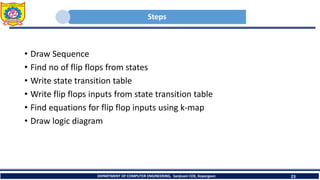

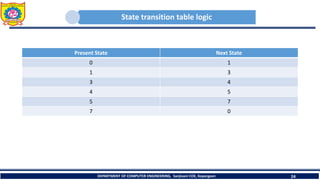

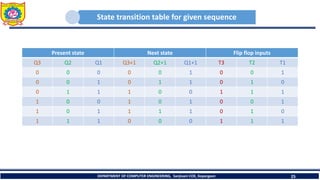

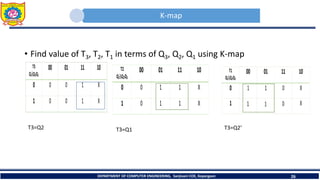

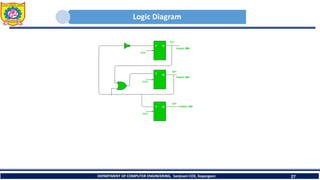

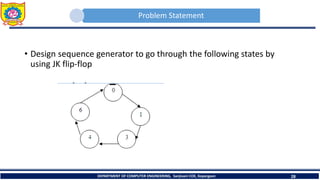

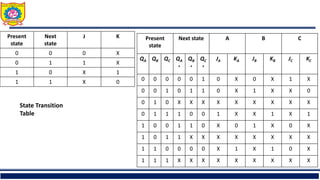

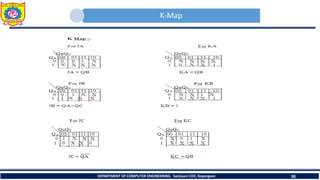

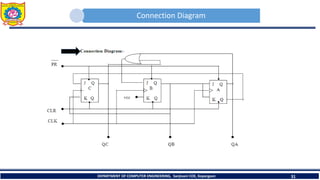

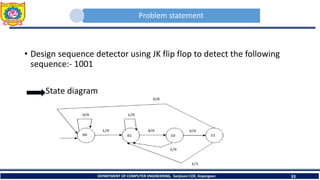

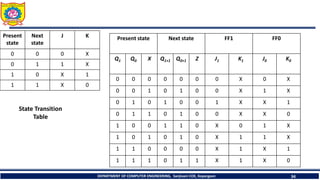

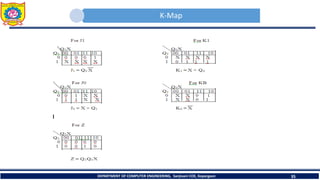

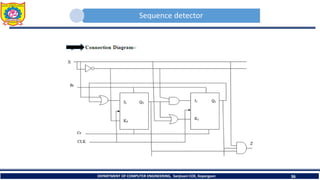

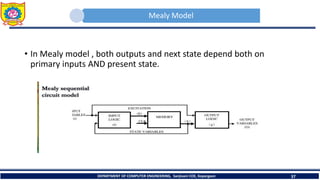

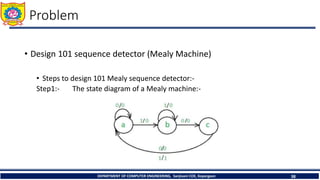

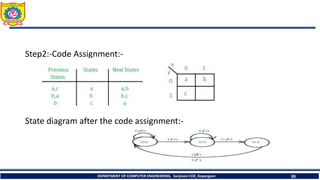

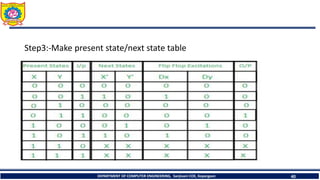

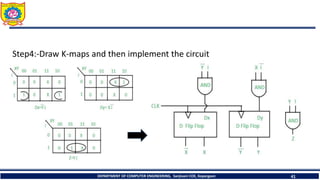

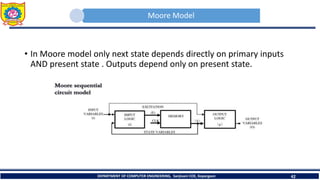

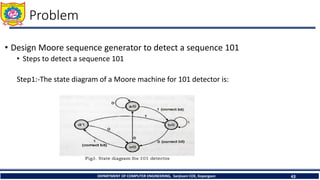

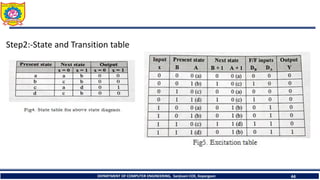

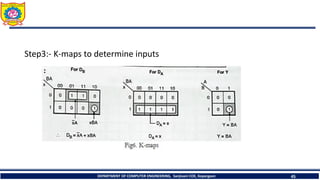

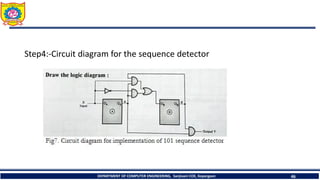

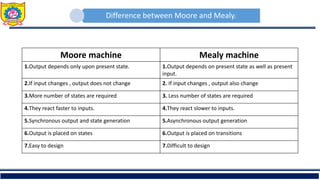

This document discusses sequential circuit design using registers and shift registers. It begins by defining different types of registers including serial in serial out (SISO), serial in parallel out (SIPO), parallel in parallel out (PIPO), and parallel in serial out (PISO) registers. It then provides examples of writing to and reading from a SISO register. Applications of shift registers like sequence generators, sequence detectors, and parallel to serial converters are also covered. Specific sequential circuits like ring counters, Johnson counters, and sequence generators using JK flip-flops are designed and their operation is explained through state tables and diagrams. Finally, the differences between Mealy and Moore models for sequential circuit design are summarized.