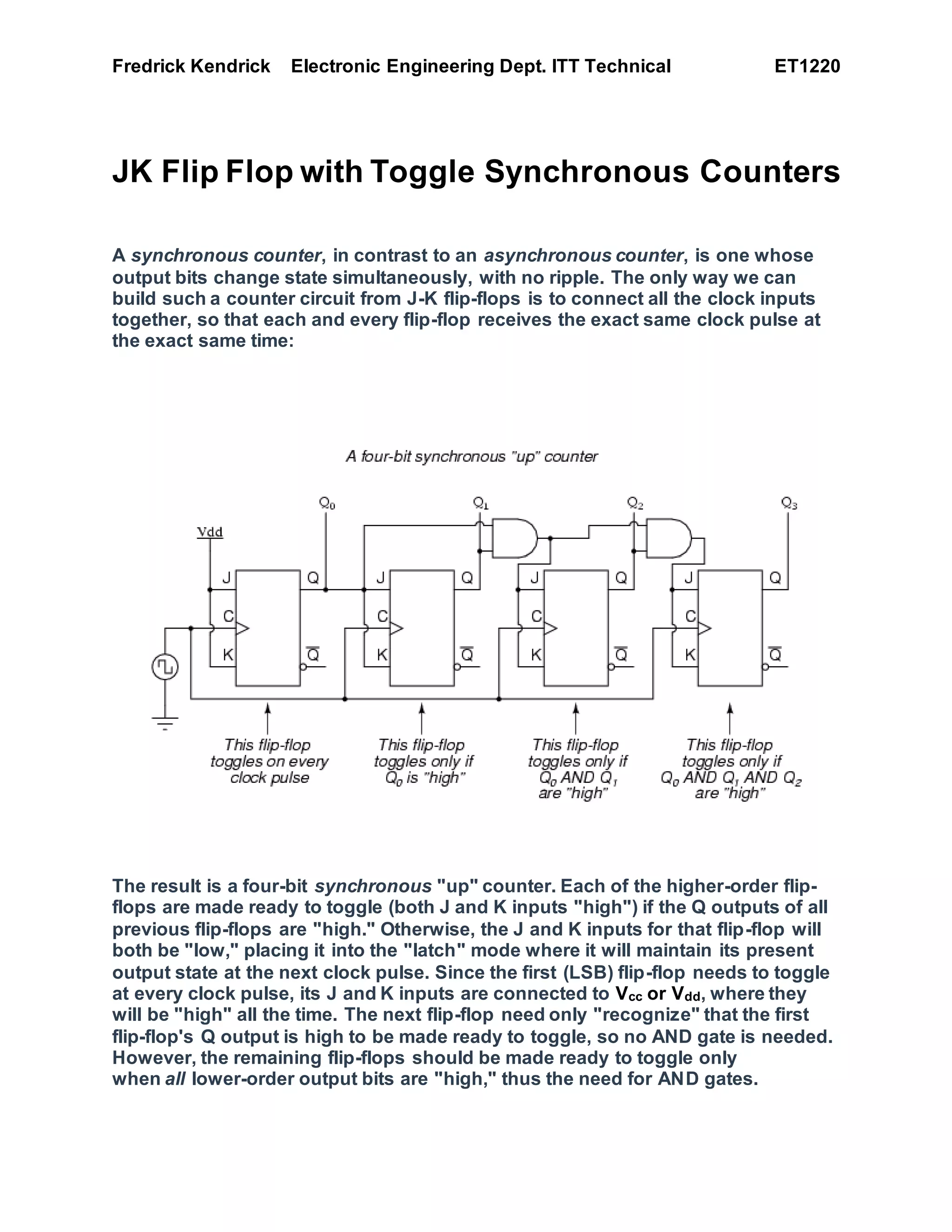

This document discusses the design and operation of a 4-bit synchronous up/down counter using JK flip-flops. It explains that in a synchronous counter, all output bits change state simultaneously in response to a clock signal. The circuit connects all flip-flop clock inputs together. For an up counter, the J and K inputs of each flip-flop are configured to toggle the flip-flop when the outputs of all previous flip-flops are high. For a down counter, the circuit recognizes bit patterns where preceding bits are low before a toggle by using the Q' outputs of each flip-flop. The least significant bit toggles on every clock cycle while more significant bits toggle less frequently in a divide