Rangkuman dokumen tersebut adalah:

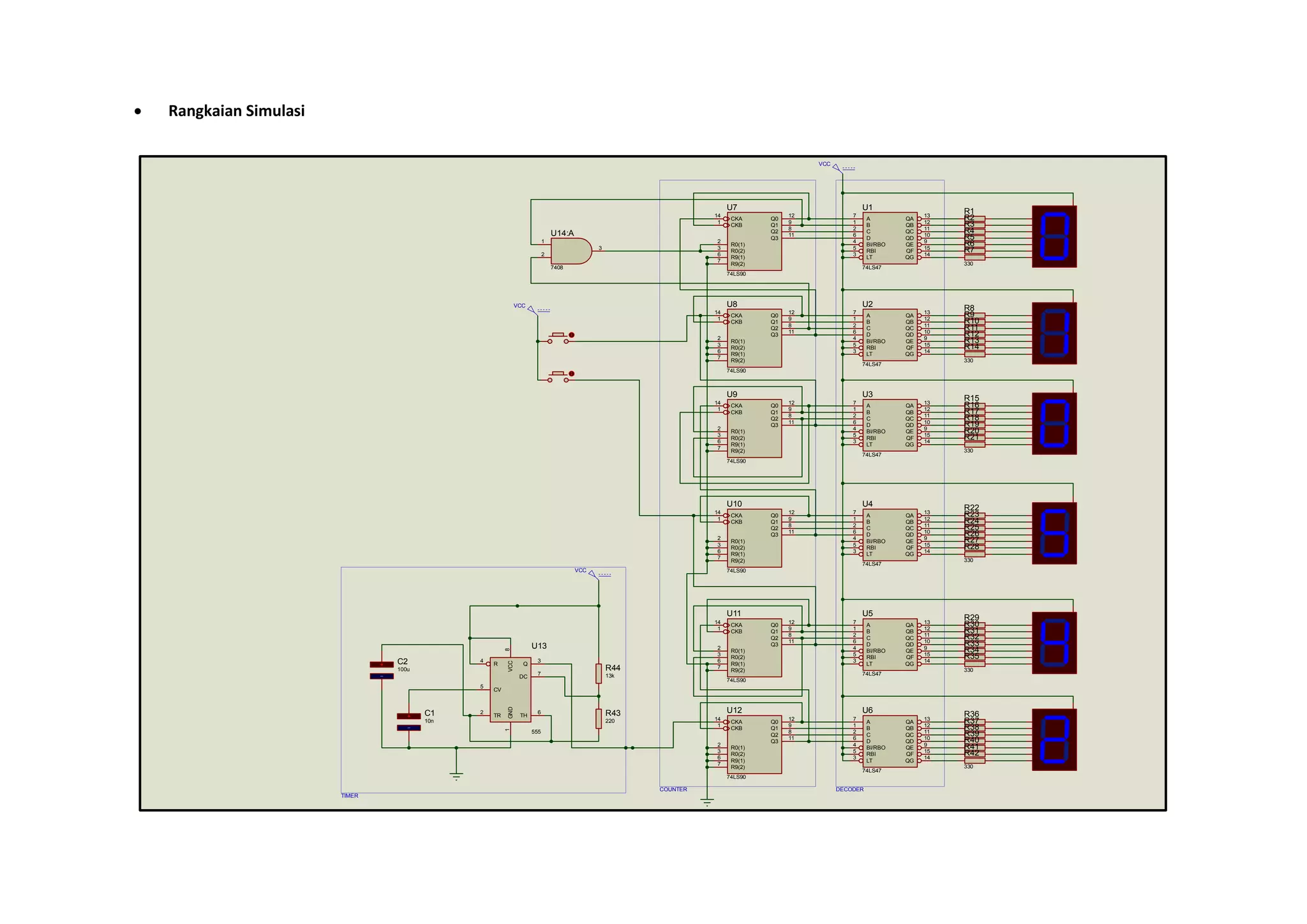

1. Laporan proyek akhir mengenai implementasi rangkaian counter pada jam digital untuk mengaplikasikan timer, counter, dan decoder BCD ke seven segment.

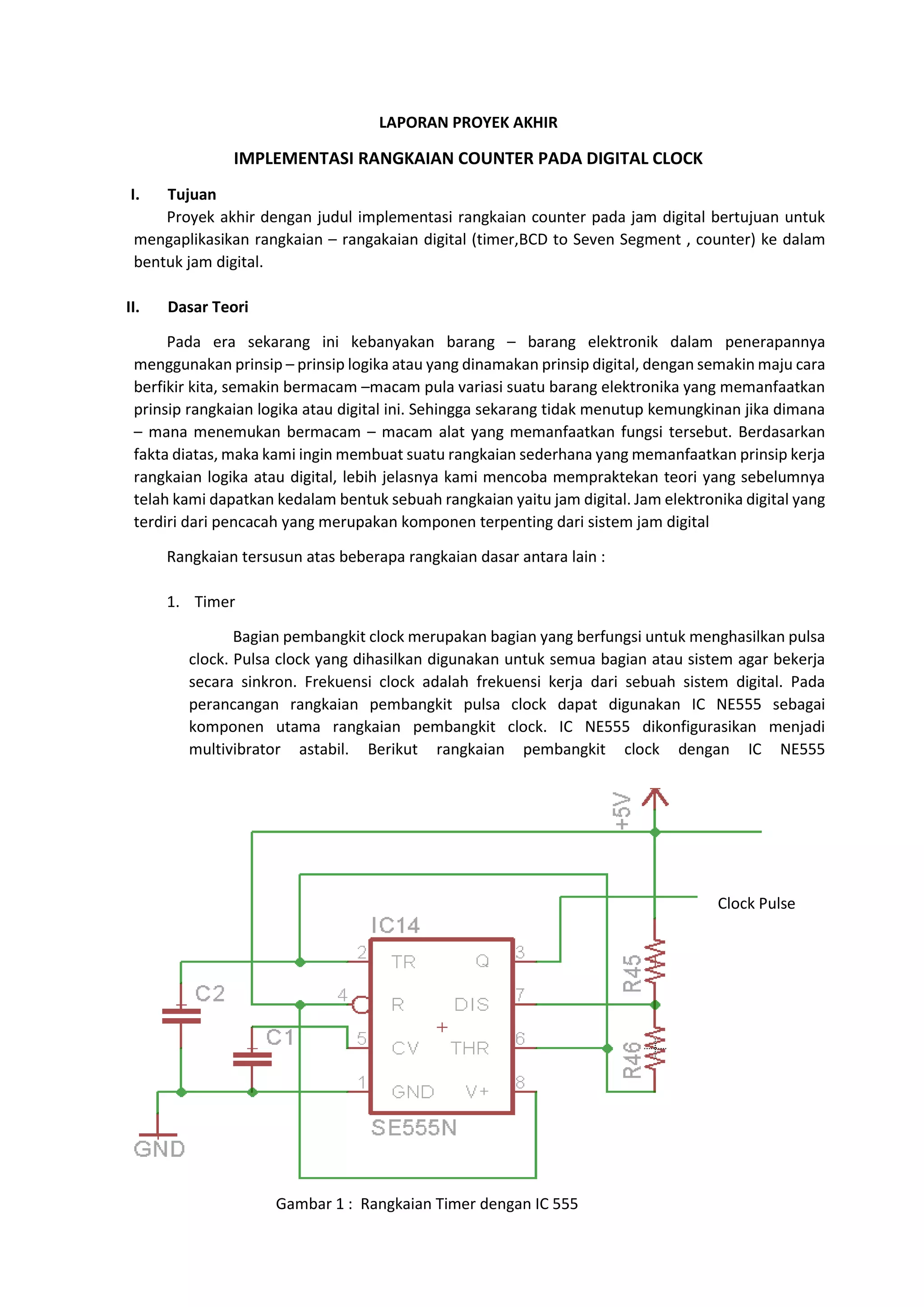

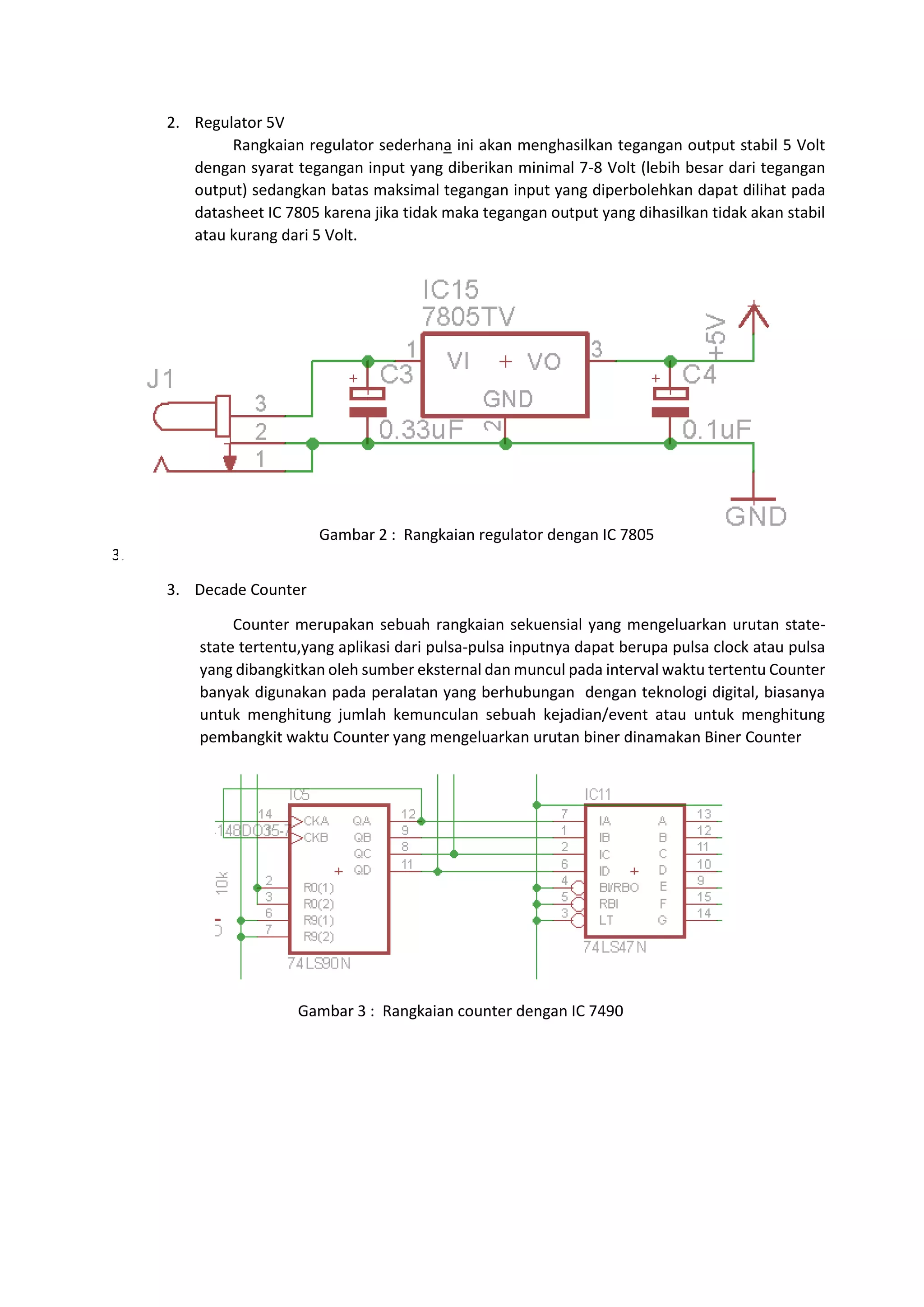

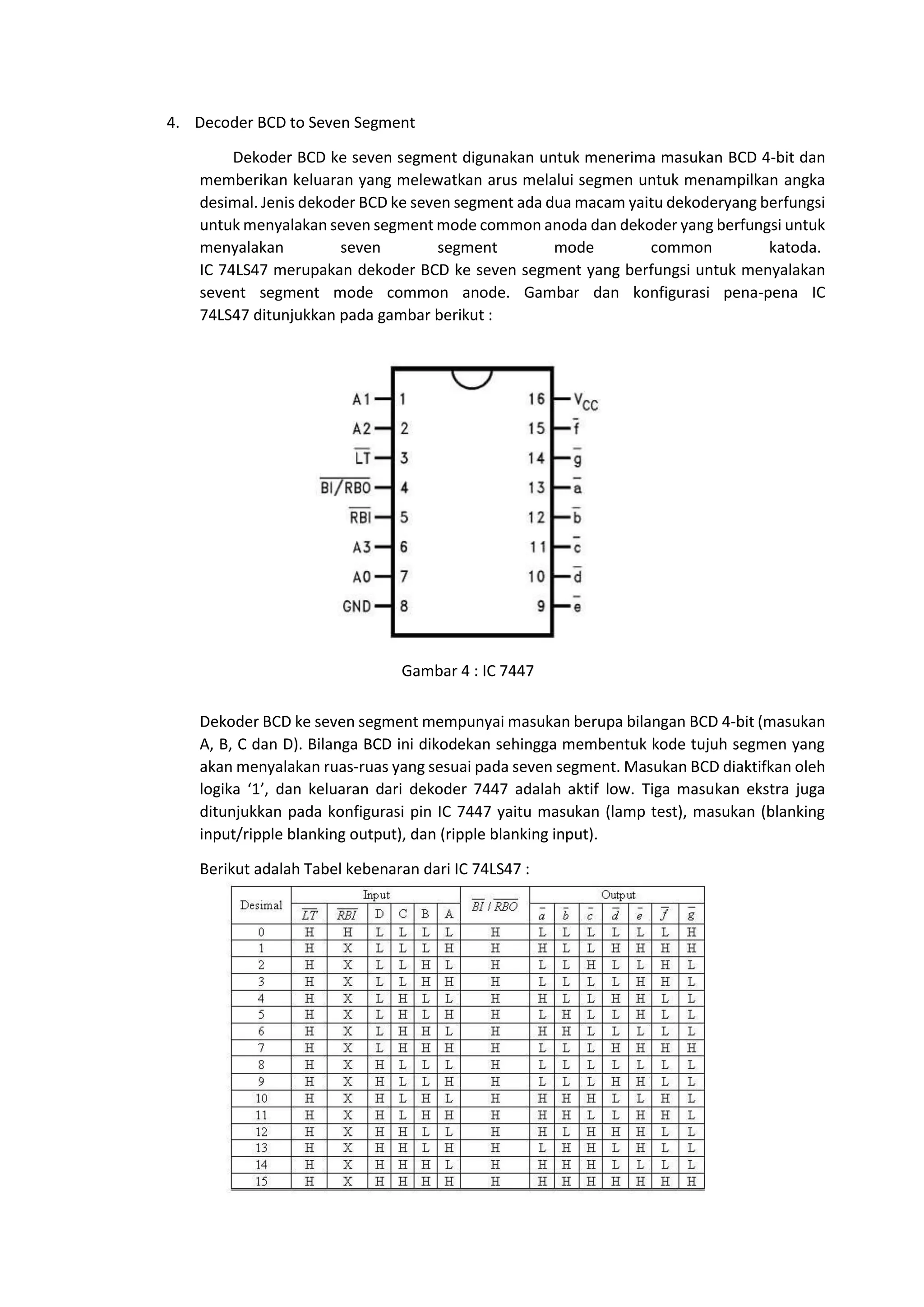

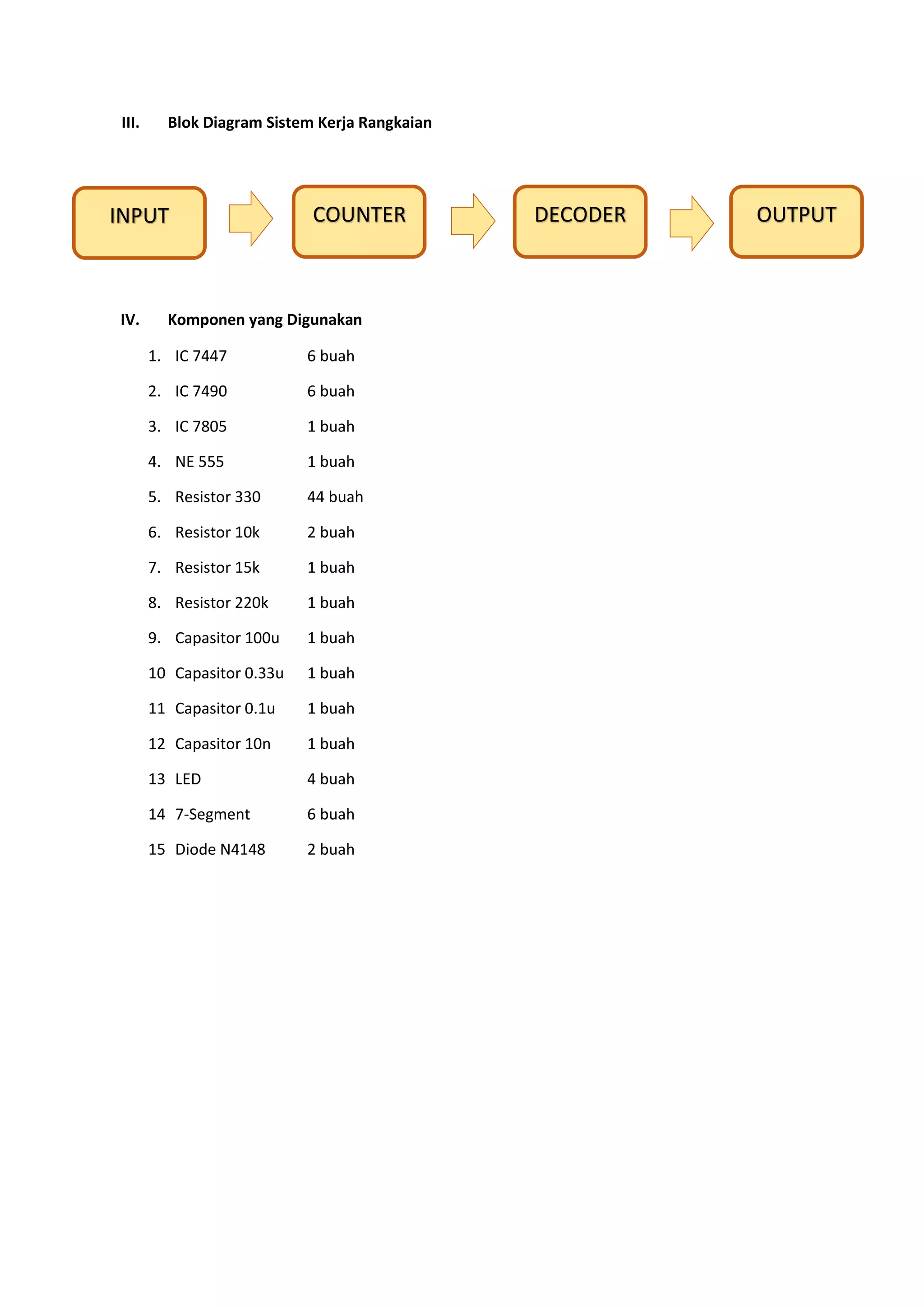

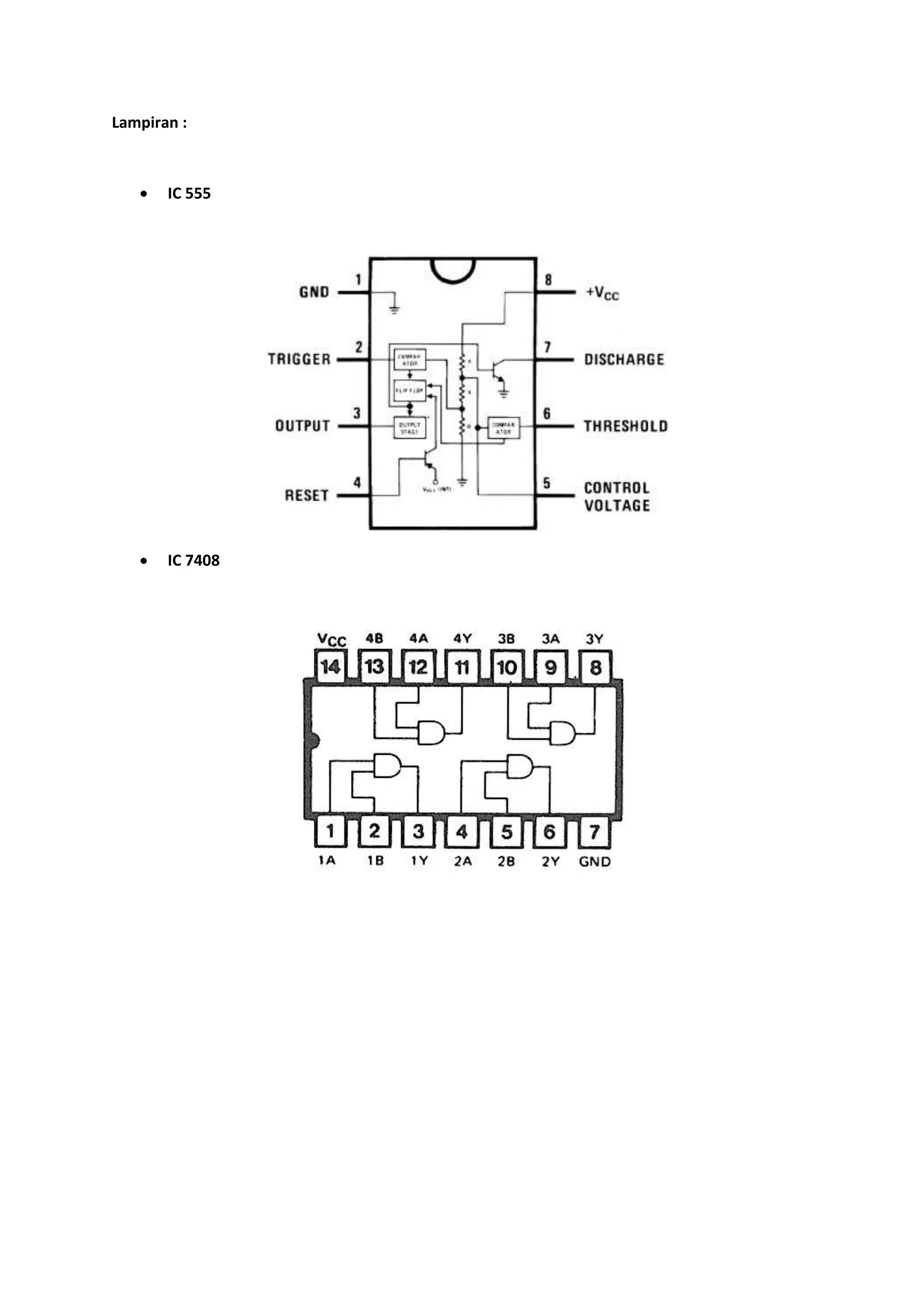

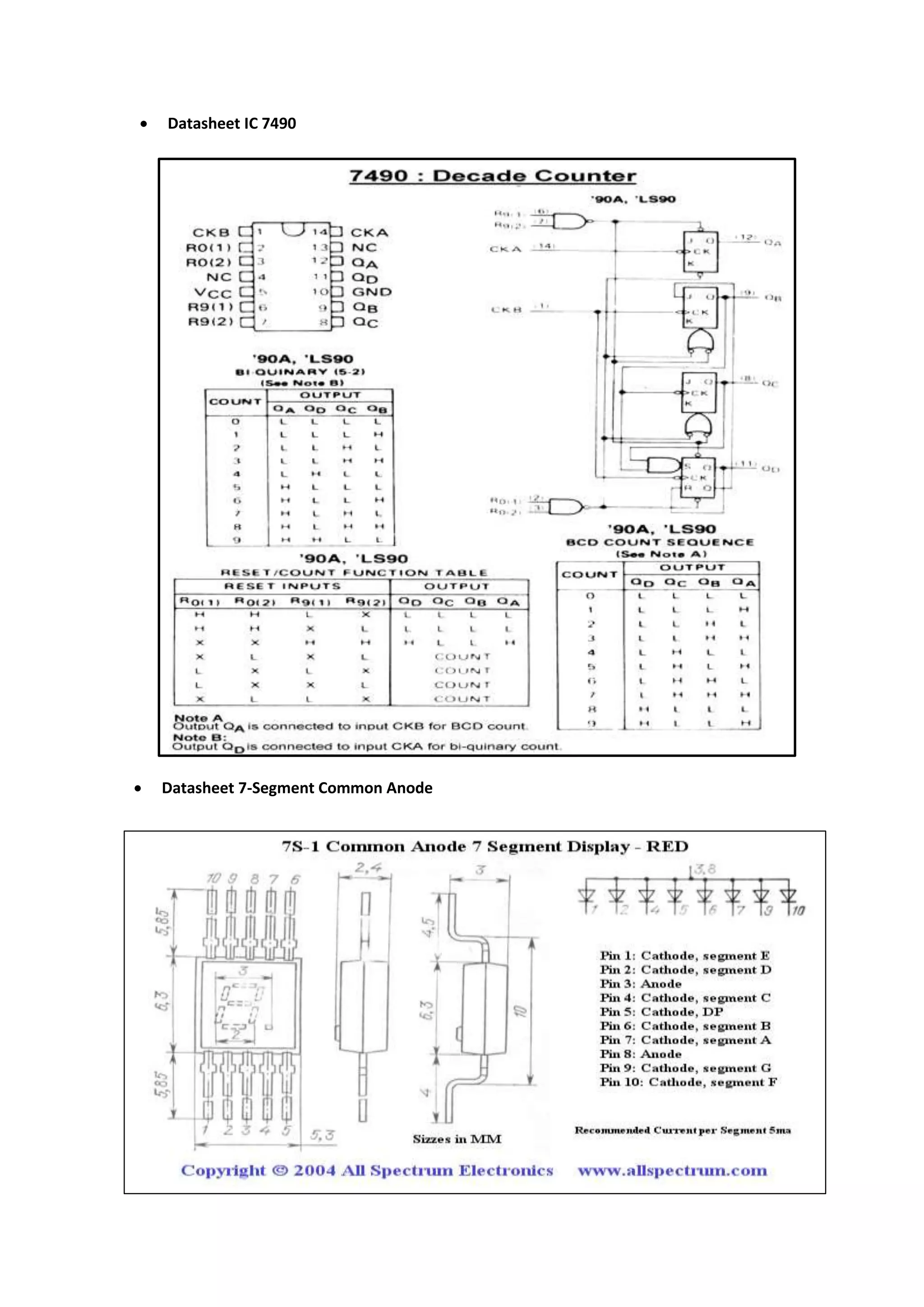

2. Rangkaian terdiri dari timer, regulator, counter decade, dan decoder yang digunakan untuk menampilkan waktu pada jam digital.