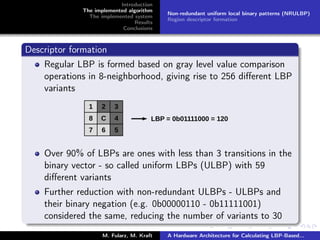

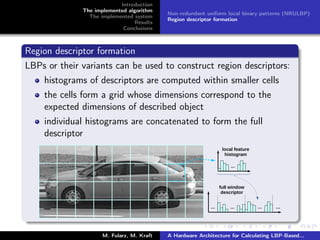

The document presents a hardware architecture designed for efficiently computing LBP-based image region descriptors, utilizing non-redundant uniform local binary patterns (NRULBP). It details the system's architecture, processing performance, and resource utilization, achieving significant processing speeds for various image resolutions while maintaining low power consumption. Future work aims to integrate this architecture with coprocessors for enhanced classification tasks.

![Introduction

The implemented algorithm

The implemented system

Results

Conclusions

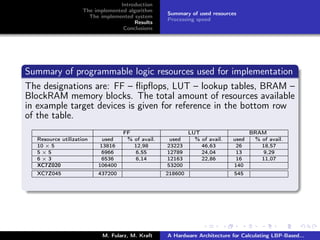

Summary of used resources

Processing speed

Processing speed

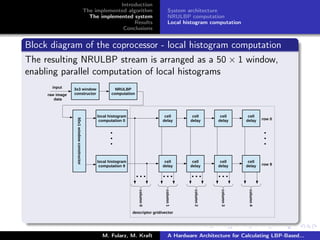

Tests were performed using a 10 × 5 grid of 5 × 5 cells on all image

pixels. The power consumption is well below 3W. Clock frequency

is 75MHz.

Number of frames per second that the proposed hardware

accelerator can process for different image sizes:

resolution processing time [ms] frames per second

640 x 480 3,84 260,4

1280 x 720 11,52 86,8

1920 x 1080 25,92 38,6

PC implementation achieves 1,5 FPS on VGA resolution images.

M. Fularz, M. Kraft A Hardware Architecture for Calculating LBP-Based...](https://image.slidesharecdn.com/hardware-architecture-calculating3-150527102021-lva1-app6892/85/Hardware-Architecture-for-Calculating-LBP-Based-Image-Region-Descriptors-15-320.jpg)