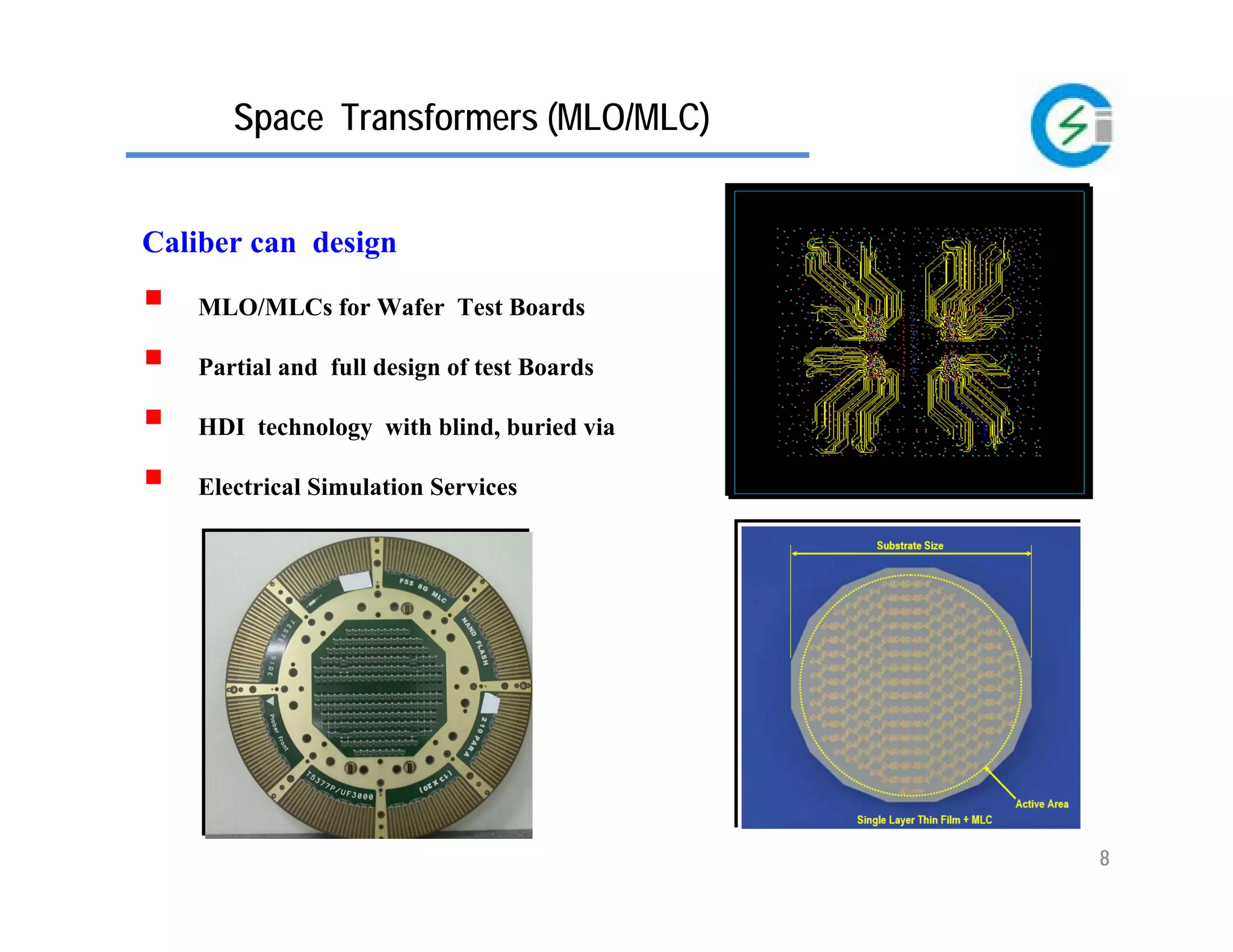

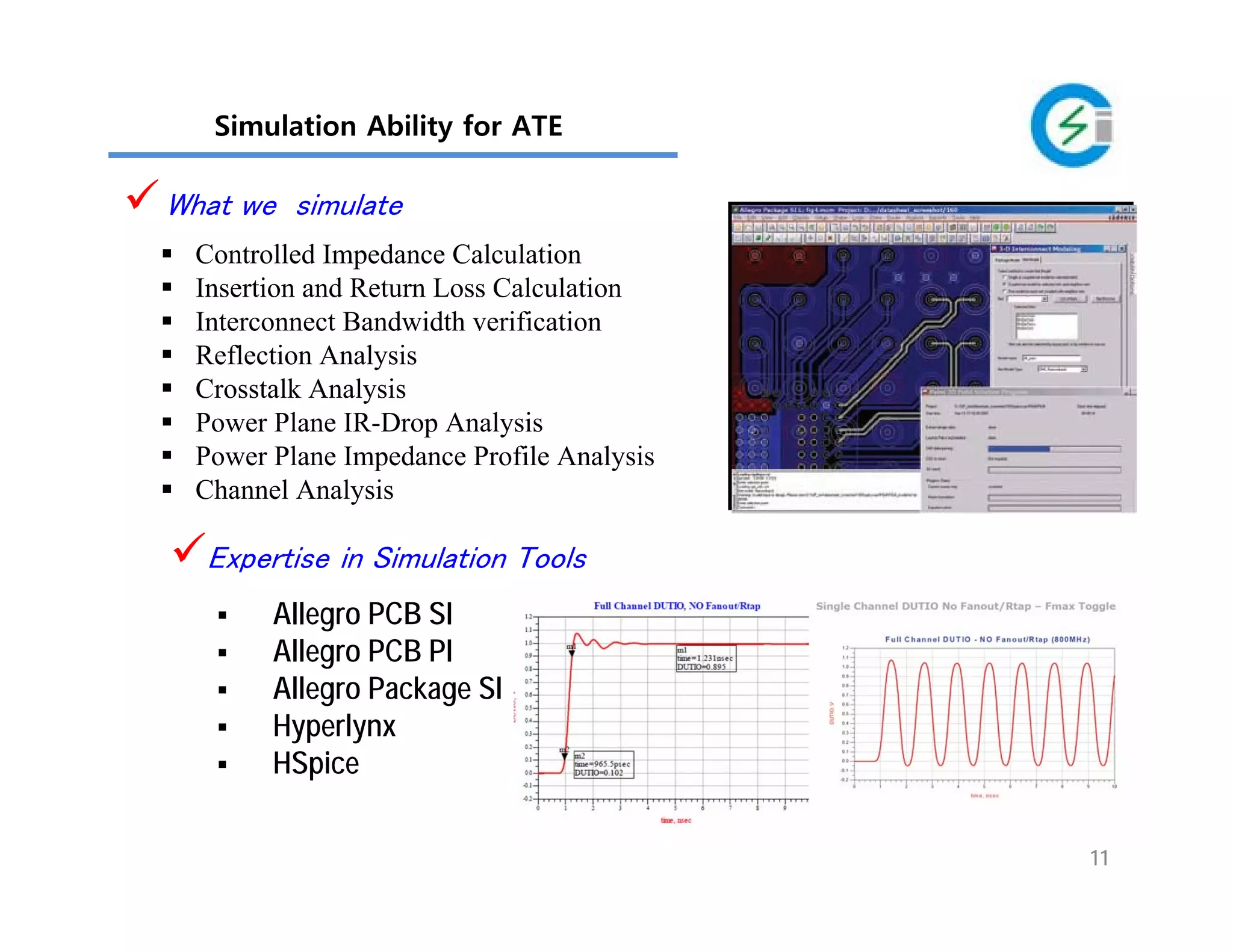

Caliber Interconnect Solutions is a design firm specializing in advanced hardware design, routing, and signal integrity analysis services primarily for automated test equipment (ATE) vendors. Established in 2000 and ISO 9001:2000 certified, the company offers expertise in developing various test interface boards and ATE systems, ensuring high-quality design solutions through experienced designers and extensive engineering capabilities. With a history of innovation and a commitment to customer satisfaction, Caliber has serviced over 6000 ATE interface boards and built a solid reputation in the industry.