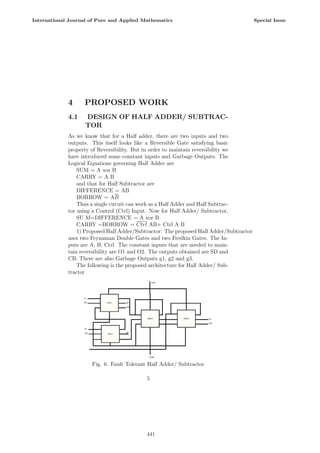

The document presents a new architecture for a full adder/subtractor using reversible logic, which aims to minimize constant inputs and garbage outputs compared to existing designs. It discusses the importance of reversible logic in modern applications such as quantum computing and emphasizes the benefits of its implementation in digital circuits. The proposed design incorporates half adder/subtractor configurations and specific reversible gates to ensure efficiency and maintain reversibility.

![1 Introduction

According to Landaurer [1], KTln2 Joules of heat energy is pro-

duced for every bit of information lost during irreversible computa-

tion, where K is Boltzmann constant and T is absolute temperature.

For room temperature T the amount of dissipating heat is small (i.e.

2.9X10-21 J ), but not negligible. This amount may not seem to be

significant, but it will become relevant in the future. This energy

dissipation would not occur during reversible computation as there

is no loss of information

[2]. Reversible circuits always maintain one-to-one mapping be-

tween the inputs and the outputs, and is performed by reversible

logic gates. There are outputs in reversible circuits which are nei-

ther used in the further stages of computation nor restore any orig-

inal inputs. These redundant outputs are called garbage outputs.

There are constant inputs (0 or 1) which are used in reversible

quantum circuits for storing intermediate values during computa-

tion. Reversible circuits are designed using reversible logic gates

such as Fredkin, Toffoli, Feynman, Peres etc. Reversible logic has

wide variety of applications in the field of emerging technologies

such as quantum computers, optical computing, Cellular automata,

ultra- low power VLSI

[3].

This paper is organized as follows. In Section II, the physi-

cal model of Reversible Logic is described. The concept of Parity

Preserving Reversible Gates is discussed in Section III in order to

validate our model. In Section IV, the design of Half Adder/ Sub-

tractor and Full Adder/ Subtractor is shown. Finally, in Section V,

the conclusion of this paper is given.

Fig. 1. n*n Reversible Logic Gate

2

International Journal of Pure and Applied Mathematics Special Issue

438](https://image.slidesharecdn.com/ijpam-190201050516/85/FULL-ADDER-SUBTRACTOR-USING-REVERSIBLE-LOGIC-2-320.jpg)

![2 REVERSIBLE LOGIC

A Reversible Logic Gate should produce one-to-one map-ping be-

tween Inputs and Outputs, so that reversibility is maintained. That

is Reversible Gate is Bijective between Inputs and Outputs. It not

only helps us to determine the outputs from the inputs but also

helps us to uniquely recover the inputs from the outputs [4].

Additional inputs or outputs can be added so as to make the

number of inputs and outputs equal whenever necessary. This also

refers to the number of outputs which are not used in the synthesis

of a given function. In certain cases these become mandatory to

achieve reversibility.

Inputs + Constant Inputs = Outputs + garbage

Fig. 1 shows a n-input and n-output Reversible Logic Gate and

is called as n*n Reversible logic gate, where nth

input of logic gate

is given by In and nth

output is given by On.

There exist many reversible gates in the literature. Among them

2*2 Feynman gate (shown in Fig. 2), 3*3 Feynman Double Gate

(shown in Fig. 3), 3*3 Fredkin gate [5] (shown in Fig. 4) are the

most preferred.

The Feynman Gate shown consists of two inputs A and B, two

outputs P(= A) and Q(= A B).

Fig. 2. Feynman Gate

The Feynman Double Gate shown consists of 3 inputs A,B and

C, 3 outputs P(= A),Q(= A xor B) and R(= A xor C).

Fig. 3. Feynman Double Gate

The Fredkin Gate shown consists of 3 inputs A,B and C, 3

outputs P(=A),Q(= AB xor AC) and R(= AC xor AB).

3

International Journal of Pure and Applied Mathematics Special Issue

439](https://image.slidesharecdn.com/ijpam-190201050516/85/FULL-ADDER-SUBTRACTOR-USING-REVERSIBLE-LOGIC-3-320.jpg)

![Fig. 8. Fault Tolerant Full Adder/ Subtractor

The Symbol showing Fault Tolerant Full Adder/ Subtractor

with 9 Inputs (4 inputs and 5 Constant Inputs) and 9 Outputs

(2 Outputs and 7 Garbage Outputs) is shown in Fig. 9

4.3 COMPARISON OF PROPOSED ARCHI-

TECTURE WITH EXISTING ARCHITEC-

TURE

Table II shows comparison of Half adder/Subtractor for existing [6]

and proposed architectures and Table III shows comparison of Full

Adder/Subtractor.

Fig.8. Hardware circuit Load connected

Fig.8. Hardware circuit Load connected

7

International Journal of Pure and Applied Mathematics Special Issue

443](https://image.slidesharecdn.com/ijpam-190201050516/85/FULL-ADDER-SUBTRACTOR-USING-REVERSIBLE-LOGIC-7-320.jpg)

![Fig.8. Hardware circuit Load connected

5 CONCLUSION

As Constant Inputs and Garbage Outputs are required to maintain

Reversibility, their number needs to be minimized. The Proposed

architecture has minimized both the Constant Inputs and Garbage

Outputs in comparison with existing architecture.

References

[1] R. Landauer, Irreversibility and heat generation in the com-

puting pro-cess, IBM Journal of Research and Development,

vol. 5, no. 3, pp. 183 191, July 1961.

[2] C. Bennett, Logical reversibility of computation, IBM Journal

of Research and Development, vol. 17, no. 6, pp. 525532, Nov

1973.

[3] S. K. S. Hari, S. Shroff, S. Mahammad, and V. Kamakoti, Effi-

cient building blocks for reversible sequential circuit design, in

Circuits and Systems, 2006. MWSCAS 06. 49th IEEE Interna-

tional Midwest Symposium on, vol. 1, Aug 2006, pp. 437441.

[4] J. Bruce, M. Thornton, L. Shivakumaraiah, P. Kokate, and X.

Li, Efficient adder circuits based on a conservative reversible

logic gate, in VLSI, 2002. Proceedings. IEEE Computer Society

Annual Symposium on, 2002, pp. 7479.

[5] D. Maslov, G. Dueck, and D. Miller, Synthesis of fredkin-toffoli

re-versible networks, Very Large Scale Integration (VLSI) Sys-

tems, IEEE Transactions on, vol. 13, no. 6, pp. 765769, June

2005.

8

International Journal of Pure and Applied Mathematics Special Issue

444](https://image.slidesharecdn.com/ijpam-190201050516/85/FULL-ADDER-SUBTRACTOR-USING-REVERSIBLE-LOGIC-8-320.jpg)

![[6] P. Kaur and B. Dhaliwal, Design of fault tolearnt full

adder/subtarctor using reversible gates, in Computer Commu-

nication and Informatics (ICCCI), 2012 International Confer-

ence on, Jan 2012, pp. 15.

9

International Journal of Pure and Applied Mathematics Special Issue

445](https://image.slidesharecdn.com/ijpam-190201050516/85/FULL-ADDER-SUBTRACTOR-USING-REVERSIBLE-LOGIC-9-320.jpg)