FABRICATION PROCESS

•

0 likes•696 views

Process of IC Fabrication with steps. The content presented are taken from various sources and explained using my understanding.

Report

Share

Report

Share

Download to read offline

Recommended

CMOS FABRICATION AND TECHNIQUES

Cmos fabrication is a part of semiconductor electronics that deals with the designing and fabrication process with NMOS and Cmos and other processes like Twin tub techniques and etc.

VLSI Design(Fabrication)

this ppt provides fabrication on SI wafer, CMOS fabrication process, basic CMOS inverter, future, application, advantage, disadvantage etc.

Cmos fabrication process

The CMOS fabrication process in VLSI.

CMOS (complementary metal-oxide-semiconductor) is the term usually used to describe the small amount of memory on a computer motherboard that stores the BIOS settings.

Recommended

CMOS FABRICATION AND TECHNIQUES

Cmos fabrication is a part of semiconductor electronics that deals with the designing and fabrication process with NMOS and Cmos and other processes like Twin tub techniques and etc.

VLSI Design(Fabrication)

this ppt provides fabrication on SI wafer, CMOS fabrication process, basic CMOS inverter, future, application, advantage, disadvantage etc.

Cmos fabrication process

The CMOS fabrication process in VLSI.

CMOS (complementary metal-oxide-semiconductor) is the term usually used to describe the small amount of memory on a computer motherboard that stores the BIOS settings.

IC Fabrication Process

Semiconductor device fabrication is the process used to create the integrated circuits that are present in everyday electrical and electronic devices. It is a multiple-step sequence of photo lithographic and chemical processing steps during which electronic circuits are gradually created on a wafer made of pure semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications.

Device isolation Techniques

In MOS, source-drain regions of adjacent MOS transistors together with interconnection metal lines may constitute parasitic MOS transistors unless they are isolated from each other. Hence, each MOSFET must be electrically isolated from each other. Device Isolation Techniques in VLSI microfabrication of MOS are discussed.

CMOS fabrication n well process

CMOS fabrication using n-well process: This is an industrial process used for making a CMOS inverter circuit.

CMOS Fabrication using P-well -VLSI

CMOS FABRICATION

For less power dissipation requirement CMOS technology is used for implementing transistors. If we require a faster circuit then transistors are implemented over IC using BJT . Fabrication of CMOS transistors as IC’s can be done in three different methods.

The N-well / P-well technology, where n-type diffusion is done over a p-type substrate or p-type diffusion is done over n-type substrate respectively.

P-WELL PROCESS

The fabrication steps of p well process are same as that of an n-well process except that instead of n-well a p-well is implanted . The process steps involved in p-well process are shown in Figure below. The process starts with the n type substrate

Ic tech unit 5- VLSI Process Integration

junction oxide and isolation techniques, LOCOS, Metallization, NMOS and CMOS technology, FAult diagnosis

More Related Content

What's hot

IC Fabrication Process

Semiconductor device fabrication is the process used to create the integrated circuits that are present in everyday electrical and electronic devices. It is a multiple-step sequence of photo lithographic and chemical processing steps during which electronic circuits are gradually created on a wafer made of pure semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications.

Device isolation Techniques

In MOS, source-drain regions of adjacent MOS transistors together with interconnection metal lines may constitute parasitic MOS transistors unless they are isolated from each other. Hence, each MOSFET must be electrically isolated from each other. Device Isolation Techniques in VLSI microfabrication of MOS are discussed.

CMOS fabrication n well process

CMOS fabrication using n-well process: This is an industrial process used for making a CMOS inverter circuit.

CMOS Fabrication using P-well -VLSI

CMOS FABRICATION

For less power dissipation requirement CMOS technology is used for implementing transistors. If we require a faster circuit then transistors are implemented over IC using BJT . Fabrication of CMOS transistors as IC’s can be done in three different methods.

The N-well / P-well technology, where n-type diffusion is done over a p-type substrate or p-type diffusion is done over n-type substrate respectively.

P-WELL PROCESS

The fabrication steps of p well process are same as that of an n-well process except that instead of n-well a p-well is implanted . The process steps involved in p-well process are shown in Figure below. The process starts with the n type substrate

Ic tech unit 5- VLSI Process Integration

junction oxide and isolation techniques, LOCOS, Metallization, NMOS and CMOS technology, FAult diagnosis

What's hot (20)

Similar to FABRICATION PROCESS

Fabrication of Floating Gate MOS (FLOTOX)

Floating Gate Devices are widely used in ROM based memories. In EEPROM, one such Floating gate MOS device FLOTOX is used. FLOTOX(Floating Gate Tunneling Oxide MOS) works on FN tunneling phenomenon. This presentation discusses the method for fabrication of such FLOTOX device(actually a EEPROM cell).

Monolithic implementation of parasitic elements

This presentation gives a brief about how a parasitic elements are fabricated using monolithic implementation

VLSI process integration

unit 5, IC Technology, RTU 8th sem ECE. isolation techniques (juntion, oxide, LOCOS, trench), bird's beak problem, planarisation, metallisation, CMP (chemical mechanical polishing), SOI (silicon on insulator)

MONOLITHIC IC PROCESSES ppt.pptx

MONOLITHIC IC PROCESSES A monolithic integrated circuit (IC) is a set of circuitry on a single semiconductor plate or chip rather than built of separate elements as a discrete circuit is.

Similar to FABRICATION PROCESS (20)

Recently uploaded

Sachpazis:Terzaghi Bearing Capacity Estimation in simple terms with Calculati...

Terzaghi's soil bearing capacity theory, developed by Karl Terzaghi, is a fundamental principle in geotechnical engineering used to determine the bearing capacity of shallow foundations. This theory provides a method to calculate the ultimate bearing capacity of soil, which is the maximum load per unit area that the soil can support without undergoing shear failure. The Calculation HTML Code included.

Hierarchical Digital Twin of a Naval Power System

A hierarchical digital twin of a Naval DC power system has been developed and experimentally verified. Similar to other state-of-the-art digital twins, this technology creates a digital replica of the physical system executed in real-time or faster, which can modify hardware controls. However, its advantage stems from distributing computational efforts by utilizing a hierarchical structure composed of lower-level digital twin blocks and a higher-level system digital twin. Each digital twin block is associated with a physical subsystem of the hardware and communicates with a singular system digital twin, which creates a system-level response. By extracting information from each level of the hierarchy, power system controls of the hardware were reconfigured autonomously. This hierarchical digital twin development offers several advantages over other digital twins, particularly in the field of naval power systems. The hierarchical structure allows for greater computational efficiency and scalability while the ability to autonomously reconfigure hardware controls offers increased flexibility and responsiveness. The hierarchical decomposition and models utilized were well aligned with the physical twin, as indicated by the maximum deviations between the developed digital twin hierarchy and the hardware.

Runway Orientation Based on the Wind Rose Diagram.pptx

Runway Orientation Based on the Wind Rose Diagram

一比一原版(IIT毕业证)伊利诺伊理工大学毕业证成绩单专业办理

IIT毕业证原版定制【微信:176555708】【伊利诺伊理工大学毕业证成绩单-学位证】【微信:176555708】(留信学历认证永久存档查询)采用学校原版纸张、特殊工艺完全按照原版一比一制作(包括:隐形水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠,文字图案浮雕,激光镭射,紫外荧光,温感,复印防伪)行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备,十五年致力于帮助留学生解决难题,业务范围有加拿大、英国、澳洲、韩国、美国、新加坡,新西兰等学历材料,包您满意。

◆◆◆◆◆ — — — — — — — — 【留学教育】留学归国服务中心 — — — — — -◆◆◆◆◆

【主营项目】

一.毕业证【微信:176555708】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【微信:176555708】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分→ 【关于价格问题(保证一手价格)

我们所定的价格是非常合理的,而且我们现在做得单子大多数都是代理和回头客户介绍的所以一般现在有新的单子 我给客户的都是第一手的代理价格,因为我想坦诚对待大家 不想跟大家在价格方面浪费时间

对于老客户或者被老客户介绍过来的朋友,我们都会适当给一些优惠。

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

选择实体注册公司办理,更放心,更安全!我们的承诺:可来公司面谈,可签订合同,会陪同客户一起到教育部认证窗口递交认证材料,客户在教育部官方认证查询网站查询到认证通过结果后付款,不成功不收费!

学历顾问:微信:176555708

HYDROPOWER - Hydroelectric power generation

Overview of the fundamental roles in Hydropower generation and the components involved in wider Electrical Engineering.

This paper presents the design and construction of hydroelectric dams from the hydrologist’s survey of the valley before construction, all aspects and involved disciplines, fluid dynamics, structural engineering, generation and mains frequency regulation to the very transmission of power through the network in the United Kingdom.

Author: Robbie Edward Sayers

Collaborators and co editors: Charlie Sims and Connor Healey.

(C) 2024 Robbie E. Sayers

Water Industry Process Automation and Control Monthly - May 2024.pdf

Water Industry Process Automation and Control Monthly - May 2024.pdfWater Industry Process Automation & Control

Welcome to WIPAC Monthly the magazine brought to you by the LinkedIn Group Water Industry Process Automation & Control.

In this month's edition, along with this month's industry news to celebrate the 13 years since the group was created we have articles including

A case study of the used of Advanced Process Control at the Wastewater Treatment works at Lleida in Spain

A look back on an article on smart wastewater networks in order to see how the industry has measured up in the interim around the adoption of Digital Transformation in the Water Industry.AKS UNIVERSITY Satna Final Year Project By OM Hardaha.pdf

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.

Thank me later.

samsarthak31@gmail.com

Final project report on grocery store management system..pdf

In today’s fast-changing business environment, it’s extremely important to be able to respond to client needs in the most effective and timely manner. If your customers wish to see your business online and have instant access to your products or services.

Online Grocery Store is an e-commerce website, which retails various grocery products. This project allows viewing various products available enables registered users to purchase desired products instantly using Paytm, UPI payment processor (Instant Pay) and also can place order by using Cash on Delivery (Pay Later) option. This project provides an easy access to Administrators and Managers to view orders placed using Pay Later and Instant Pay options.

In order to develop an e-commerce website, a number of Technologies must be studied and understood. These include multi-tiered architecture, server and client-side scripting techniques, implementation technologies, programming language (such as PHP, HTML, CSS, JavaScript) and MySQL relational databases. This is a project with the objective to develop a basic website where a consumer is provided with a shopping cart website and also to know about the technologies used to develop such a website.

This document will discuss each of the underlying technologies to create and implement an e- commerce website.

Investor-Presentation-Q1FY2024 investor presentation document.pptx

this is the investor presemtaiton document for qurrter 1 2024

一比一原版(SFU毕业证)西蒙菲莎大学毕业证成绩单如何办理

SFU毕业证原版定制【微信:176555708】【西蒙菲莎大学毕业证成绩单-学位证】【微信:176555708】(留信学历认证永久存档查询)采用学校原版纸张、特殊工艺完全按照原版一比一制作(包括:隐形水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠,文字图案浮雕,激光镭射,紫外荧光,温感,复印防伪)行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备,十五年致力于帮助留学生解决难题,业务范围有加拿大、英国、澳洲、韩国、美国、新加坡,新西兰等学历材料,包您满意。

◆◆◆◆◆ — — — — — — — — 【留学教育】留学归国服务中心 — — — — — -◆◆◆◆◆

【主营项目】

一.毕业证【微信:176555708】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【微信:176555708】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分→ 【关于价格问题(保证一手价格)

我们所定的价格是非常合理的,而且我们现在做得单子大多数都是代理和回头客户介绍的所以一般现在有新的单子 我给客户的都是第一手的代理价格,因为我想坦诚对待大家 不想跟大家在价格方面浪费时间

对于老客户或者被老客户介绍过来的朋友,我们都会适当给一些优惠。

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

选择实体注册公司办理,更放心,更安全!我们的承诺:可来公司面谈,可签订合同,会陪同客户一起到教育部认证窗口递交认证材料,客户在教育部官方认证查询网站查询到认证通过结果后付款,不成功不收费!

学历顾问:微信:176555708

J.Yang, ICLR 2024, MLILAB, KAIST AI.pdf

Language-Interfaced Tabular Oversampling Via Progressive Imputation And Self Autentication

Gen AI Study Jams _ For the GDSC Leads in India.pdf

Gen AI Study Jams _ For the GDSC Leads in India.pdf

Recently uploaded (20)

Sachpazis:Terzaghi Bearing Capacity Estimation in simple terms with Calculati...

Sachpazis:Terzaghi Bearing Capacity Estimation in simple terms with Calculati...

Runway Orientation Based on the Wind Rose Diagram.pptx

Runway Orientation Based on the Wind Rose Diagram.pptx

Water Industry Process Automation and Control Monthly - May 2024.pdf

Water Industry Process Automation and Control Monthly - May 2024.pdf

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.pdf

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.pdf

Final project report on grocery store management system..pdf

Final project report on grocery store management system..pdf

Planning Of Procurement o different goods and services

Planning Of Procurement o different goods and services

ML for identifying fraud using open blockchain data.pptx

ML for identifying fraud using open blockchain data.pptx

Investor-Presentation-Q1FY2024 investor presentation document.pptx

Investor-Presentation-Q1FY2024 investor presentation document.pptx

block diagram and signal flow graph representation

block diagram and signal flow graph representation

MCQ Soil mechanics questions (Soil shear strength).pdf

MCQ Soil mechanics questions (Soil shear strength).pdf

Gen AI Study Jams _ For the GDSC Leads in India.pdf

Gen AI Study Jams _ For the GDSC Leads in India.pdf

FABRICATION PROCESS

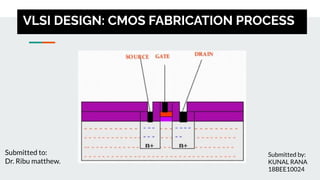

- 1. VLSI DESIGN: CMOS FABRICATION PROCESS Submitted to: Dr. Ribu matthew. Submitted by: KUNAL RANA 18BEE10024

- 2. STEP 1: ● First we choose a substrate for Nmos fabrication. ● P-Type substrate is preferred for NMOS Transistor.

- 3. STEP 2: ● A layer of silicon dioxide (SiO2) typically 1 micrometer thick is grown all over the surface of the wafer to protect the surface and provide a generally insulating substrate on to which other layers may be deposited and patterned.

- 4. STEP 3: ● The Photolithography is done next. ● The surface is removed with photoresist which is deposited and spun to achieve the even distribution.

- 5. STEP 4: ● A mask is placed on PR later. Which defines where regions into diffusion is to take place together with transmission channels. i.e.UV light passed and the area exposed to light gets hardened while keeping Others unaffected ● The unaffected area is etched away with underlying thick OX i.e.The remaining PR is removed

- 6. STEP 5: ● The remaining photoresist is removed and a thin layer of SiO2 is grown over the entire chip surface and then poly silicon is deposited on the top of this to form the gate structure. ● Further photoresist coating and masking allows the polysilicon to be patterned and then the thin oxide is removed to expose areas into which n-type impurities are to be diffused to form the source and drain.

- 7. STEP 6: ● The gate is formed by photolithography.

- 8. STEP 7: ● The n-type impurities are diffused in the exposed p-substrate from source and drain ● Diffusion is done by heating the water to a high temperature and passing gas containing the desired n-type impurities over the surface.

- 9. STEP 8: ● Thick OX layer is grown and then by photo photolithography 'contact cuts' are formed.

- 10. STEP 9: ● The whole chip then has metal (aluminium) deposited over its surface. This metal layer is then masked and etched to form the required interconnection pattern.

- 11. THANK YOU.