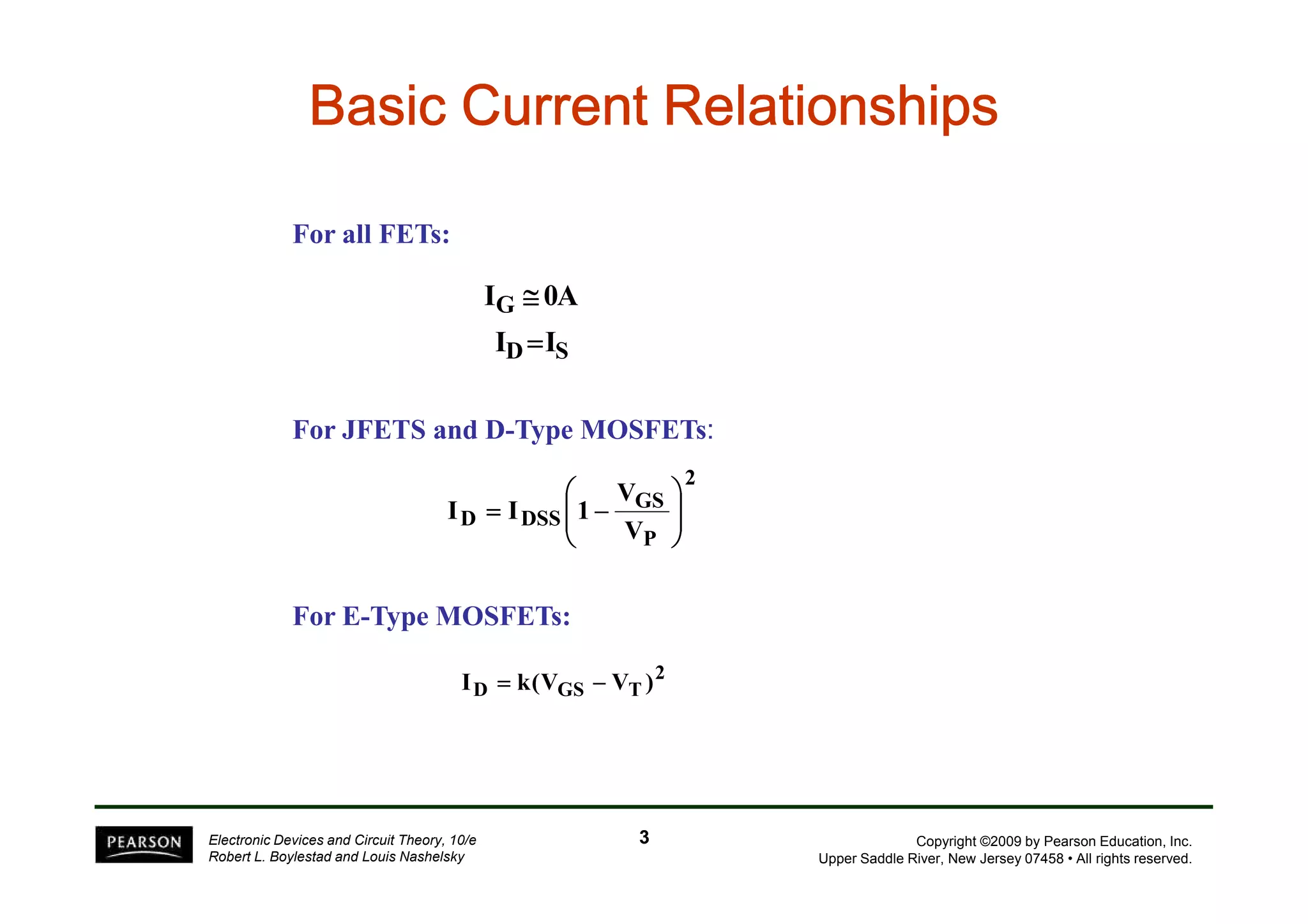

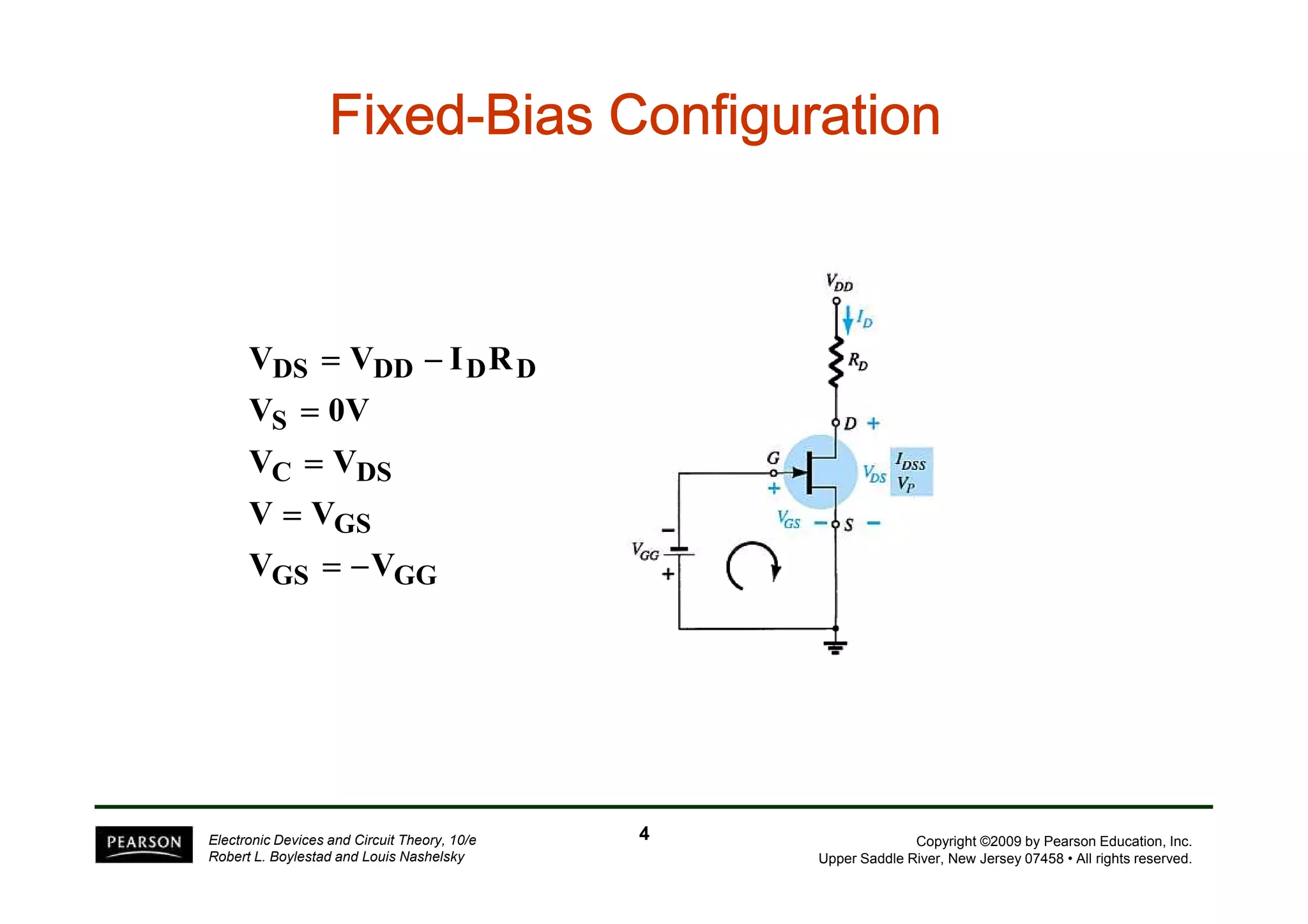

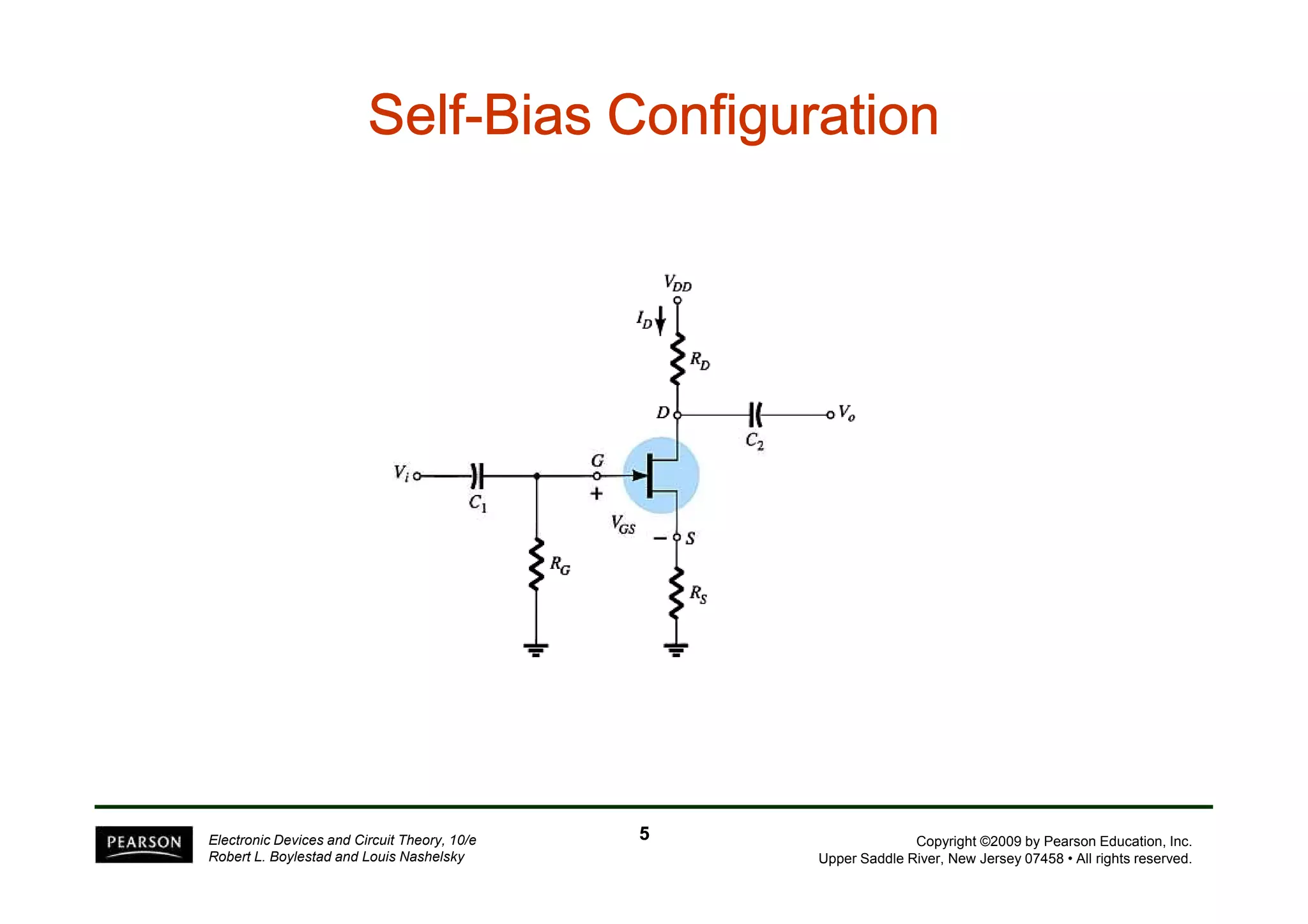

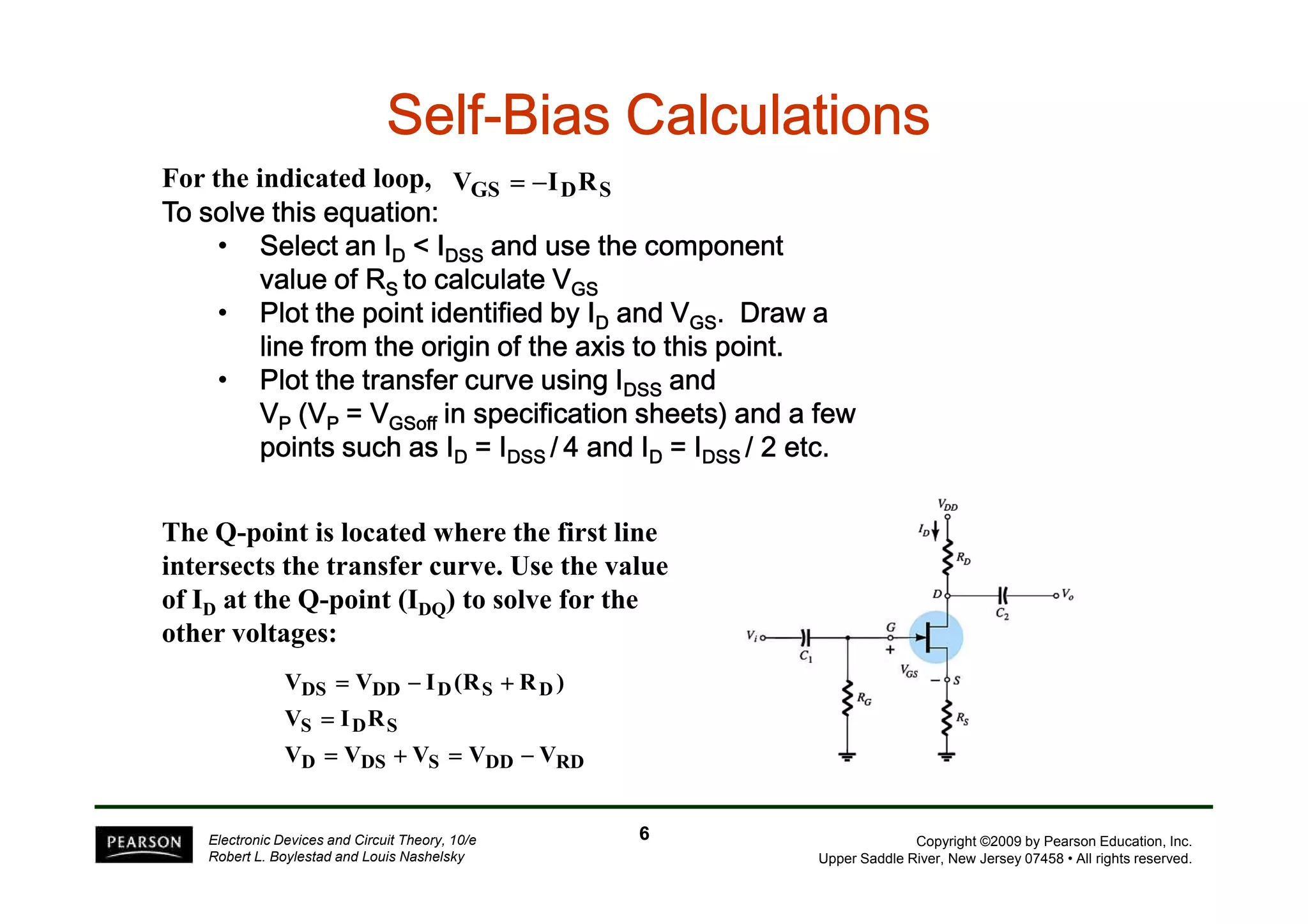

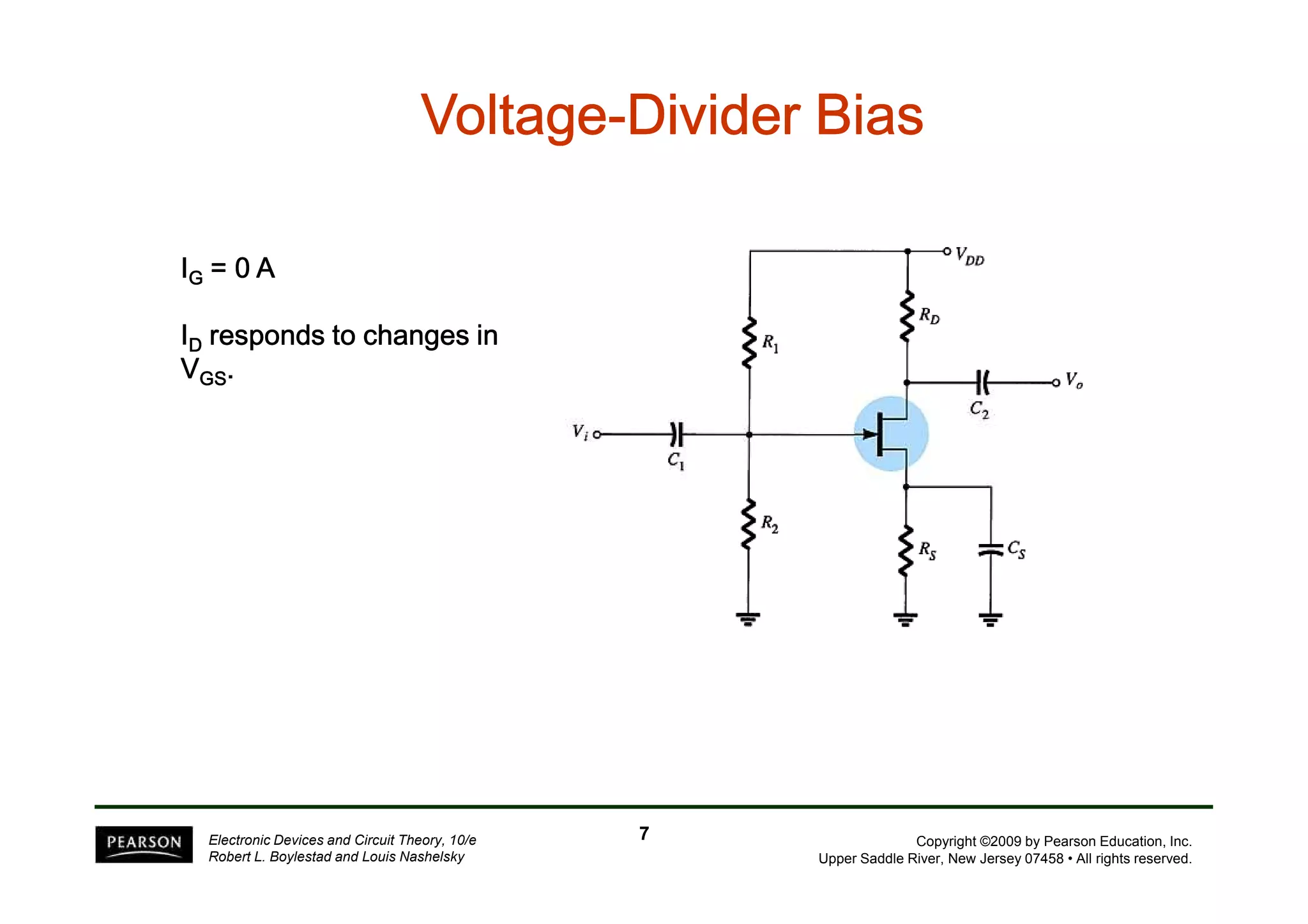

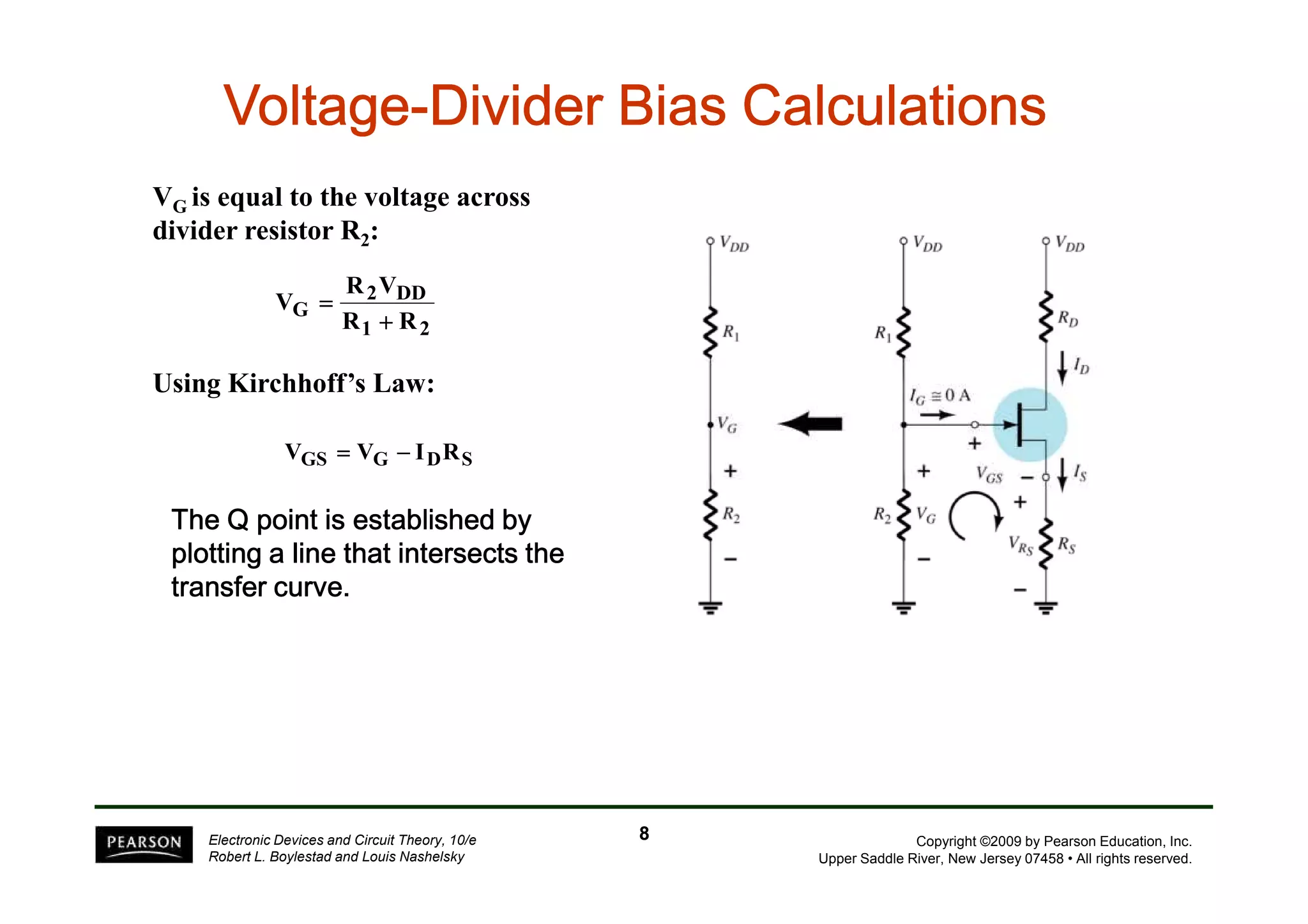

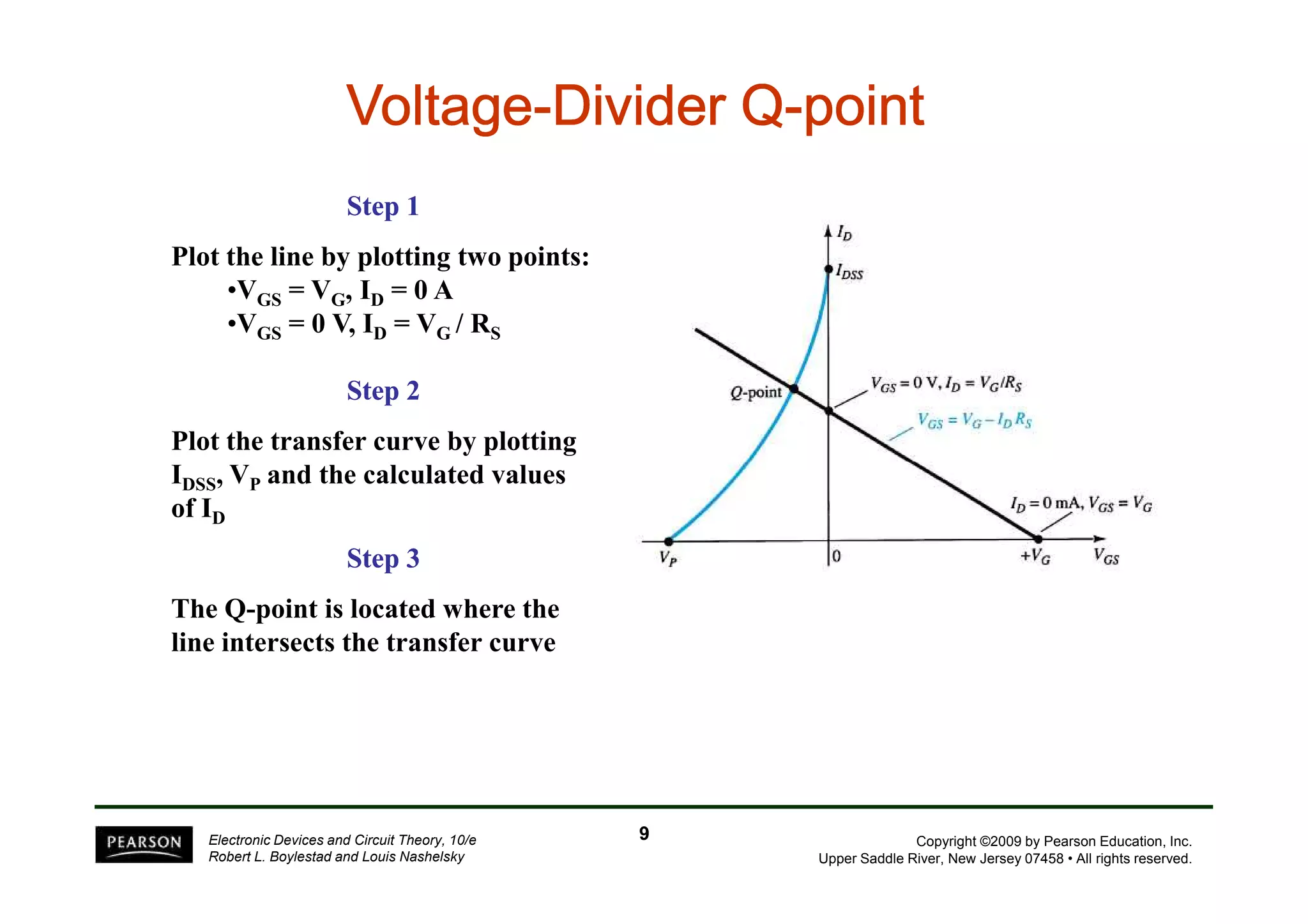

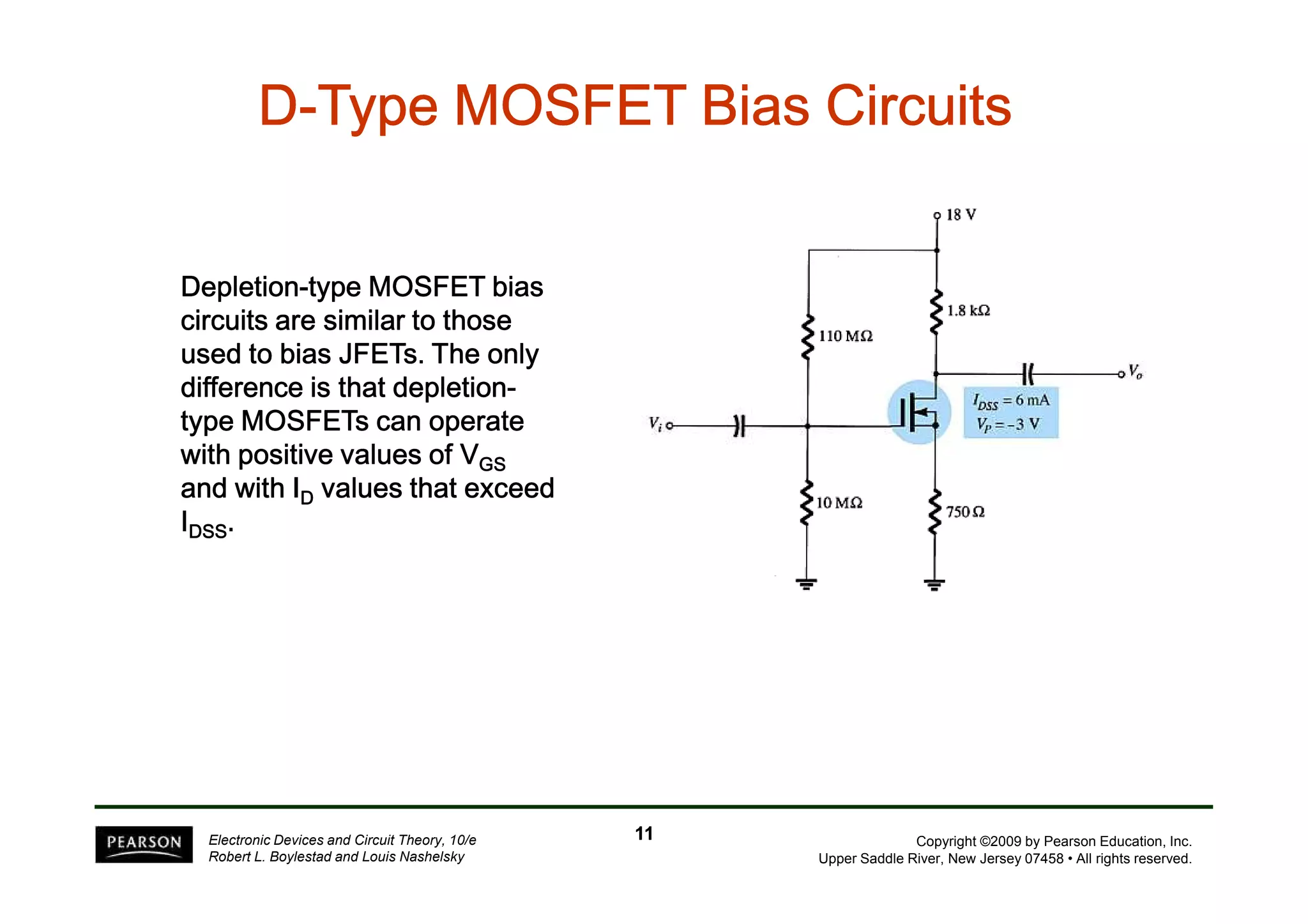

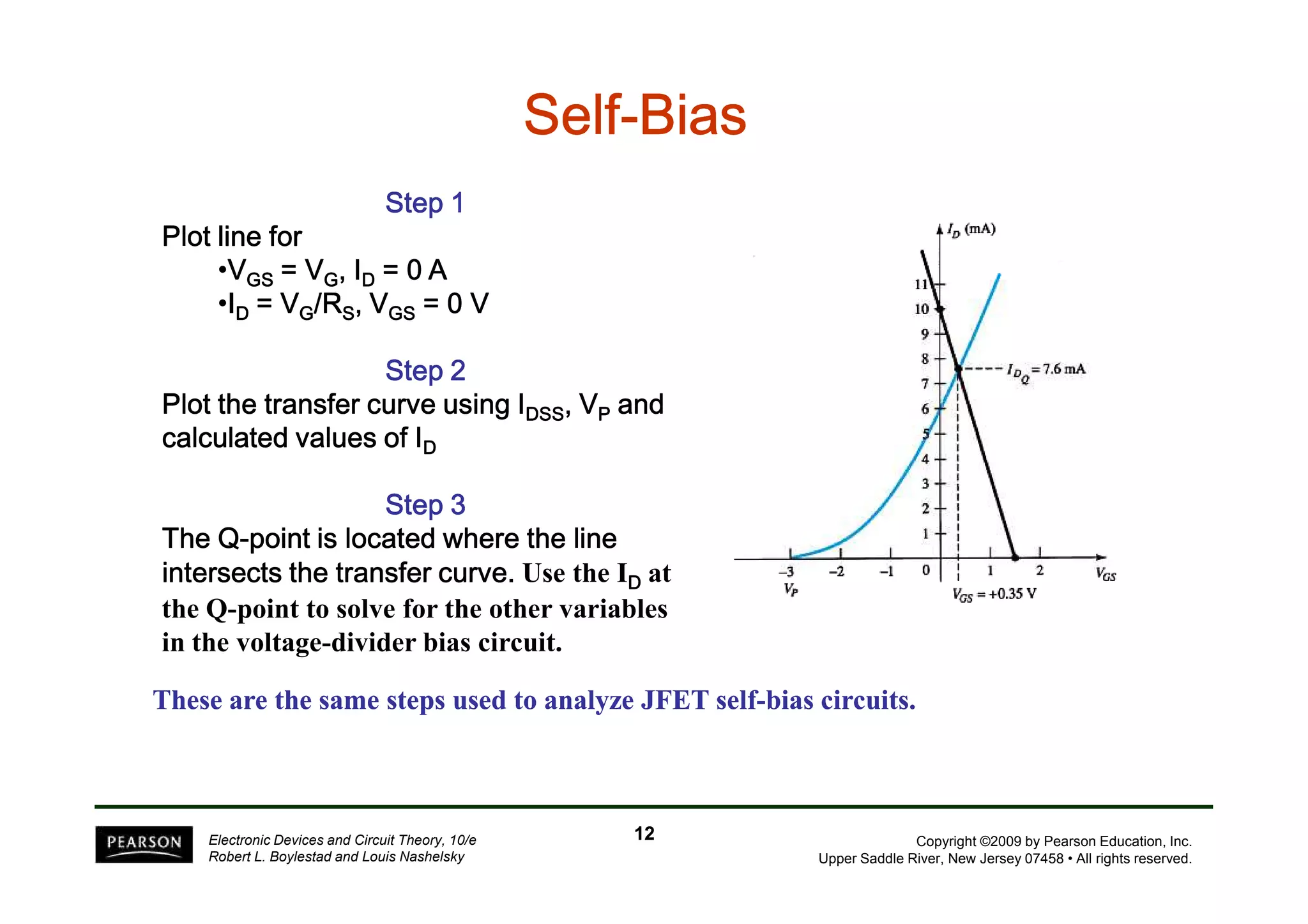

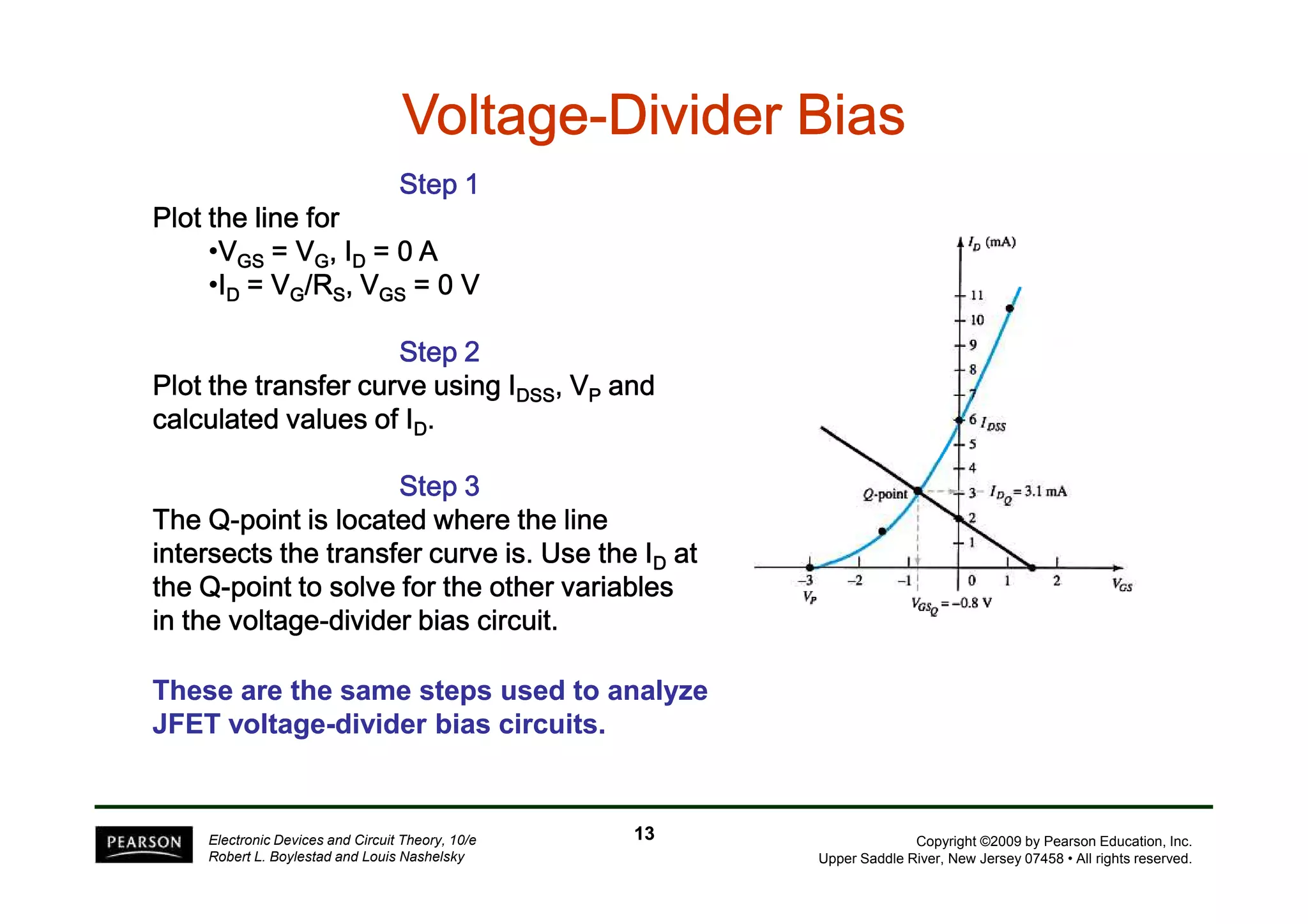

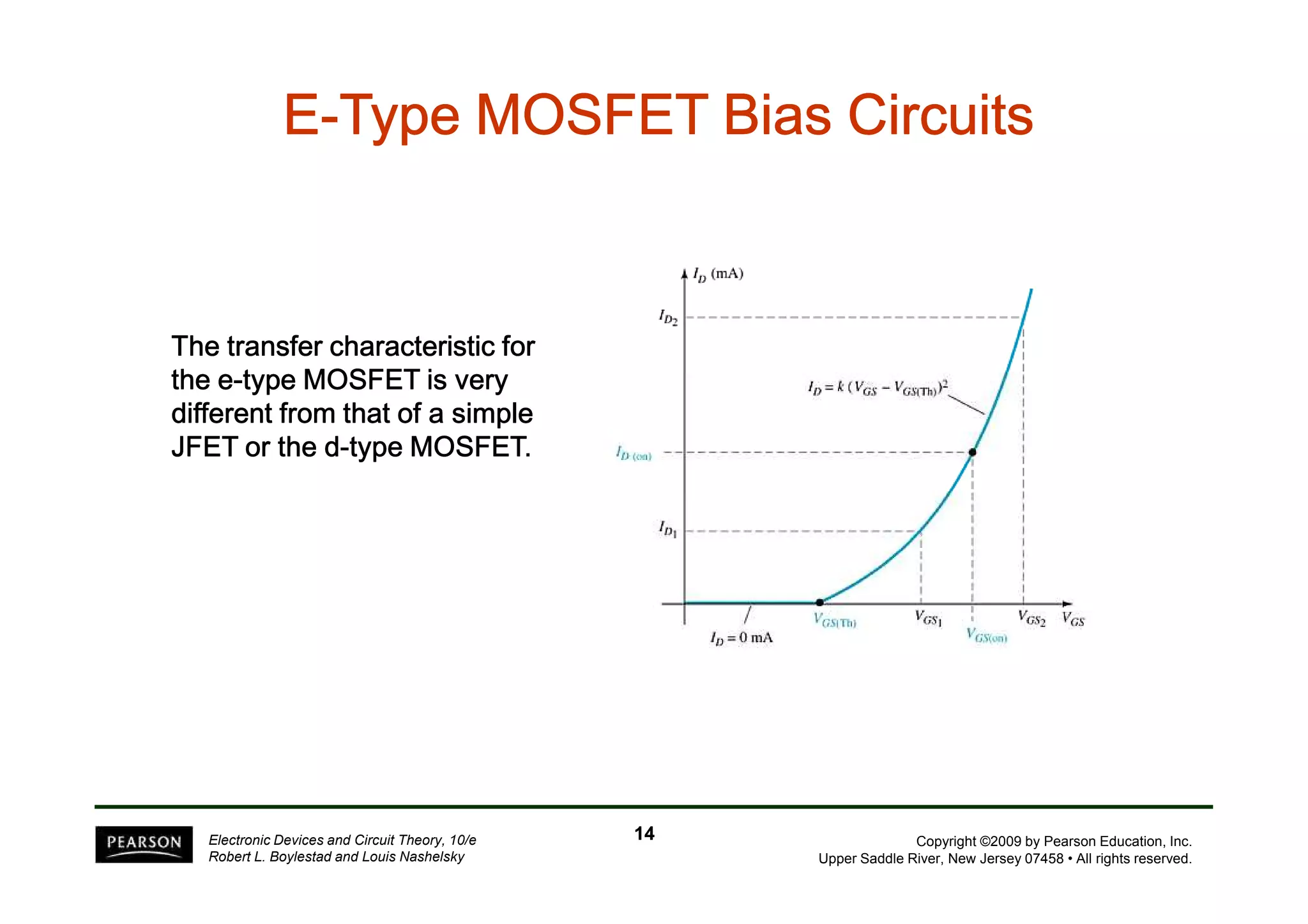

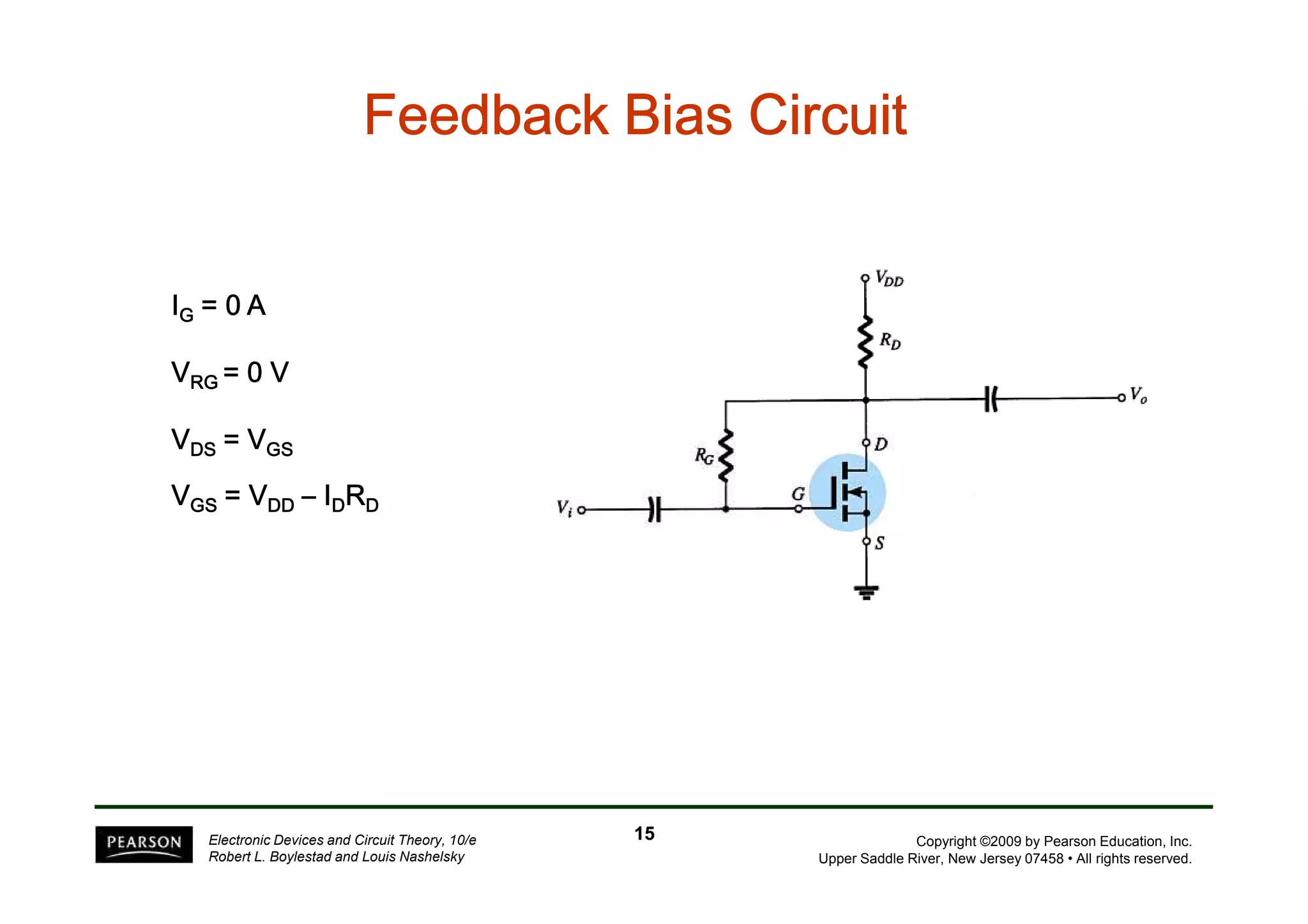

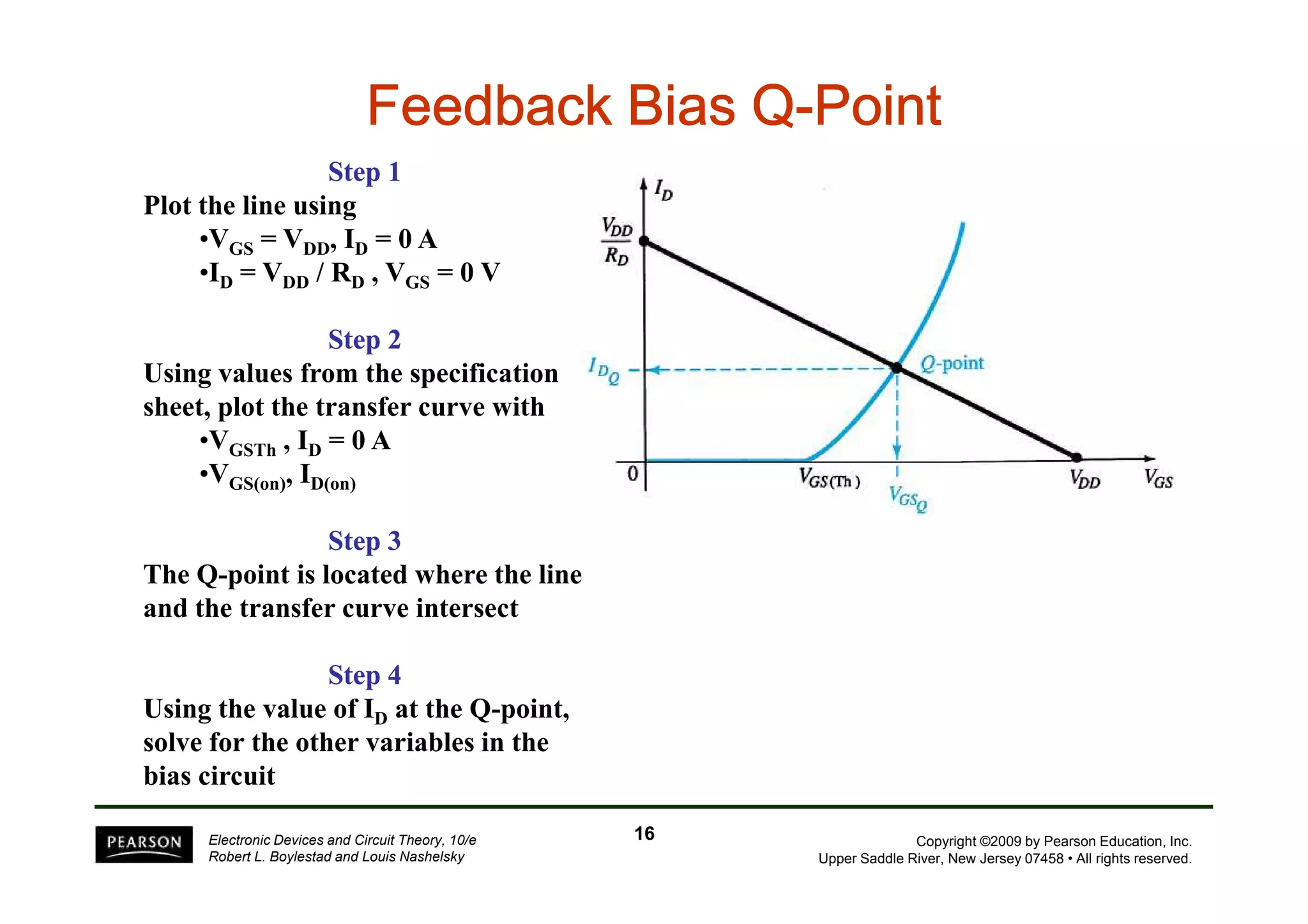

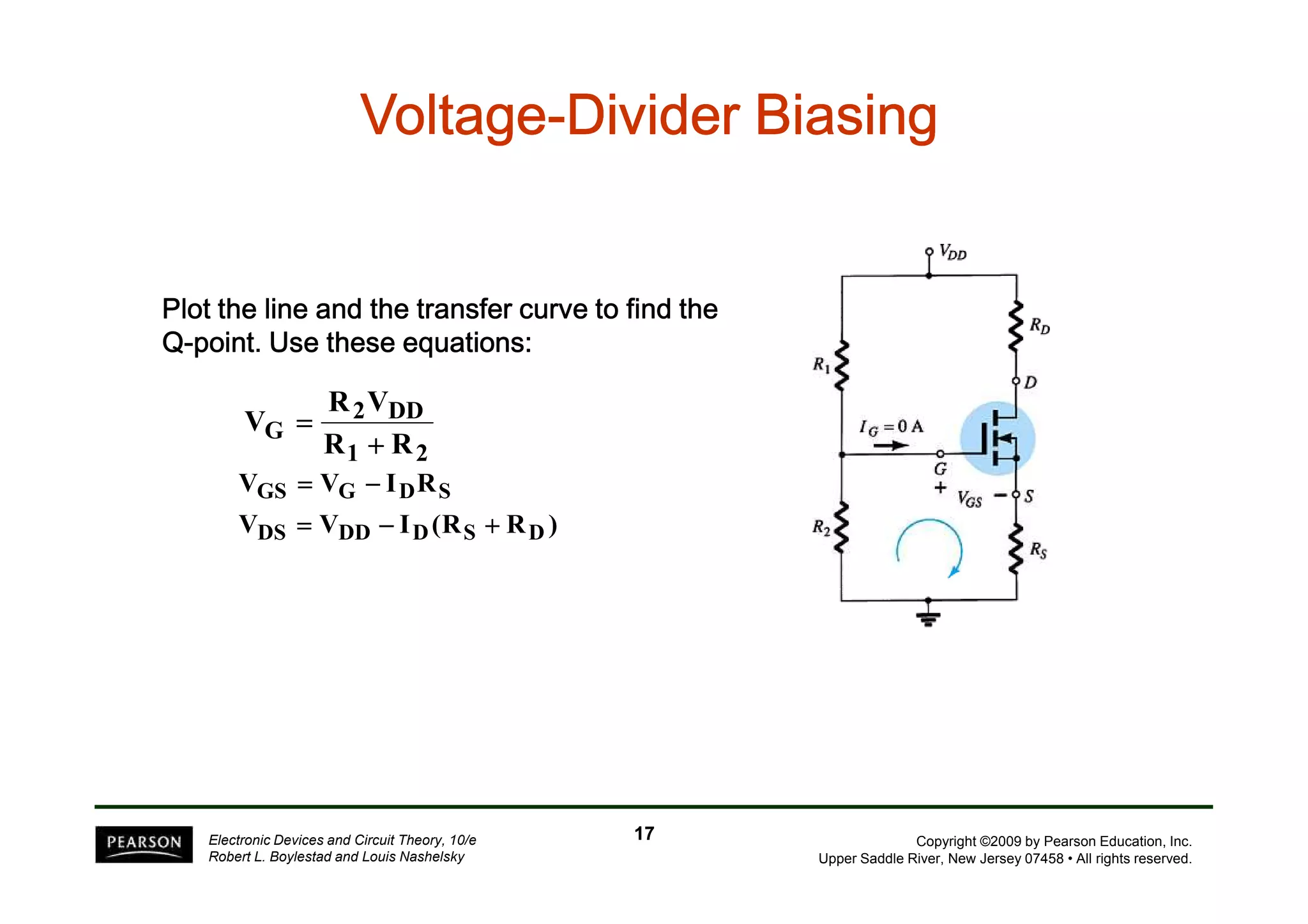

This chapter discusses various biasing circuits used for field effect transistors (FETs). It describes fixed-bias, self-bias, and voltage divider bias configurations for JFETs and MOSFETs. The key steps to analyze self and voltage divider bias circuits are: 1) Plot the transistor transfer curve and bias line, 2) Find the Q-point where they intersect, 3) Use the Q-point values to calculate the other circuit voltages and currents. D-type MOSFET biasing is similar to JFET biasing, except they can operate with positive VGS values and higher ID values than IDSS.