dsd for traditional system design for elecronics.ppt

•Download as PPT, PDF•

0 likes•1 view

Traditional system design

Report

Share

Report

Share

Recommended

The Author of this document is

Dr. Abdulfatah A. SalemOperations Management - Book1.p - Dr. Abdulfatah A. Salem

Operations Management - Book1.p - Dr. Abdulfatah A. SalemArab Academy for Science, Technology and Maritime Transport

More Related Content

Similar to dsd for traditional system design for elecronics.ppt

Similar to dsd for traditional system design for elecronics.ppt (20)

Basic Design Flow for Field Programmable Gate Arrays

Basic Design Flow for Field Programmable Gate Arrays

Recently uploaded

The Author of this document is

Dr. Abdulfatah A. SalemOperations Management - Book1.p - Dr. Abdulfatah A. Salem

Operations Management - Book1.p - Dr. Abdulfatah A. SalemArab Academy for Science, Technology and Maritime Transport

Recently uploaded (20)

Operations Management - Book1.p - Dr. Abdulfatah A. Salem

Operations Management - Book1.p - Dr. Abdulfatah A. Salem

REPRODUCTIVE TOXICITY STUDIE OF MALE AND FEMALEpptx

REPRODUCTIVE TOXICITY STUDIE OF MALE AND FEMALEpptx

Features of Video Calls in the Discuss Module in Odoo 17

Features of Video Calls in the Discuss Module in Odoo 17

Exploring Gemini AI and Integration with MuleSoft | MuleSoft Mysore Meetup #45

Exploring Gemini AI and Integration with MuleSoft | MuleSoft Mysore Meetup #45

INU_CAPSTONEDESIGN_비밀번호486_업로드용 발표자료.pdf

INU_CAPSTONEDESIGN_비밀번호486_업로드용 발표자료.pdf

Removal Strategy _ FEFO _ Working with Perishable Products in Odoo 17

Removal Strategy _ FEFO _ Working with Perishable Products in Odoo 17

Basic Civil Engg Notes_Chapter-6_Environment Pollution & Engineering

Basic Civil Engg Notes_Chapter-6_Environment Pollution & Engineering

How to Manage Notification Preferences in the Odoo 17

How to Manage Notification Preferences in the Odoo 17

Application of Matrices in real life. Presentation on application of matrices

Application of Matrices in real life. Presentation on application of matrices

Post Exam Fun(da) Intra UEM General Quiz - Finals.pdf

Post Exam Fun(da) Intra UEM General Quiz - Finals.pdf

Post Exam Fun(da) Intra UEM General Quiz 2024 - Prelims q&a.pdf

Post Exam Fun(da) Intra UEM General Quiz 2024 - Prelims q&a.pdf

dsd for traditional system design for elecronics.ppt

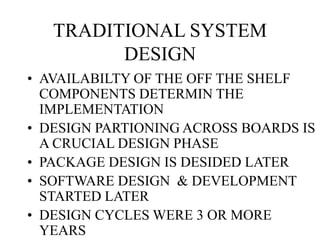

- 1. TRADITIONAL SYSTEM DESIGN • AVAILABILTY OF THE OFF THE SHELF COMPONENTS DETERMIN THE IMPLEMENTATION • DESIGN PARTIONING ACROSS BOARDS IS A CRUCIAL DESIGN PHASE • PACKAGE DESIGN IS DESIDED LATER • SOFTWARE DESIGN & DEVELOPMENT STARTED LATER • DESIGN CYCLES WERE 3 OR MORE YEARS

- 2. CONTINUED…… • COMPONENTS BECOMING OBSOLETEWAS A LURKING DANGER • CHANGES IN SPECIFICATIONS INVOLVED COSTLY DESIGN ITERATIONS

- 3. FPGAs & GATE ARRAYS • HIGHLY FEXIBLE • LOW ENERGY COST • SHORTER DEVELOPMENT CYCLE • LOW RISK • NEGLIGIBLE ITERATION COST • EMINENTLY SUITABLE FOR LOW VOLUMES • NO COMLICATED & ELABORATE TEST DESIGN

- 4. Programmable logic device (PLD)? It is an IC used to build digital circuits. Unlike a logic gate which has a fixed function, a PLD has an undefined function at the time of manufacture. Before the PLD can be used in a circuit it can be configured by the user to perform a logic function by programming it.

- 5. TYPES PROM FIXED AND ARRAY & PROGRAMMABLE OR ARRAY PLA AND & OR ARRAY PROGRAMMABLE PAL PROGAMMABLE AND &FIXED OR

- 6. Early programmable logic In 1970, TEXAS INSTRUMENTS developed a mask-programmable IC, the TMS2000, was programmed by altering the metal layer during the production of the IC. TI coined the term PROGRAMMABLE LOGIC ARRAY for this device.

- 7. ROM as a PLD Before PLDs were invented, (ROM) chips were used to create arbitrary COMBINATIONAL LOGIC functions

- 11. PAL devices consists of a small PROM (programmable read-only memory) core and additional output logic used to implement particular desired logic functions with few components

- 15. Programming languages • PALASM • ABEL • VHDL

- 16. PALASM

- 17. INTRODUCTION • PALASM IS A SOFTWARE WHICH CONVERTSAN INPUT PLD DESIGN INTO A JEDEC FILE

- 18. JEDEC JOINED ELECTRON DEVICE ENGINEERING COUNCIL

- 19. A JEDEC FILE • SPECIFIES WHICH FUCES ARE TO BE BLOWN ON THE TARGET DEVICE • CAN BE USED TO PROGRAM PLDS ON A PROGRAMER

- 20. ROLE OF PALASM • HIGH LEVEL LANGUAGE • COMPILER • MACHINE CODE • PALASM SOURCE • PALASM • JEDEC FILE

- 22. OPERATIONS SEQUENCE STEP1 INPUT SOURCE FILE • CHECK INPUT SYNTAX • EXPAND FUNCTIONS • MINIMIZE EQUATIONS • ASSEMBLE • SIMULATE • TRACEFILE OUTPUT OR WAVEFORMS STEP2 INPUT SOURCE FILE • CHECK INPUT SYNTAX • EXPAND FUNCTIONS • MINIMIZE EQUATIONS • ASSEMBLE • JEDEC FILE AND FUSE MAP

- 23. CPLD

- 24. Field-programmable gate array • A field programmable gate array (FPGA) is a semiconductor device containing programmable logic components and programmable interconnects.

- 25. •The programmable logic components can be programmed to duplicate the functionality of basic logic gates such as AND, OR, XOR,NOT or more complex combinational functions such as decoders or simple math functions.

- 26. In most FPGAs, these programmable logic components (or logic blocks, in FPGA ) also include memory elements, which may be simple flipflops or more complete blocks of memories.

- 27. Architecture The basic architecture consists of an array of configurable logic blocks (CLBs) and routing channels. Multiple I/Opads may fit into the height of One row or the width of one column. Generally, all the routing channels have the same width (number of wires). An application circuit must be mapped into an FPGA with adequate resources.

- 31. THANK YOU