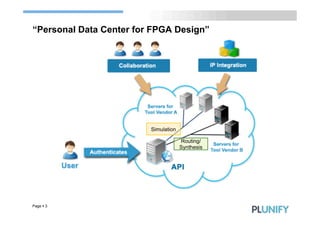

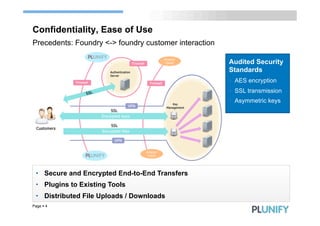

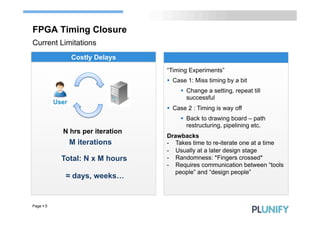

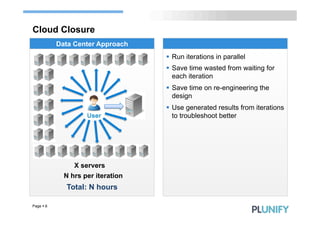

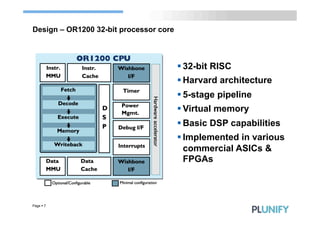

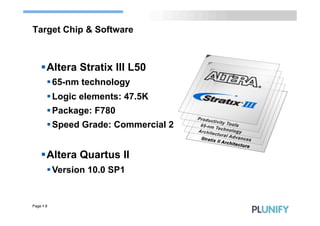

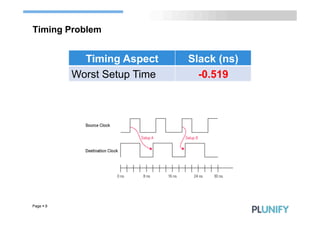

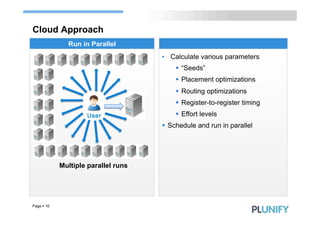

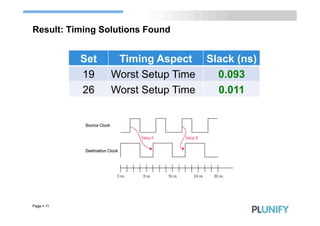

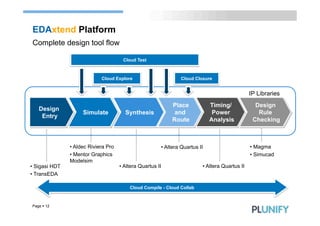

The document discusses the benefits of using cloud computing for FPGA design, focusing on personal data centers to improve timing closure processes. It emphasizes the advantages of parallel processing to save time and enhance design iterations through secure, easy-to-use tools while detailing specific technical approaches and future developments. Additionally, it outlines next steps for expanding support for FPGA processes and invites feedback from users.