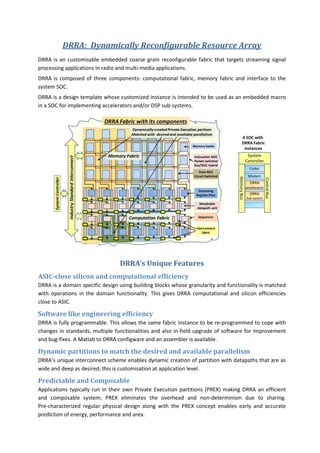

The document details the Dynamic Reconfigurable Resource Array (DRRA), a customizable embedded fabric design targeted at signal processing applications in radio and multimedia. DRRA consists of a computational fabric, memory fabric, and system interface, allowing for application-level customizations and efficient resource management through dynamic partitioning and fine-grained power management. Its industrial evaluation highlights its ability to handle multiple functionalities efficiently, demonstrating computational and silicon efficiency comparable to ASICs.