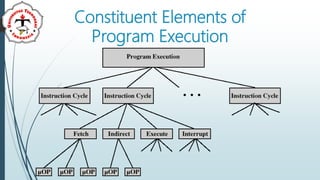

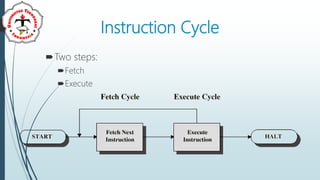

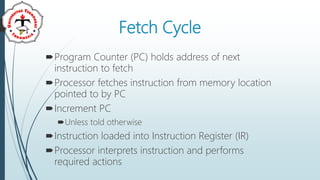

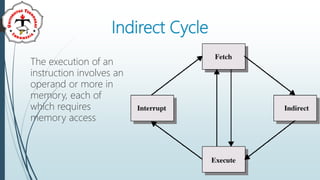

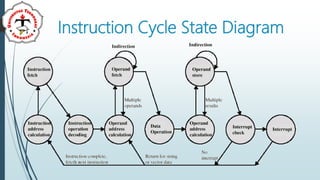

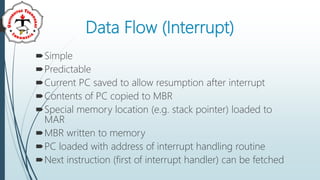

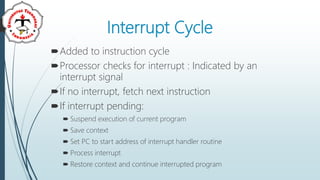

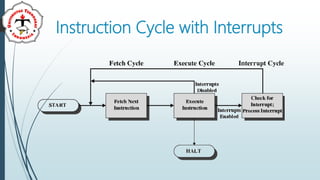

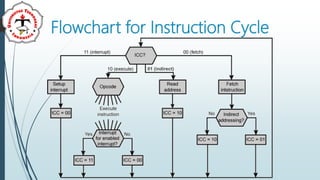

The document discusses the control unit (CU) and how it executes micro-operations to control the flow of instructions in a computer's central processing unit (CPU). It explains that the CU breaks down each instruction fetch and execute cycle into discrete micro-operations that transfer data between registers and memory. These include operations to fetch instructions from memory into registers using the program counter, memory address register, memory buffer register, and instruction register. The document also describes how the CU handles interrupts by saving the program context and loading the interrupt handling routine address.