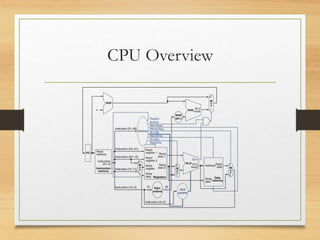

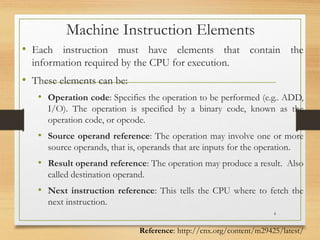

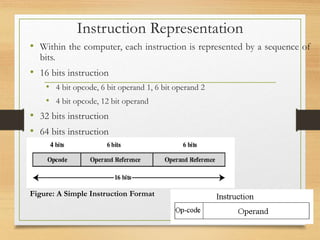

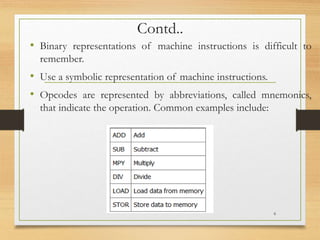

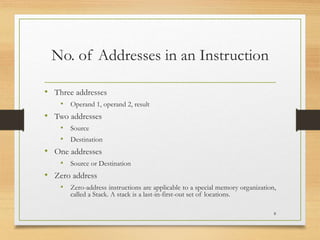

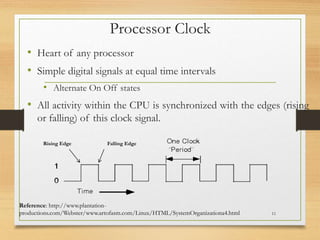

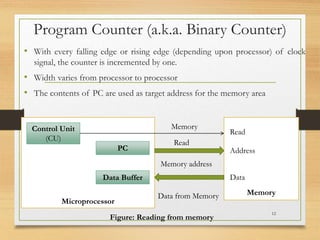

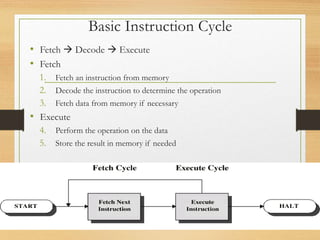

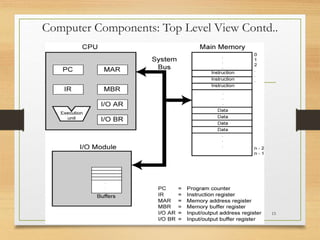

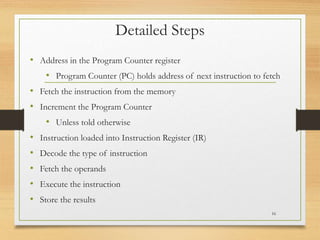

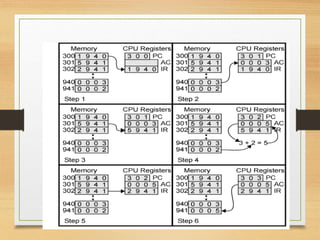

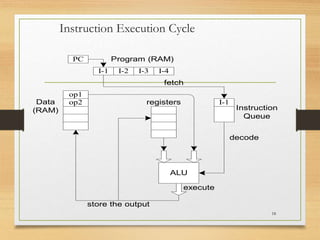

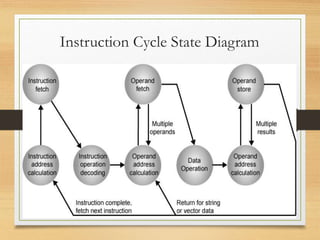

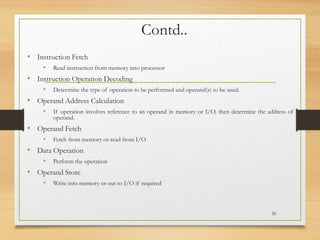

The document outlines the fundamentals of CPU and processor operation, detailing instruction representation, instruction cycles, and elements of machine instructions. It describes various instruction types, operand categories, and the significance of the processor clock in synchronizing CPU activities. Additionally, it explains the basic instruction cycle of fetch, decode, and execute, highlighting the role of critical CPU registers.