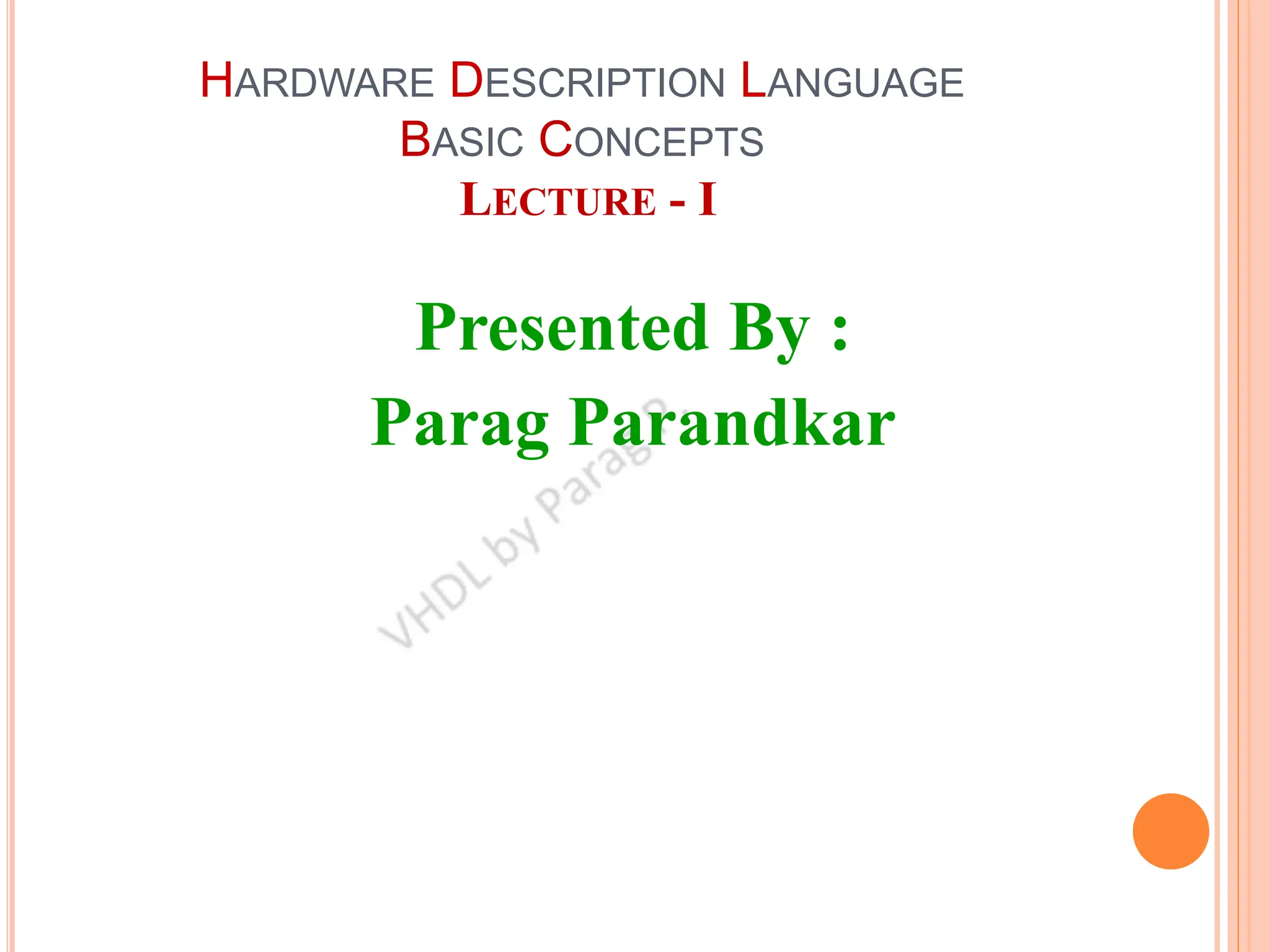

The document is a lecture on the basic concepts of VHDL (Very High Speed Integrated Circuit Hardware Description Language), covering its purpose, capabilities, and the fundamentals of simulation. It explains modeling hardware with VHDL, detailing different levels of abstraction such as behavioral and structural models, alongside design units and libraries. It includes examples of VHDL syntax for defining components and their interconnections, emphasizing the role of entities and architectures.

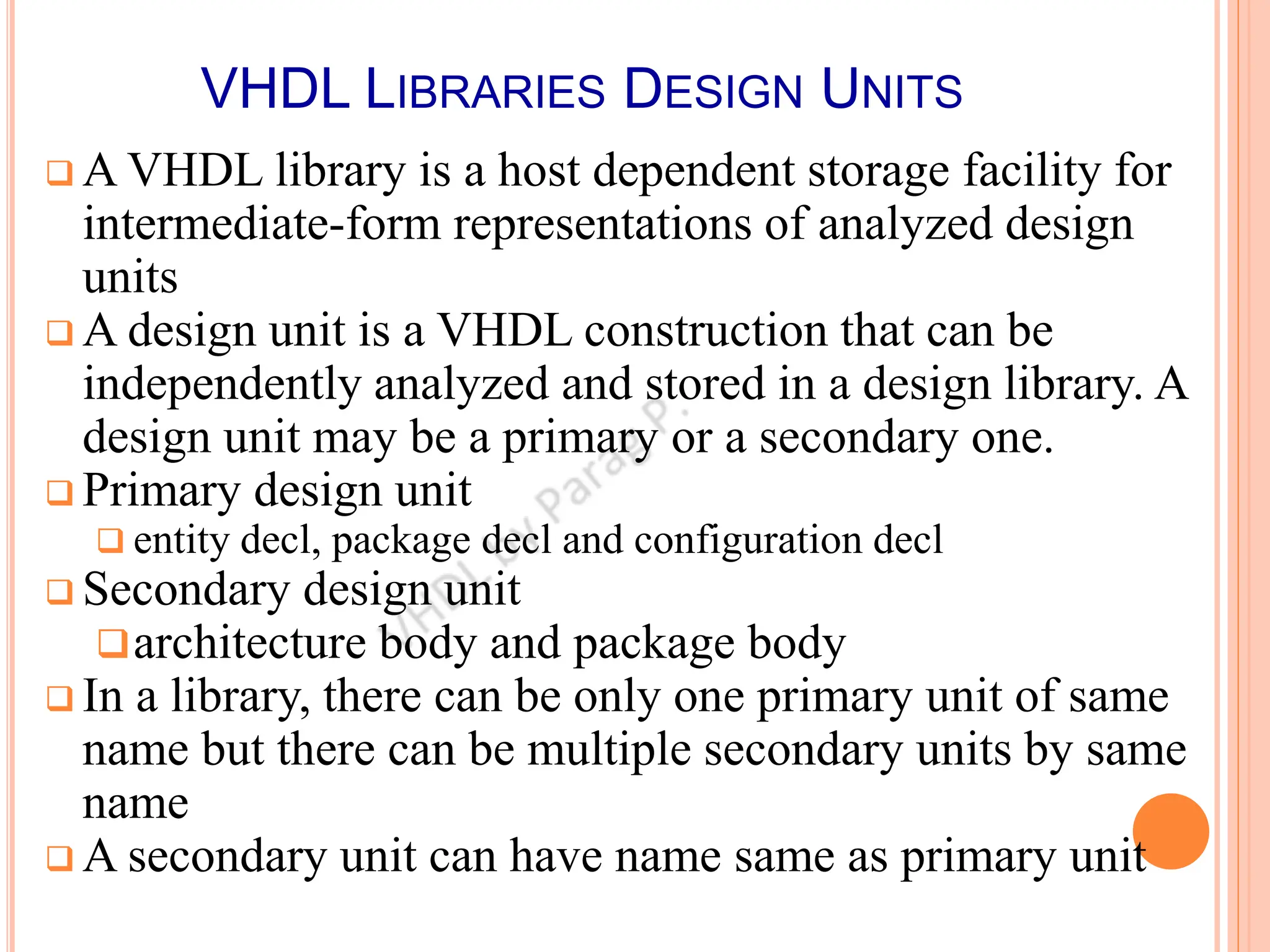

![ENTITY

provides a name to the component

contains the port definitions in the interface list

can contain some generic definitions which can

be used to override default values

entity identifier is

generic interface_list;

port interface_list;

declarations

begin

statements

end [entity] [identifier];](https://image.slidesharecdn.com/vhdllecture1-231007031451-083cd73b/75/VHDL-lecture-1-ppt-14-2048.jpg)

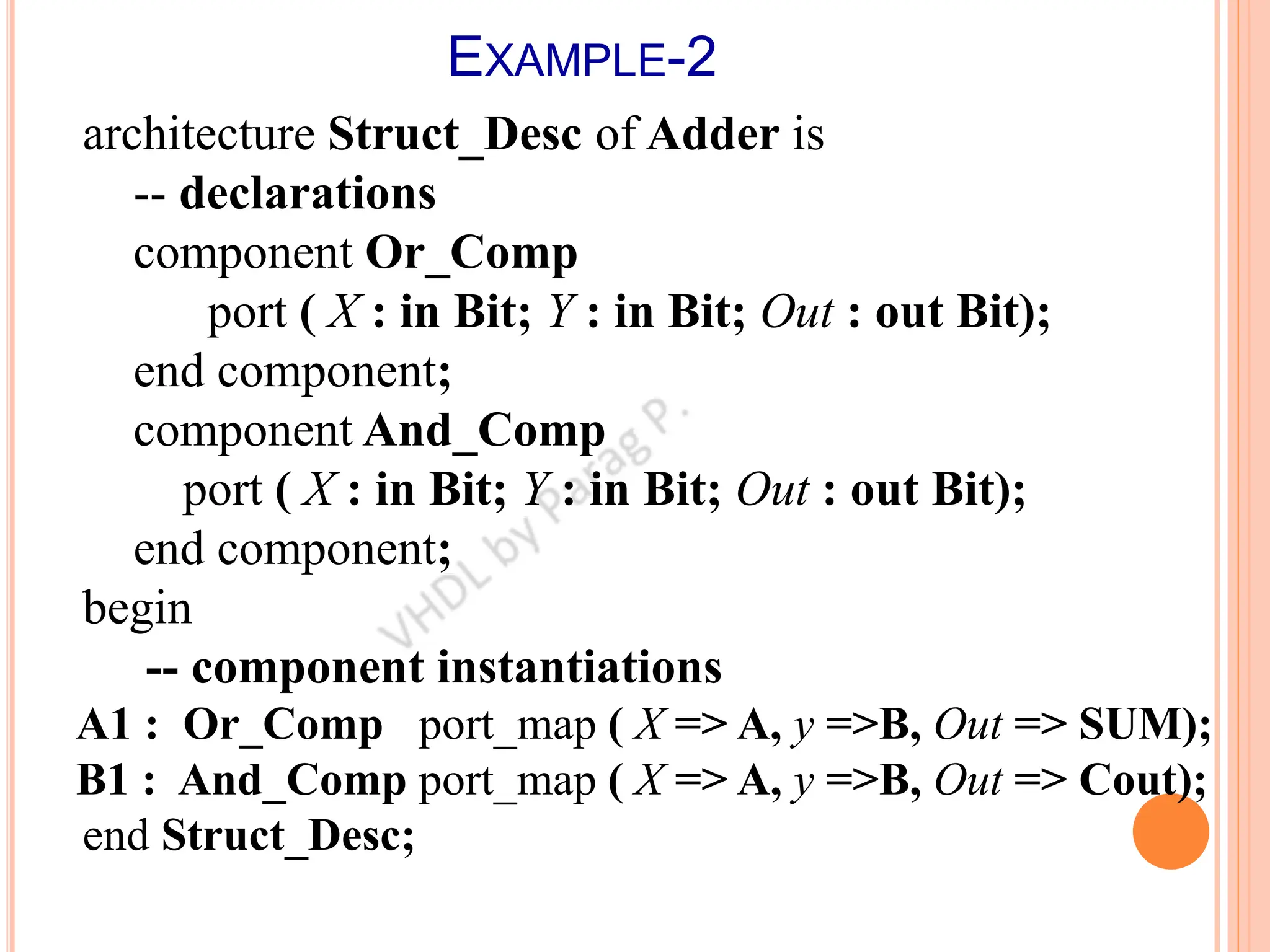

![ARCHITECTURE

encapsulates the behavior and timing

information

contains a number of concurrent statements

there can be multiple architecture bodies for a

given entity

architecture identifier of entity_name is

declarations

begin

statements

end [architecture] [identifier];](https://image.slidesharecdn.com/vhdllecture1-231007031451-083cd73b/75/VHDL-lecture-1-ppt-16-2048.jpg)