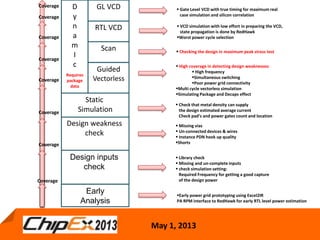

The document discusses a power delivery network (PDN) verification flow to analyze power, noise, and reliability for advanced electronic systems. The flow aims to provide high design failure coverage through early detection of faults and weaknesses, enabling early prototyping and improvement of productivity. It involves checks for design weaknesses, static simulation, scan and gate-level vectorless simulation incorporating package and decap effects to thoroughly test designs under different conditions.