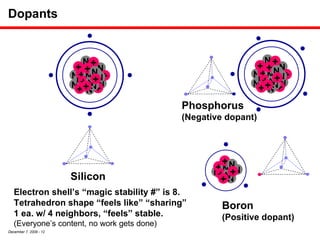

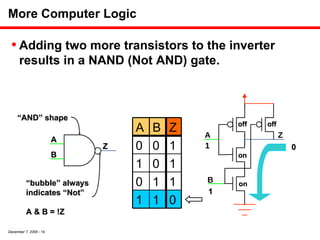

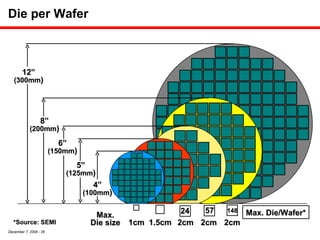

Silicon is extracted from sand and grown into crystalline ingots which are sliced into wafers. Wafers are doped with elements like boron and phosphorus to create transistors on integrated circuits. Computer-aided design (CAD) software is used to design and simulate chips before they are manufactured using photolithography to etch transistor patterns on successive wafer layers, allowing billions of transistors to fit on a single chip.