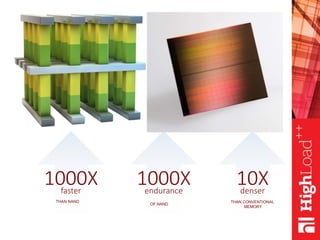

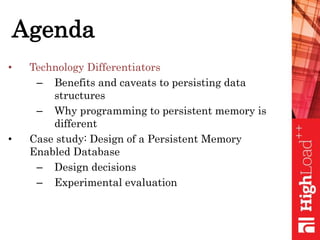

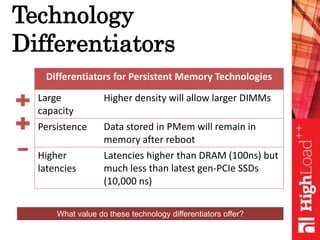

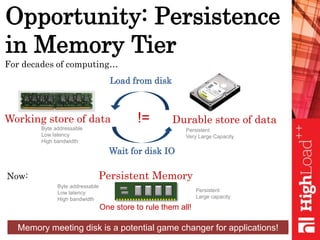

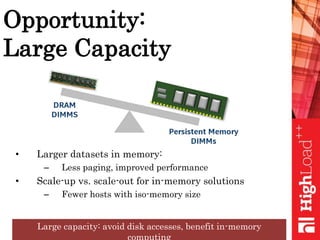

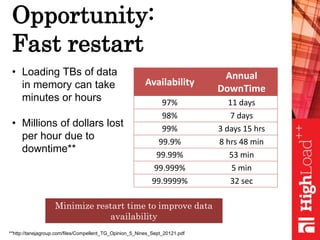

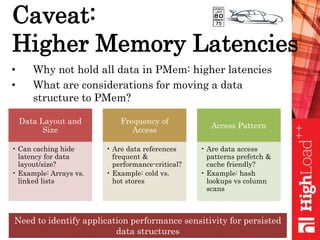

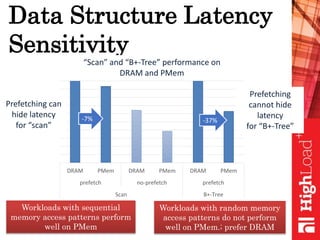

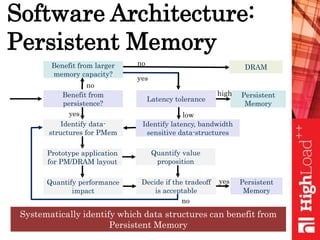

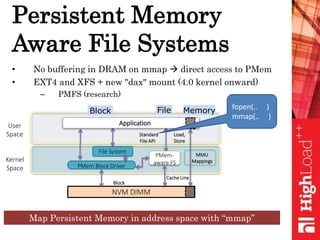

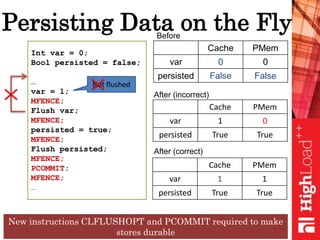

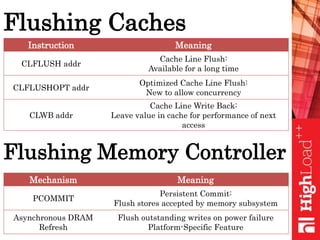

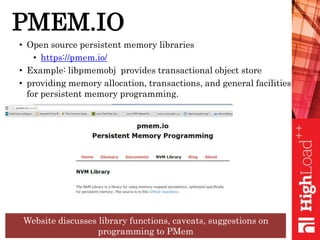

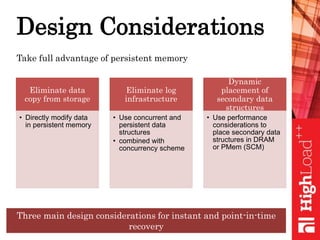

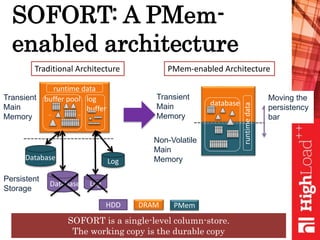

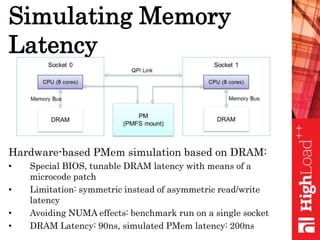

The document discusses the development of software for persistent memory by Intel, detailing the implications of utilizing persistent memory technology, including its benefits, such as improved data availability and performance, as well as challenges like higher latencies. It emphasizes the need for careful design considerations when integrating persistent memory into applications, particularly in relation to data structures and recovery processes. Additionally, it highlights available tools and libraries for programming with persistent memory, aiming to provide insights for developers on leveraging this technology effectively.