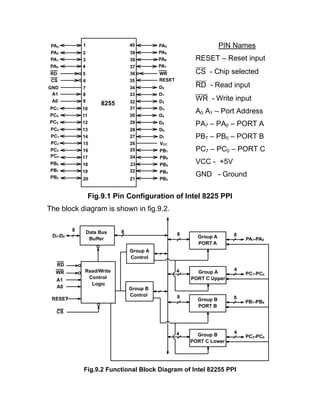

The Intel 8255A is a programmable peripheral interface chip that consists of three 8-bit I/O ports that can be configured to interface with input and output devices. Port A and B each have an output latch and input buffer, while Port C has an output latch and input buffer but can be divided into two 4-bit ports. The ports can be programmed into three modes to operate independently or for bidirectional communication. The 8255A simplifies interfacing with I/O devices by eliminating the need for external logic components like buffers and latches.