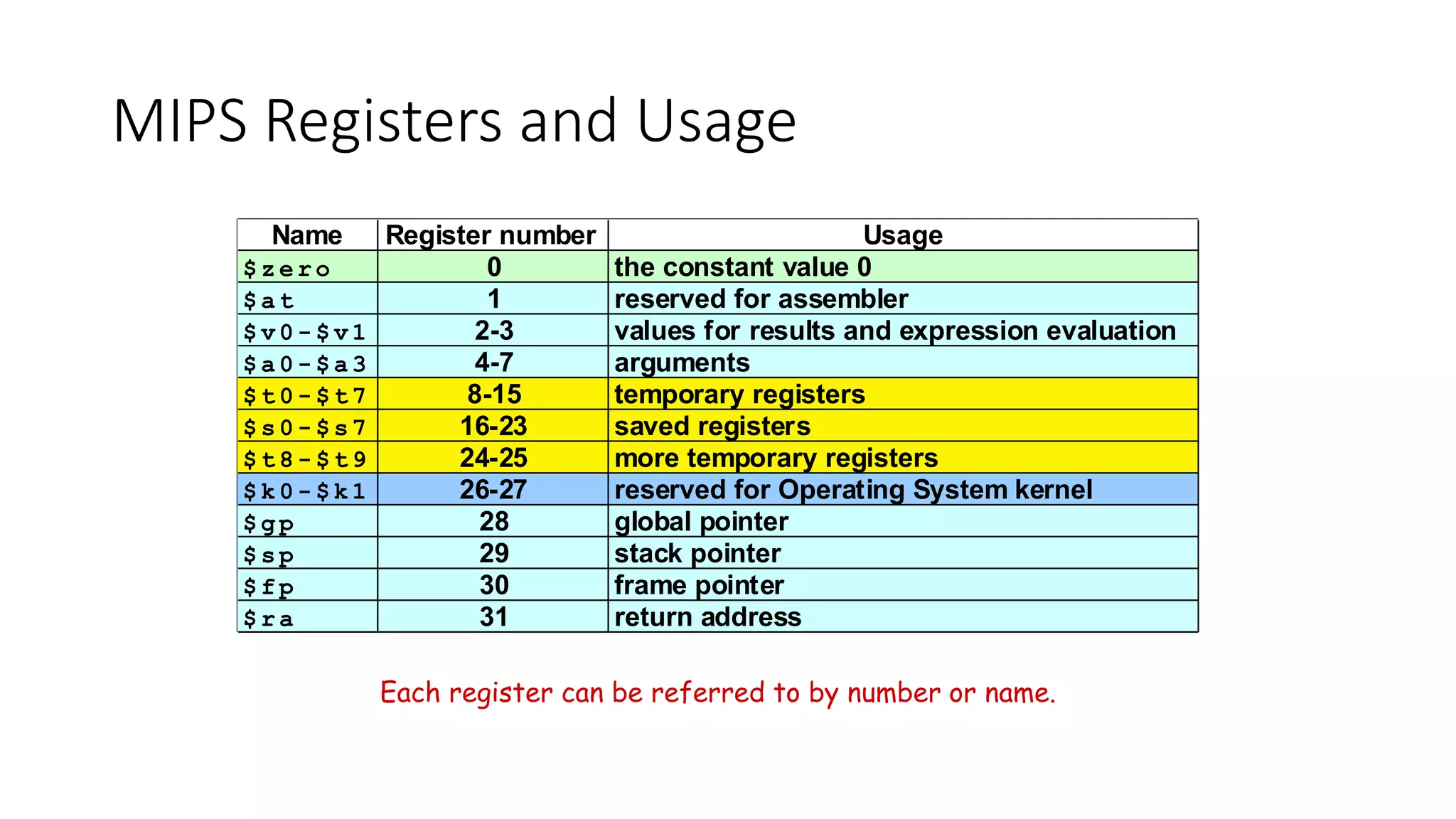

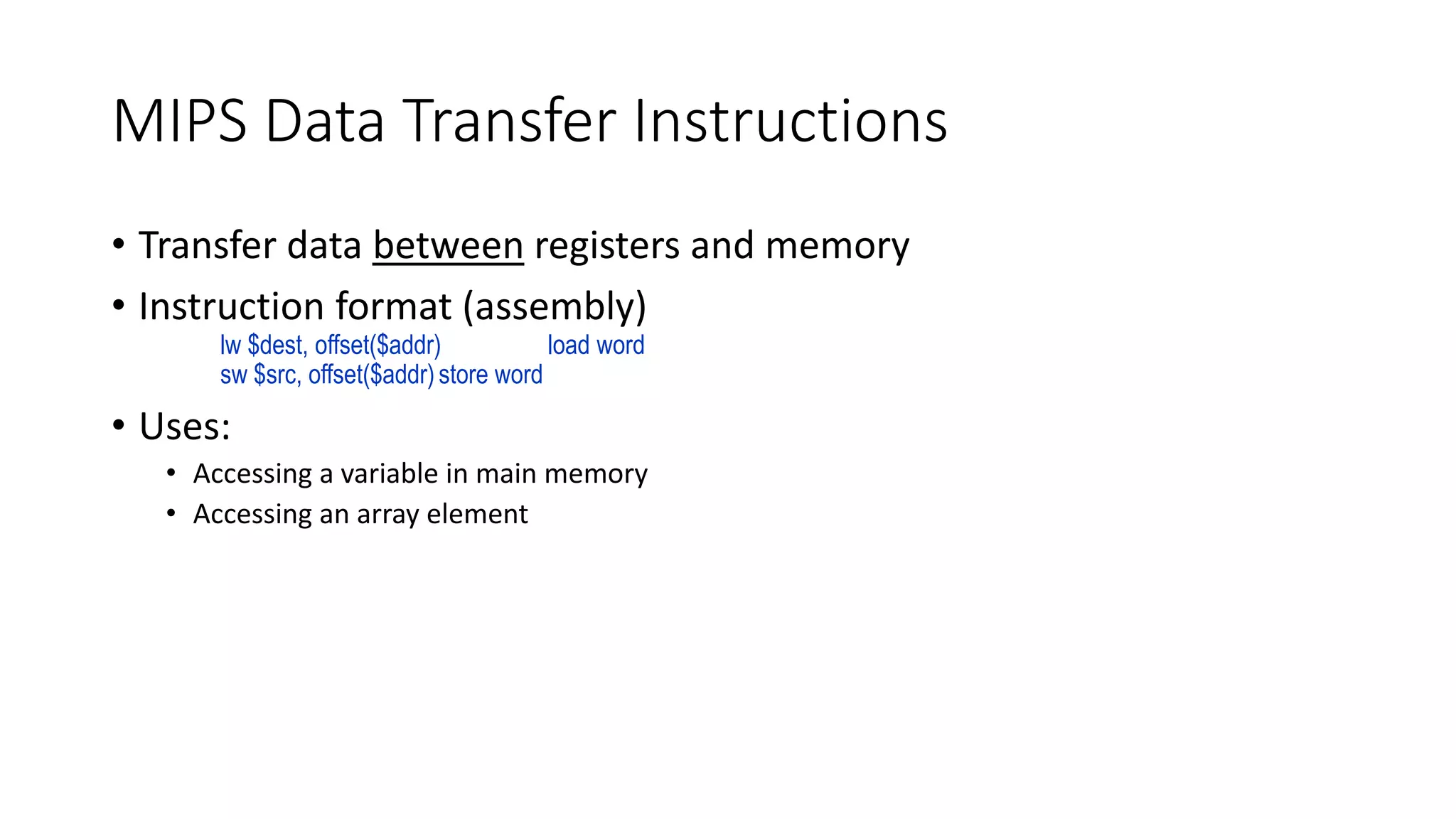

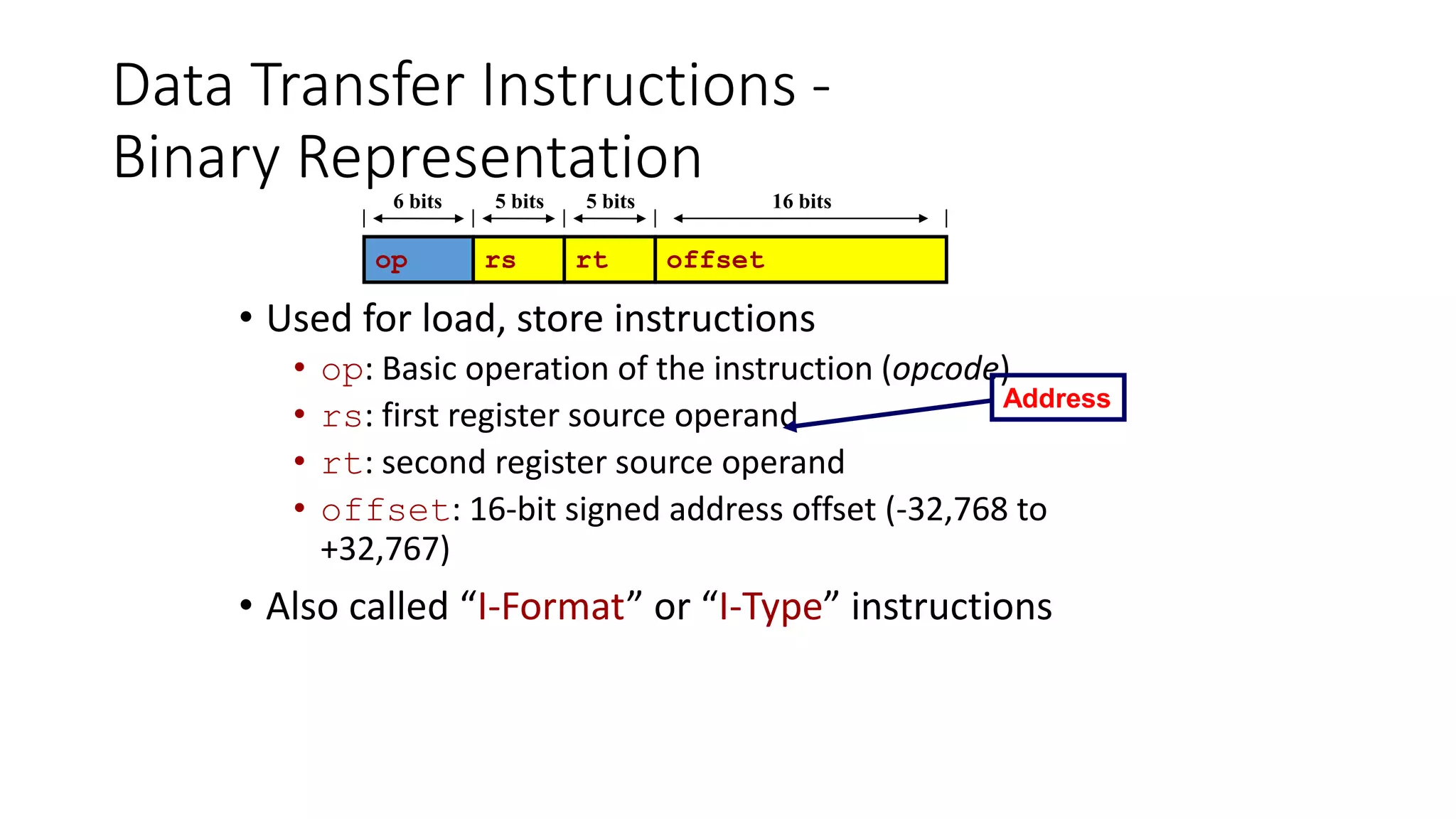

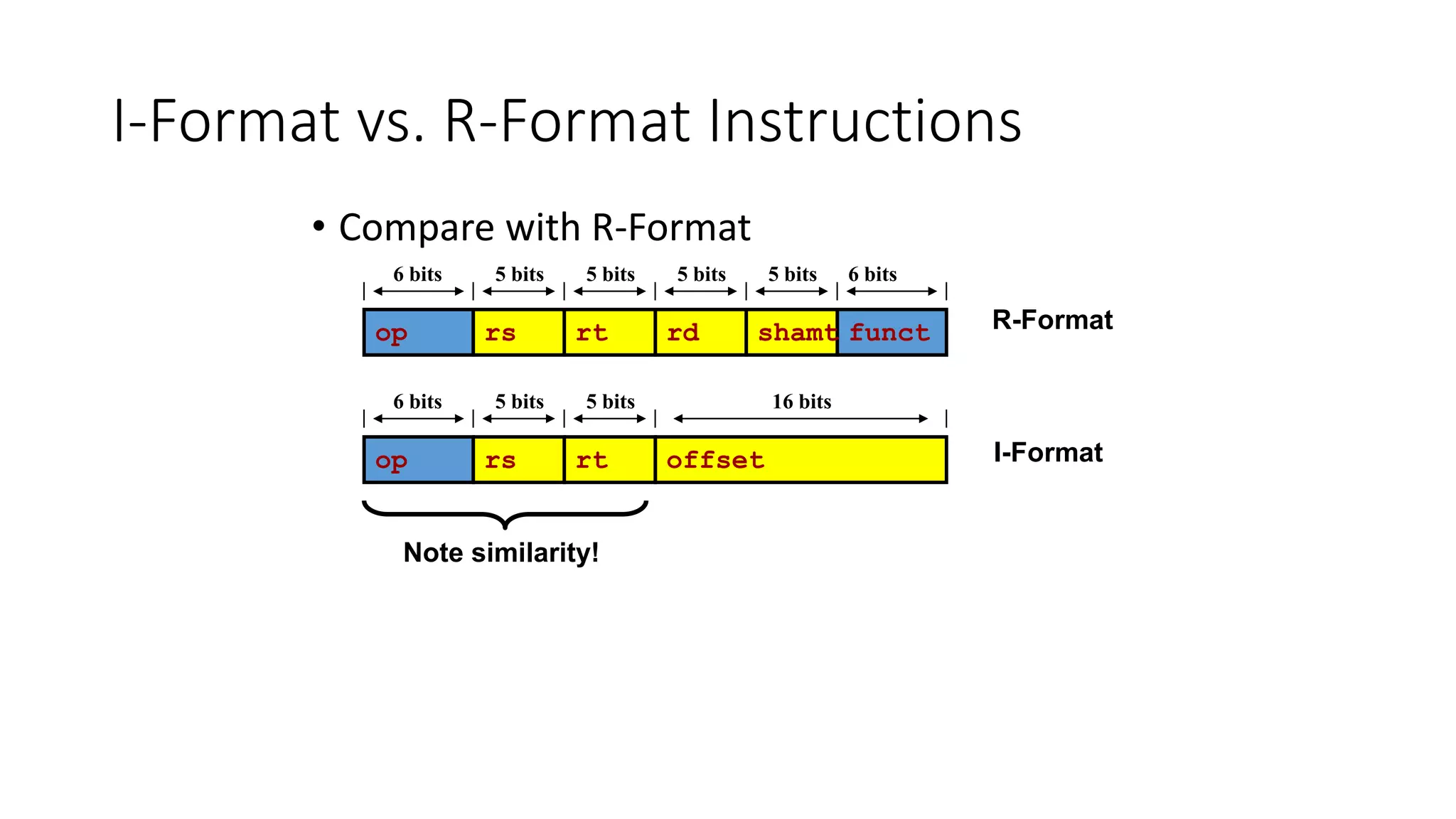

The document discusses the MIPS instruction set architecture. It describes the MIPS ISA's registers and memory organization, with 32 general purpose registers and 4GB of maximum memory addressed through bytes or words. It outlines the main instruction formats - R-format for arithmetic/logical instructions, I-format for data transfer, and J-format for jumps. The key MIPS instruction types are described, including how they manipulate data in registers or move it between registers and memory.

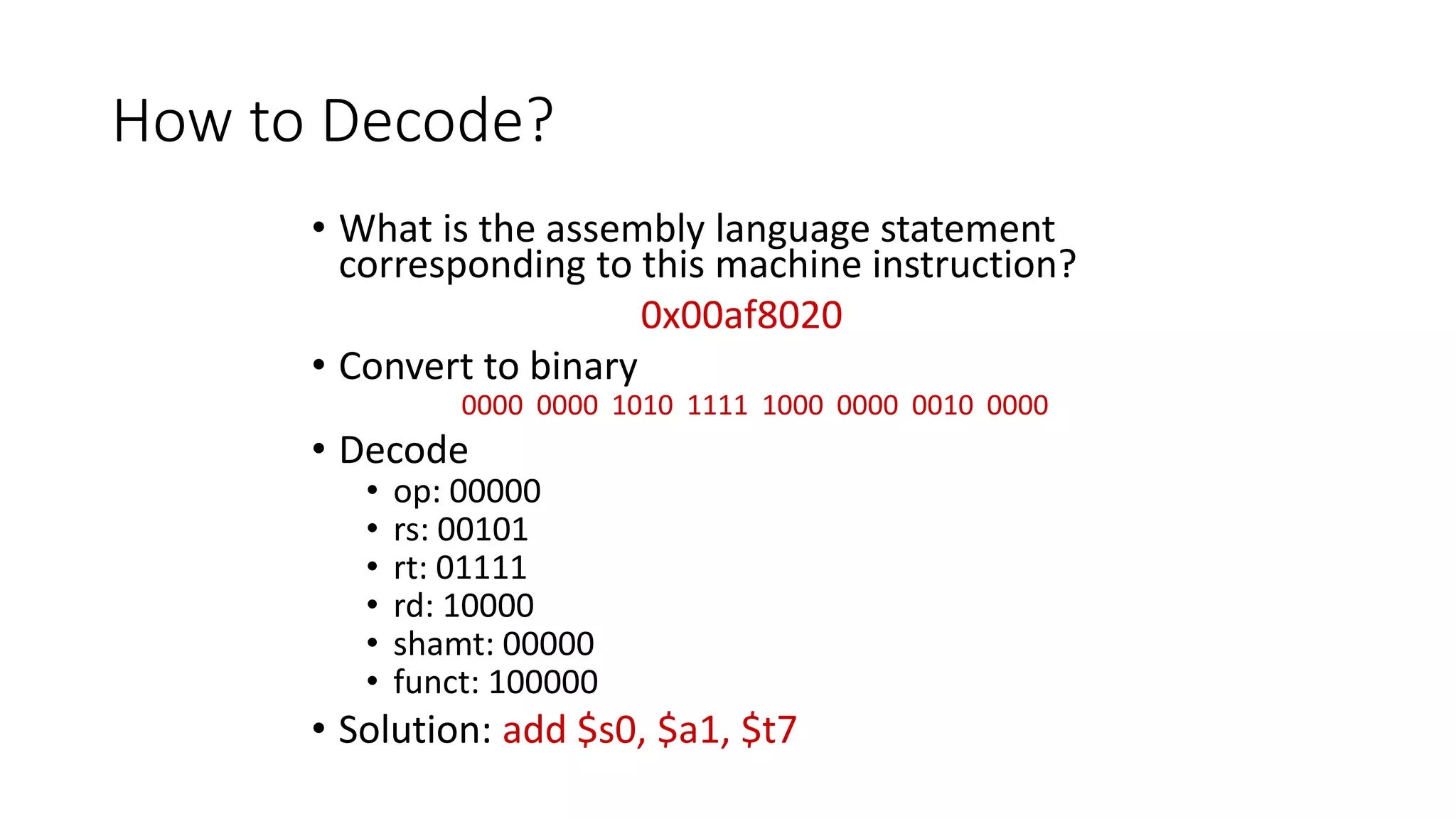

![MIPS Instruction Types

• Arithmetic & Logical - manipulate data in registers

add $s1, $s2, $s3 $s1 = $s2 + $s3

or $s3, $s4, $s5 $s3 = $s4 OR $s5

• Data Transfer - move register data to/from memory

lw $s1, 100($s2) $s1 = Memory[$s2 + 100]

sw $s1, 100($s2) Memory[$s2 + 100] = $s1

• Branch - alter program flow

beq $s1, $s2, 25 if ($s1==$s1) PC = PC + 4 + 4*25](https://image.slidesharecdn.com/06-mips-isa-150514011434-lva1-app6892/75/06-mips-isa-9-2048.jpg)

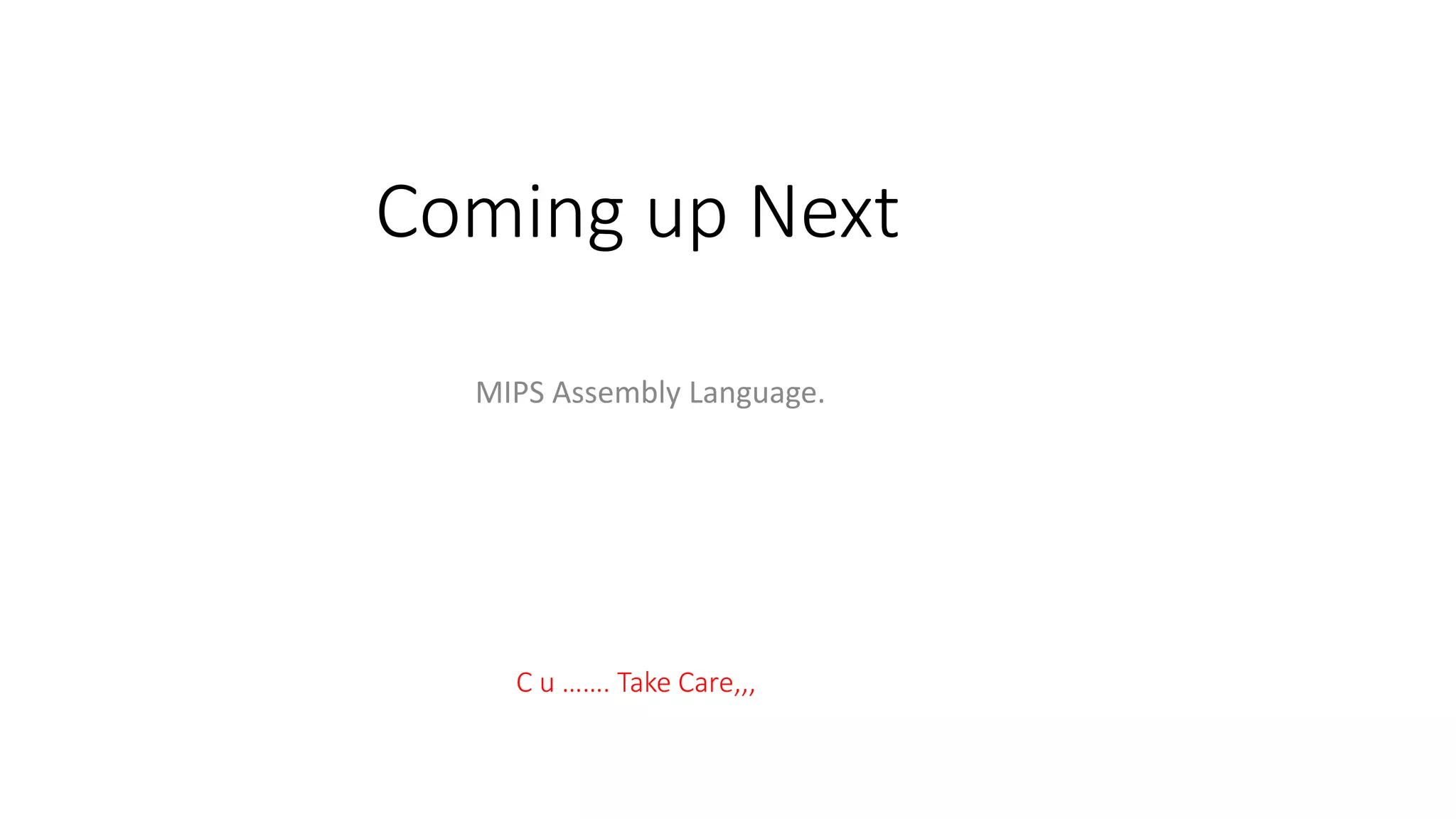

![Data Transfer Example - Array Variable

Registers

R0=0 (constant)

R1

R2=0x08

R30

R31

R3

R4

R5=105

C Program: int a[5];

a[3] = z;

Assembly: sw $5,12($2)

12=0xc

+

Memory

0x00

a[0]

a[4]

a[2]

a[1]

a[3]

0x04

0x08

0x0c

0x10

0x14

0x18

0x1c

Base Address

R5=105

R2=0x08

a[3]=105

scaled offset](https://image.slidesharecdn.com/06-mips-isa-150514011434-lva1-app6892/75/06-mips-isa-15-2048.jpg)

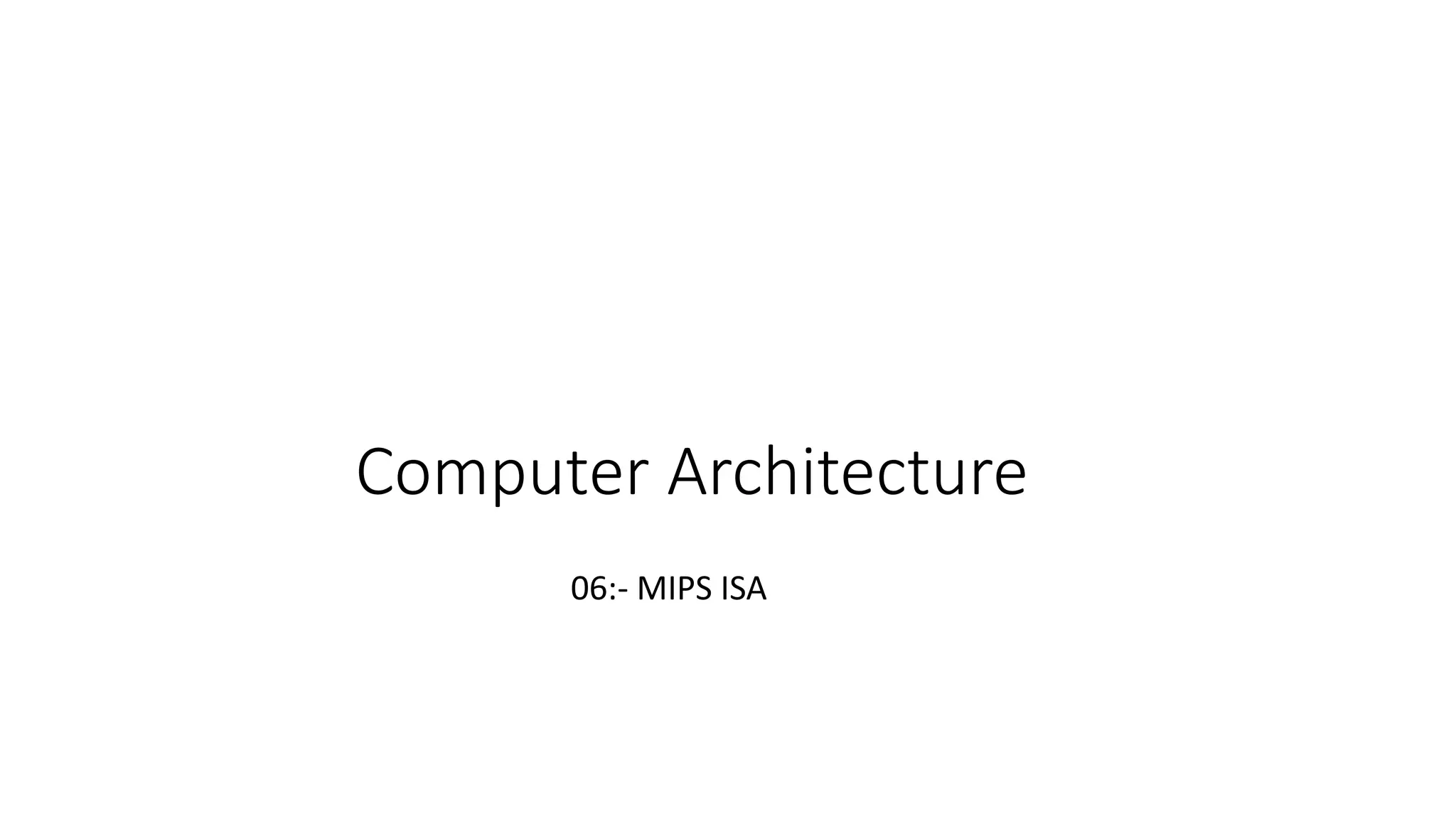

![Binary Representation - Jump

• Jump Instruction uses J-Format (op=2)

• What happens during execution?

PC = PC[31:28] : (IR[25:0] << 2)

op address

6 bits 26 bits

Conversion to

word offset

Concatenate

upper 4 bits

of PC to form

complete

32-bit address](https://image.slidesharecdn.com/06-mips-isa-150514011434-lva1-app6892/75/06-mips-isa-19-2048.jpg)