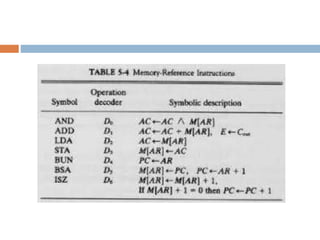

The document discusses seven different memory reference instructions used in a computer system. The instructions include AND to AC, ADD to AC, LDA, STA, BUN, BSA, and ISZ. Each instruction requires a sequence of microoperations to read data from memory into a register, perform the operation, and update registers or memory. For example, the LDA instruction reads the memory word specified by the effective address into the data register in T4, then transfers this value to the accumulator in T5 before clearing the sequence counter.

![ AND to AC

Performs the AND logic operations on pairs of bits

in AC and the memory word specified by the

effective address

Two timing signals are needed

• In T4 transfering operand from memory into DR

• In T5 transfering result of AND logic operation

between the contents of DR and AC

• In T5 SC is cleared to 0 and control is transfered

to T0 to start a new instruction cycle

Example:

• D0T4 : DR←M[AR]

• D0T5 : AC←AC∧ DR, SC←0](https://image.slidesharecdn.com/memoryreference-191009135603/85/Memory-reference-5-320.jpg)

![ ADD to AC

Adds the contents of memory word specified

by the effective address to the value of AC

Sum is transferred into AC and the output carry

Cout is transferred to the E(extended

accumulator) flip flop

Two timing signals are needed but decoder D1

instead of D0

Example:

• D1T4 : DR←M[AR]

• D1T5 : AC←AC+DR, E←Cout SC←0](https://image.slidesharecdn.com/memoryreference-191009135603/85/Memory-reference-6-320.jpg)

![ LDA:Load to AC

Transfers the memory word specified by the

effective address to AC

Necessary to read the memory word into DR

first and transfer the contents of DR into AC

there is no direct path from bus into AC

to maintain one clock cycle as well

Example:

D2T4 : DR←M[AR]

D2T5 : AC←DR SC←0](https://image.slidesharecdn.com/memoryreference-191009135603/85/Memory-reference-7-320.jpg)

![ STA:Store AC

Stores the content of AC into the

memory word specified by the

effective address

The output of AC is applied to the

bus and the data input of memory is

connected to the bus

Example:

D3T4 : M[AR]←AC, SC←0](https://image.slidesharecdn.com/memoryreference-191009135603/85/Memory-reference-8-320.jpg)

![ ISZ:Increment and Skip if Zero

Increments the word specified by the effective address

If the incremented value is equal to 0, PC is incremented by 1

When a negative number(in 2's compelement) stored in memory

word is repeatedy incremented by 1 it eventually reaches zero

At this time PC is incremented by one in order to skip the next

instruction in the program

It is necessary to read the word into DR, increment DR and store

the word back into memory since it is not possible to increment a

word inside the memory

Example:

D6T4 : DR←M[AR]

D6T5 : DR←DR+1

D6T6 : M[AR] ← DR, if (DR=0) then (PC←PC+1), SC←0](https://image.slidesharecdn.com/memoryreference-191009135603/85/Memory-reference-11-320.jpg)