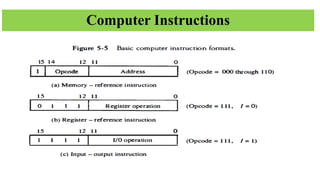

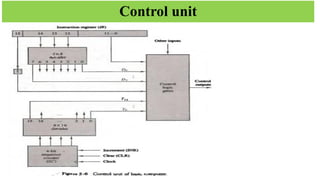

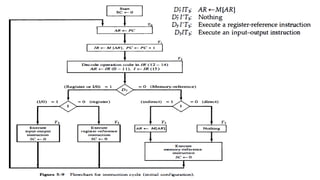

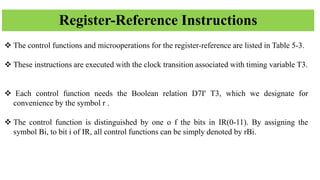

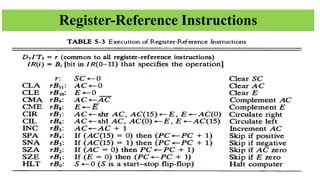

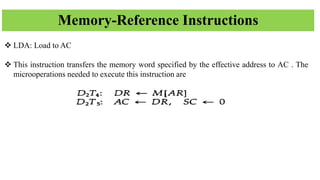

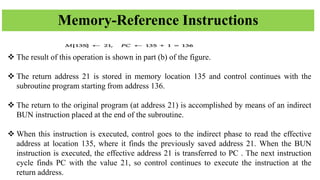

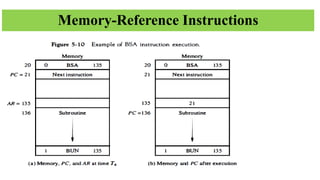

The document describes the instruction cycle process in a computer. It is divided into phases: fetch, decode, execute. Each instruction goes through this cycle. The phases are further divided into subcycles where the control unit determines the instruction type (register, memory, I/O), then performs the appropriate operations like fetching from memory, arithmetic/logic operations, and branching. Memory instructions include AND, ADD, LOAD, BRANCH etc. Register instructions modify registers directly. Subroutines are implemented using branch-and-save and indirect branch instructions.