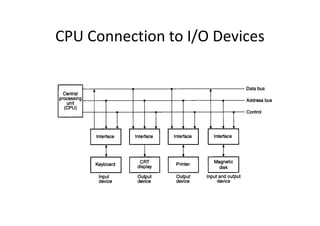

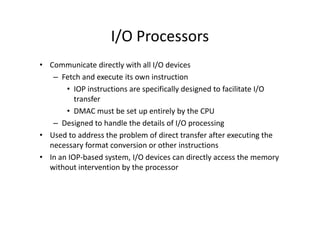

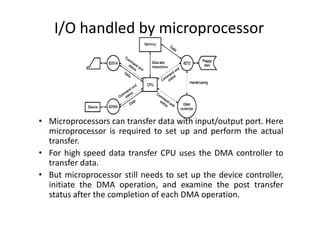

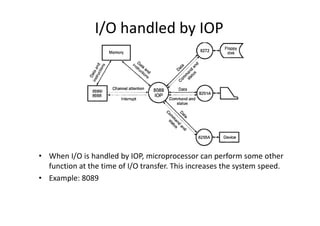

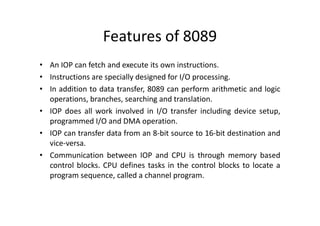

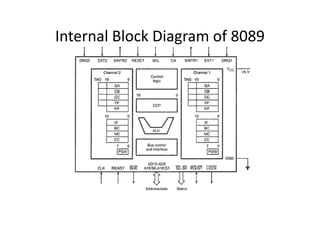

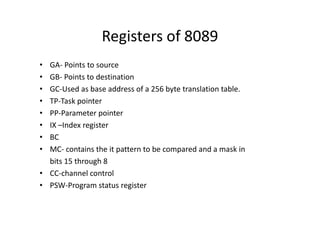

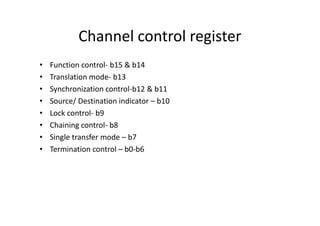

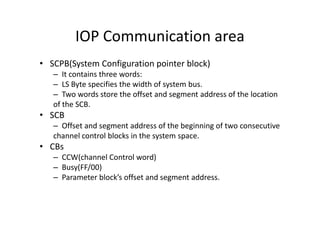

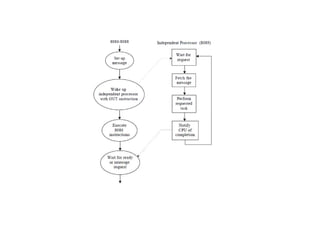

The document discusses the role and functionality of the 8089 I/O processor in managing interactions between input/output devices and the CPU. It highlights how the I/O processor relieves the CPU from input/output chores by directly handling device communication, data transfers, and execution of its own instructions, thereby improving system speed. Additionally, the I/O processor supports various commands for data transfer, arithmetic operations, and hardware control.