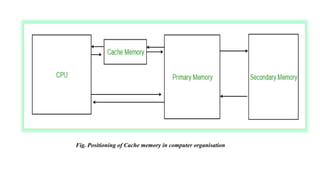

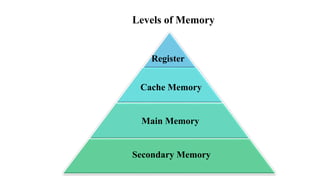

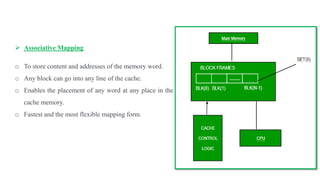

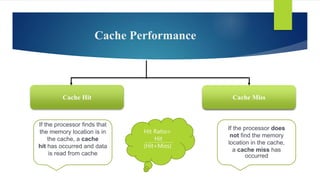

Cache memory is a high-speed memory located between the CPU and main memory that acts as a buffer to improve access time. There are three types of cache mapping: direct mapping maps each memory block to a single cache line; associative mapping allows any memory block to be placed in any cache line; and set-associative mapping groups lines into sets and allows blocks to map to any line within a set. The performance of cache is determined by the hit ratio, which is the number of hits divided by the total number of memory accesses.