- ARM was developed in 1983 by Acorn Computers with a 4-man team to replace the 6502 processor in BBC computers. It has since become one of the most widely used processor cores in the world due to its simplicity, low power consumption, and use in portable devices.

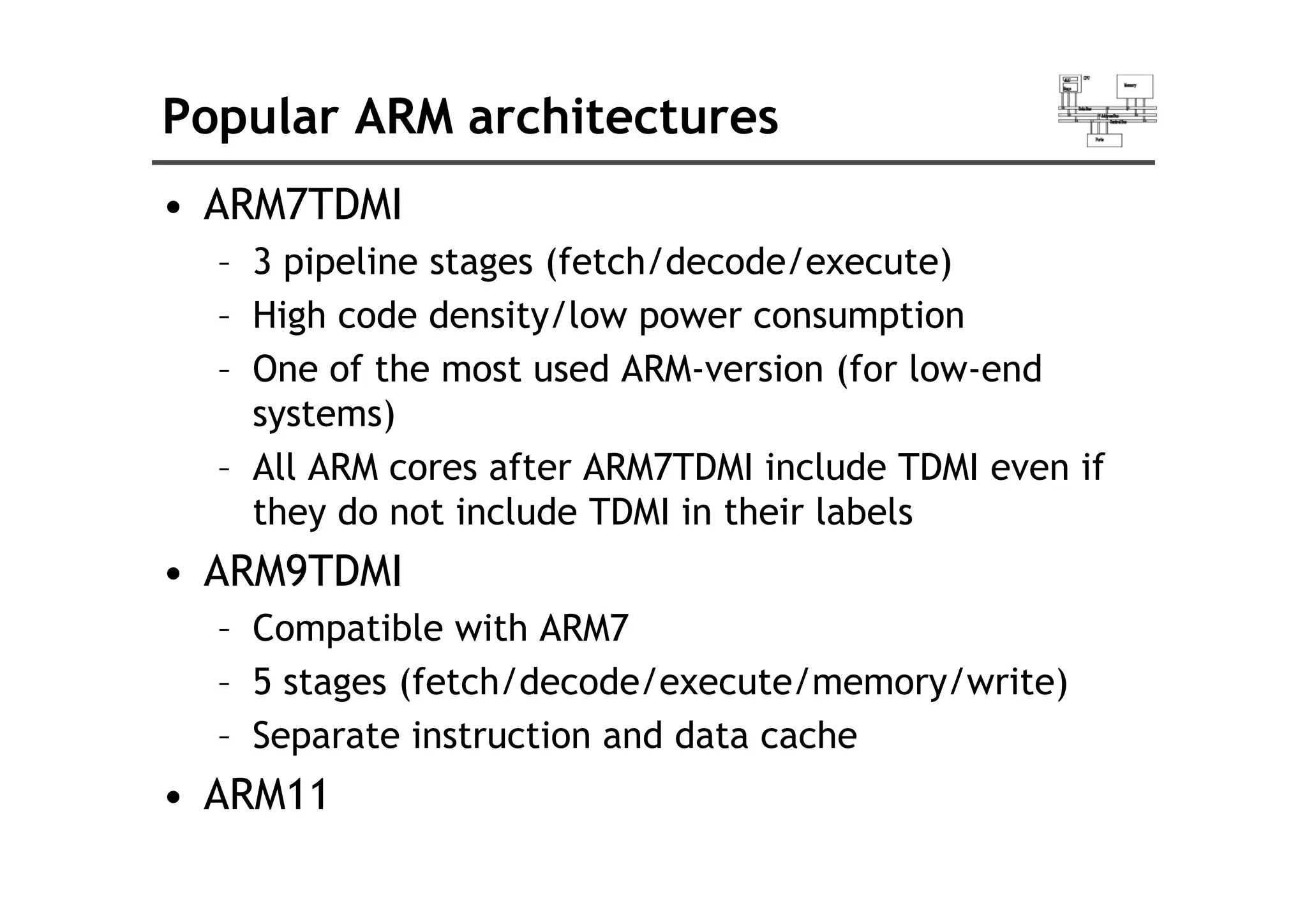

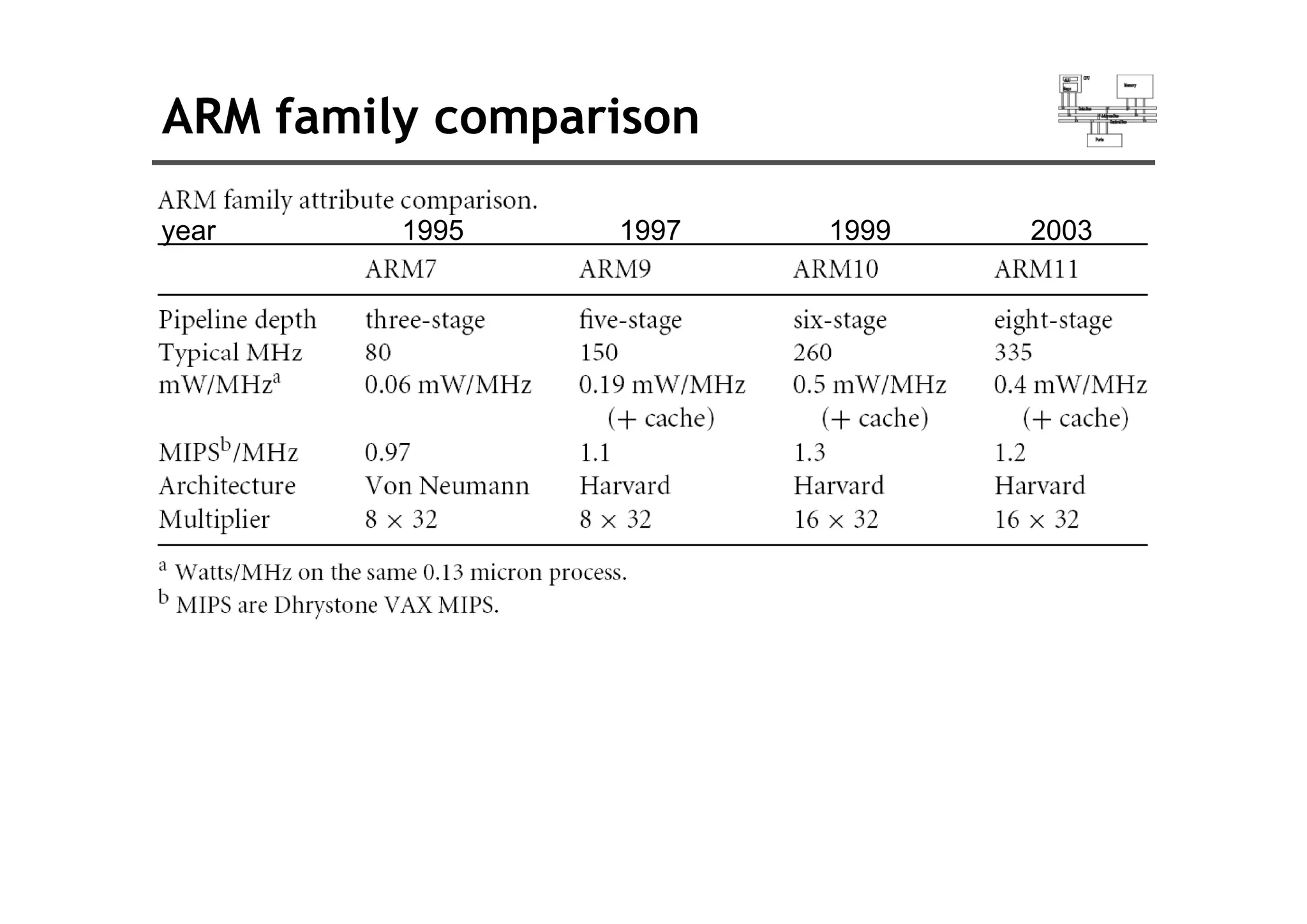

- ARM Holdings licenses the ARM processor core designs to manufacturers but does not manufacture the chips itself. ARM cores power many products including PDAs, phones, media players, handheld game consoles, digital cameras, and more. Popular ARM architectures include ARM7TDMI and ARM9TDMI.

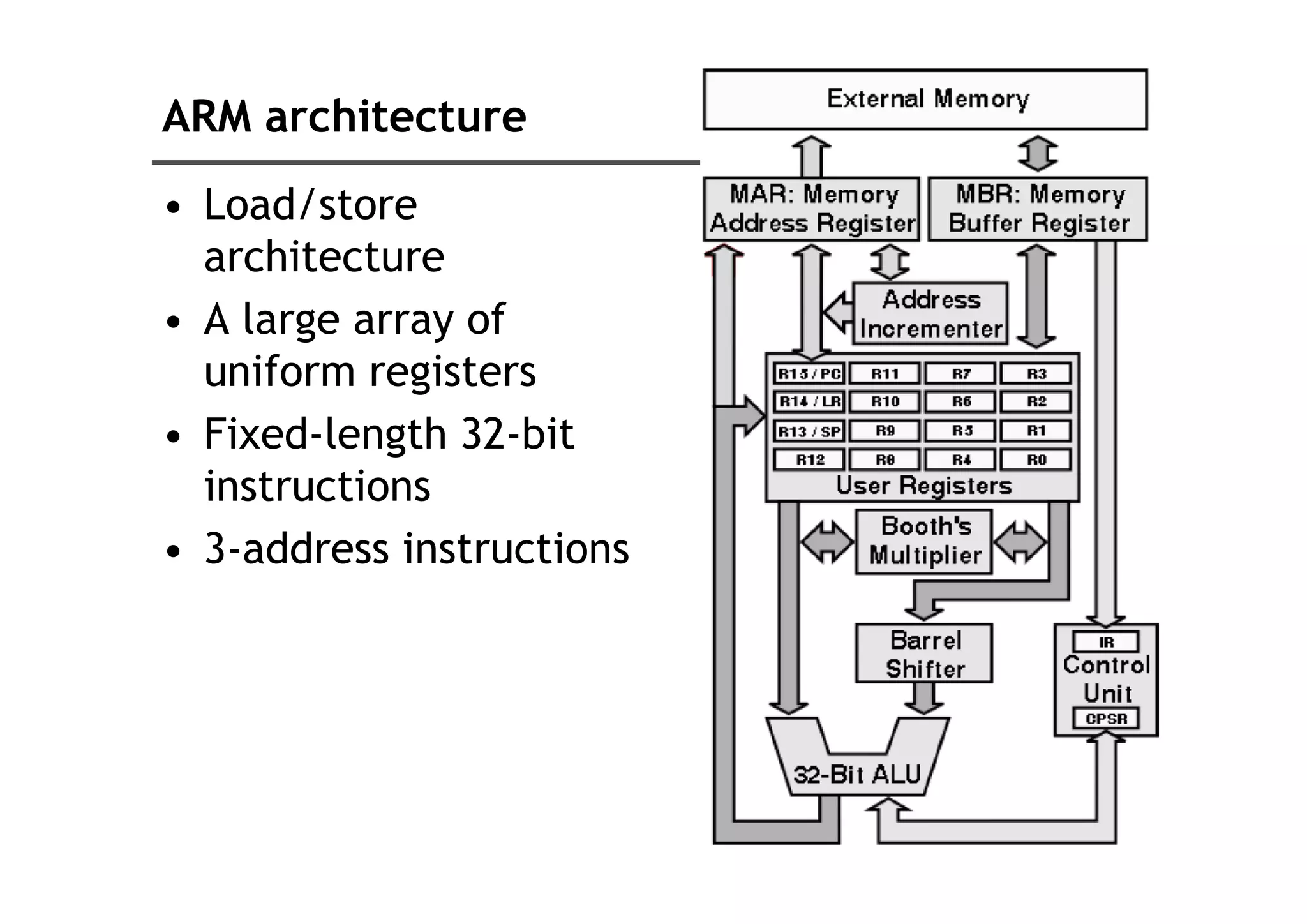

- The ARM architecture uses a load/store design with 32-bit fixed-length instructions operating on a large number of general purpose