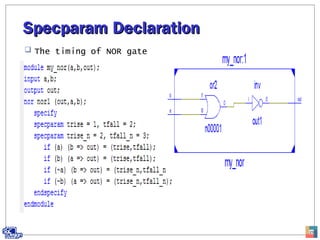

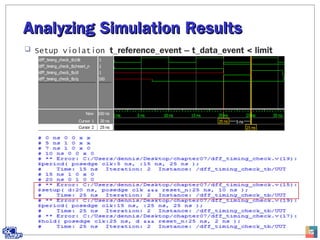

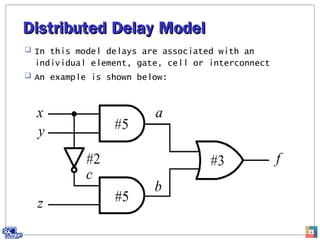

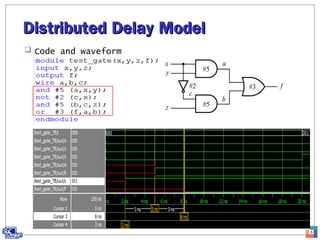

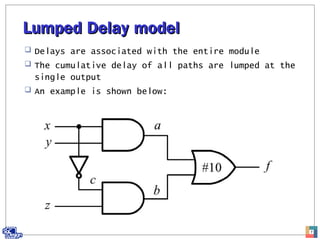

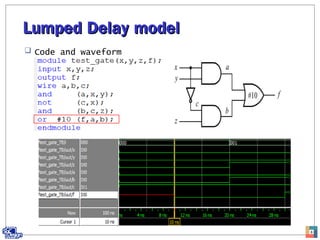

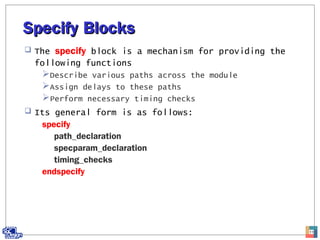

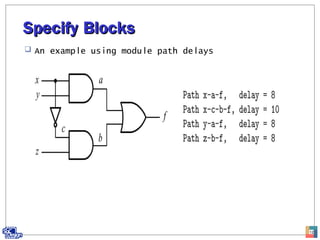

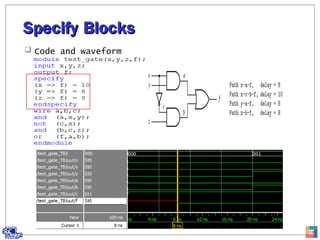

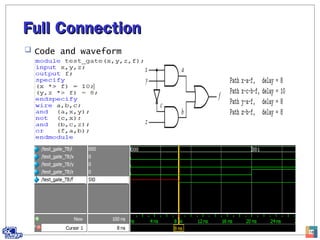

The document discusses three delay models - distributed, lumped, and path delay models. It also describes specify blocks which are used to describe module paths, assign delays, and perform timing checks. Common timing checks include setup, hold, width, period, and skew checks. An example of a D flip-flop model with timing checks is presented and the simulation results analyzing violations are discussed.

![Specparam DeclarationSpecparam Declaration

It is used to define specify parameters which are

intended to provide timing and delay

It has the general form as below:

specparam [range] specparam_assignment;

22](https://image.slidesharecdn.com/advancedmodelingtechniques-140718050745-phpapp01/85/Advanced-modeling-techniques-22-320.jpg)