Embed presentation

Download to read offline

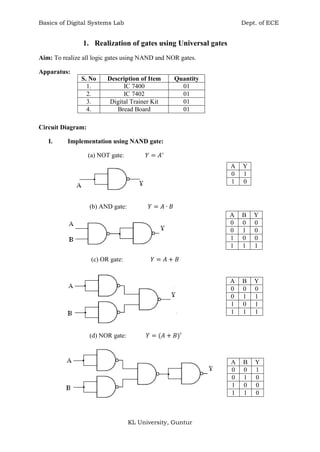

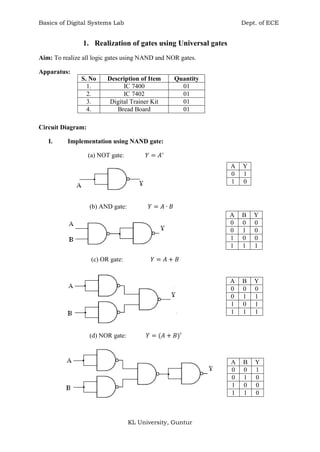

This document provides information about realizing logic gates using universal gates. It describes implementing NOT, AND, OR, NOR, XOR, and XNOR gates using only NAND gates and again only using NOR gates. The apparatus used includes IC 7400, IC 7402, a digital trainer kit, and a breadboard. Truth tables are given for each gate realization.