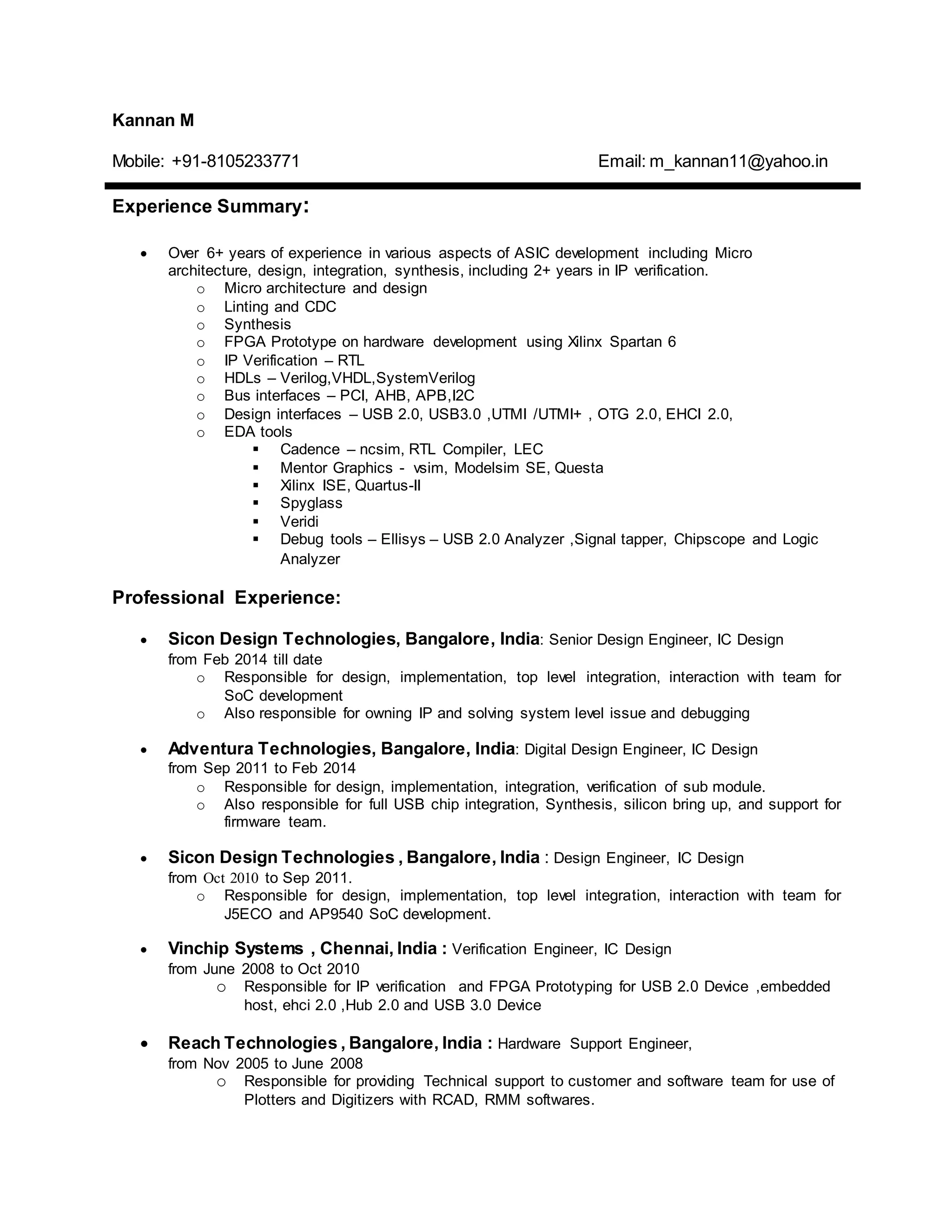

Kannan M has over 6 years of experience in ASIC development including microarchitecture design, IP verification, synthesis, and FPGA prototyping. He has worked on USB controller designs such as OTG, USB 2.0/3.0 hubs and devices, and embedded USB hosts. His responsibilities included RTL design, integration, verification using simulation and FPGA prototyping, and customer support. He is proficient with Verilog, VHDL, and EDA tools from Cadence, Mentor Graphics, and Xilinx.