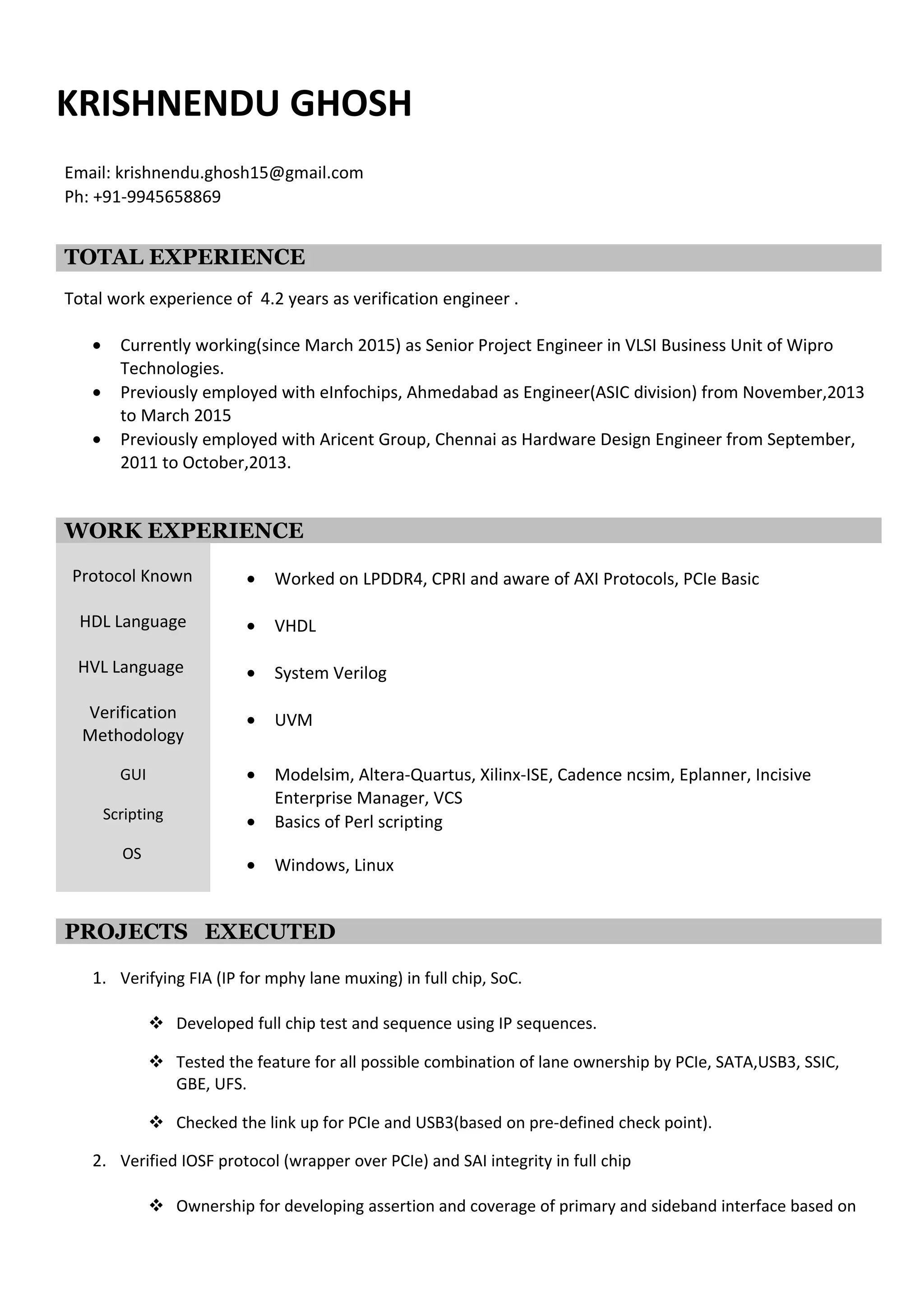

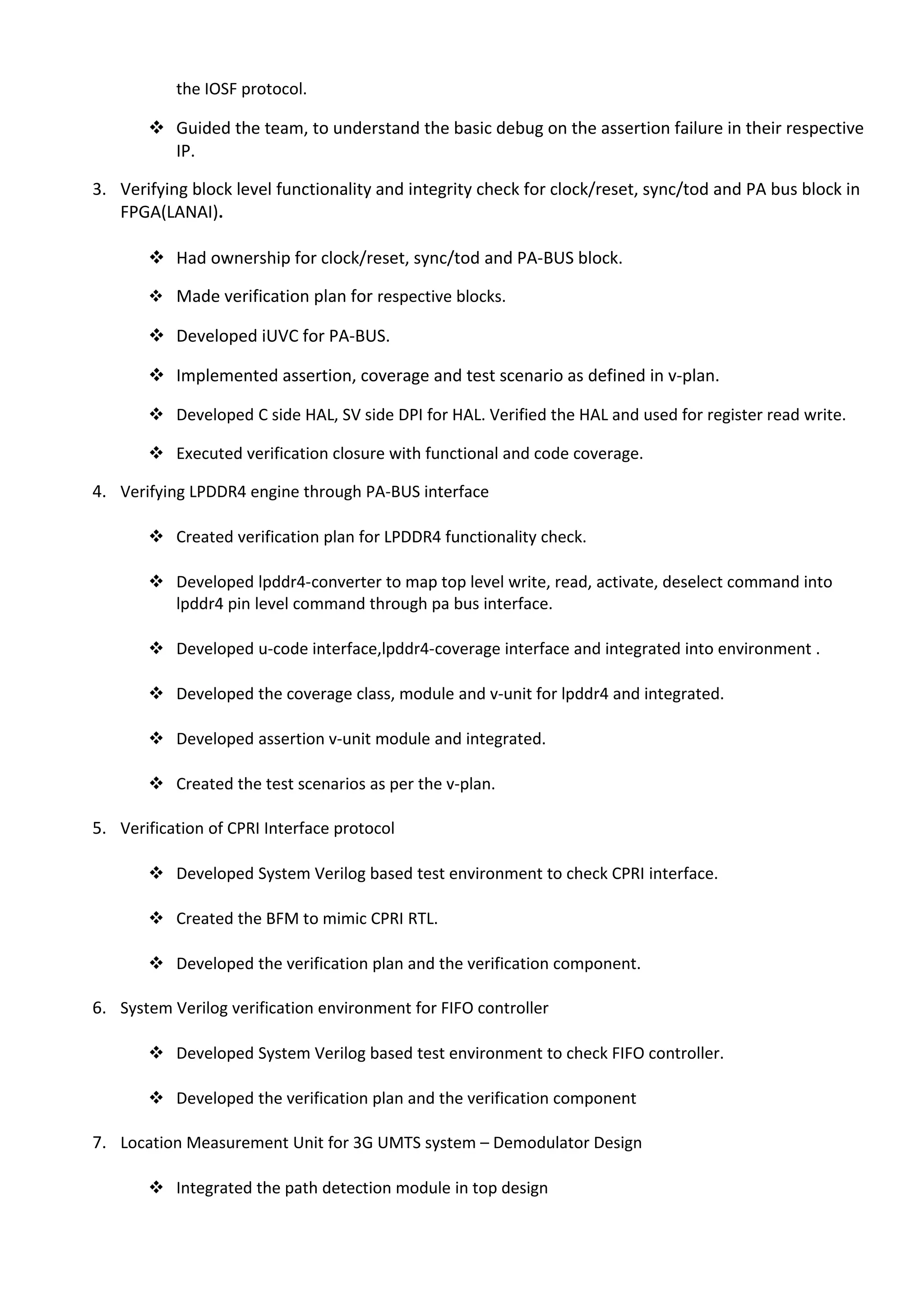

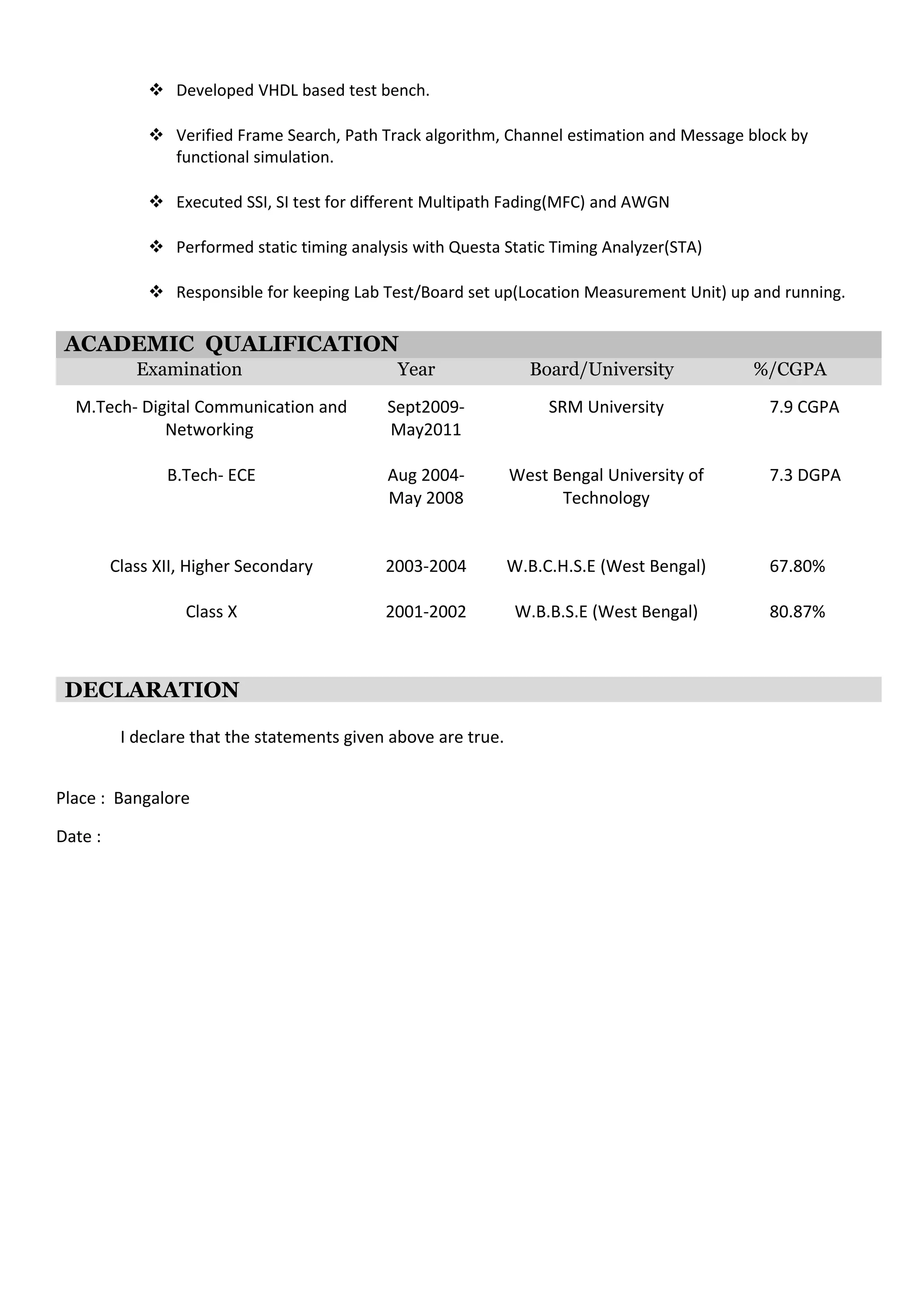

This document contains a summary of Krishnendu Ghosh's work experience and qualifications. It outlines his 5 years of experience as a verification engineer, including current and previous roles at Wipro Technologies, eInfochips, and Aricent Group. It provides details on the protocols, languages, and tools he has experience with for verification. It also summarizes 7 projects he has worked on related to verifying IP blocks, interfaces, and controllers using UVM and SystemVerilog. The document concludes with his academic qualifications, including an M.Tech in Digital Communication and Networking from SRM University and a B.Tech in ECE from West Bengal University of Technology.