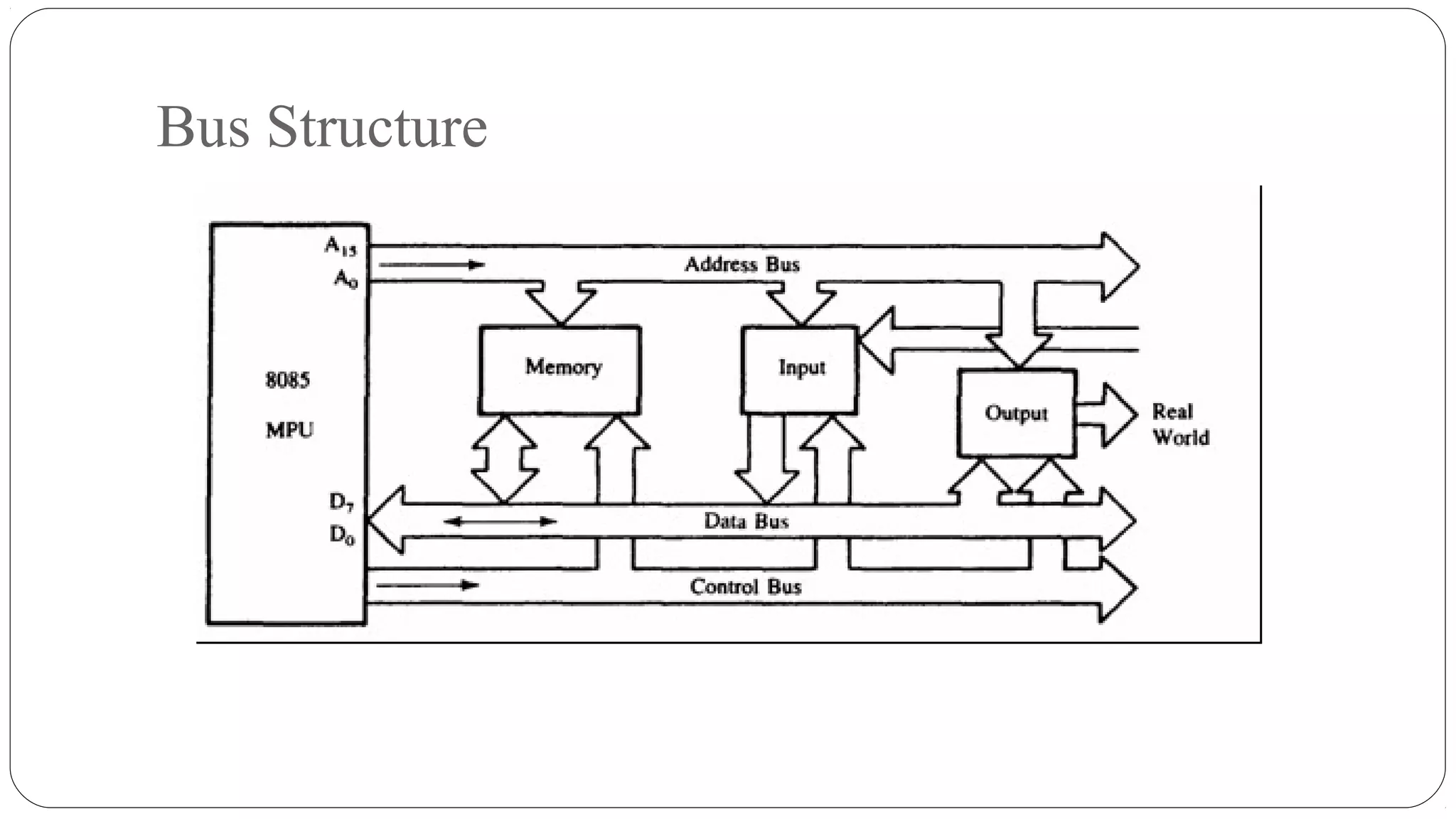

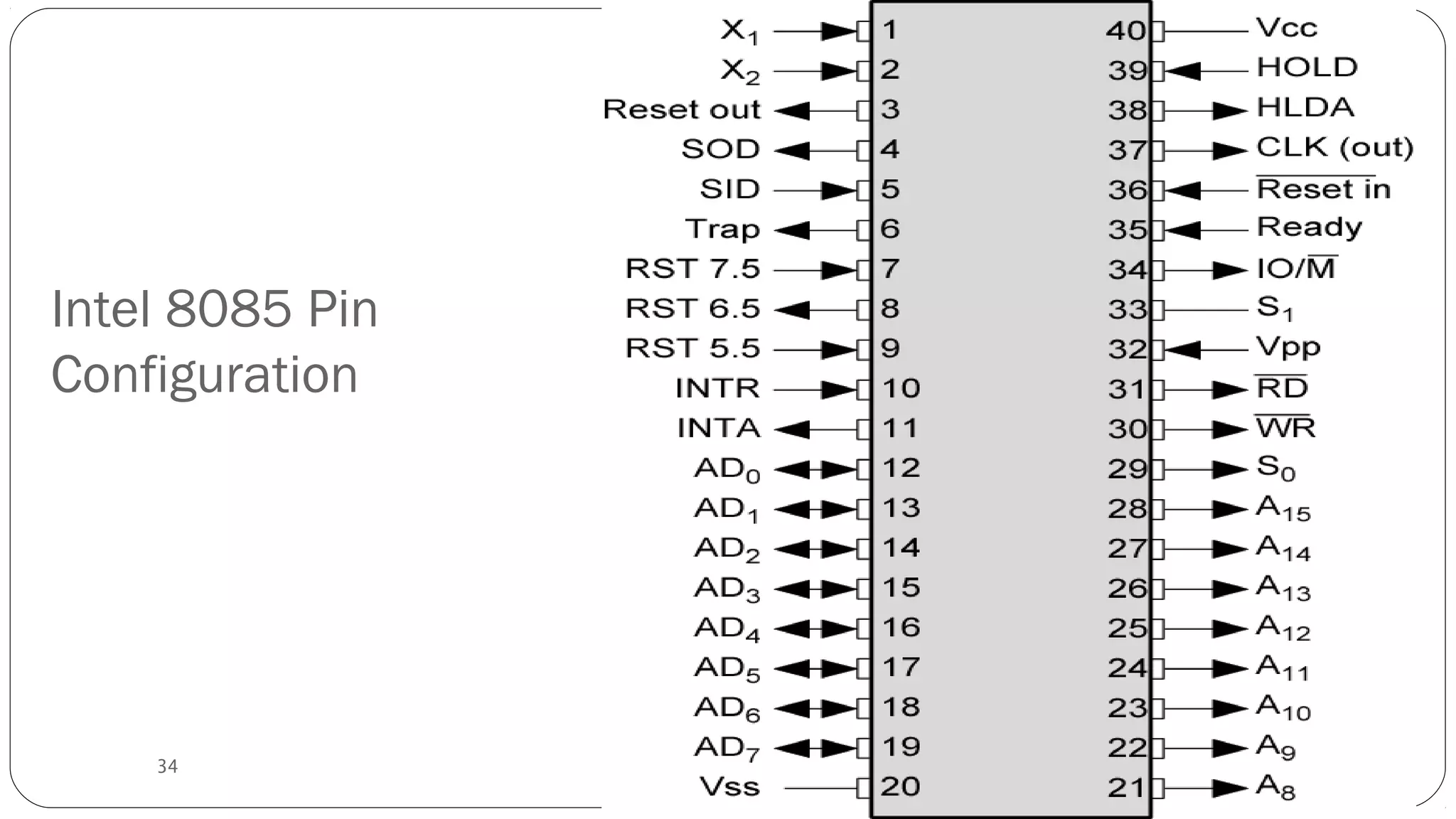

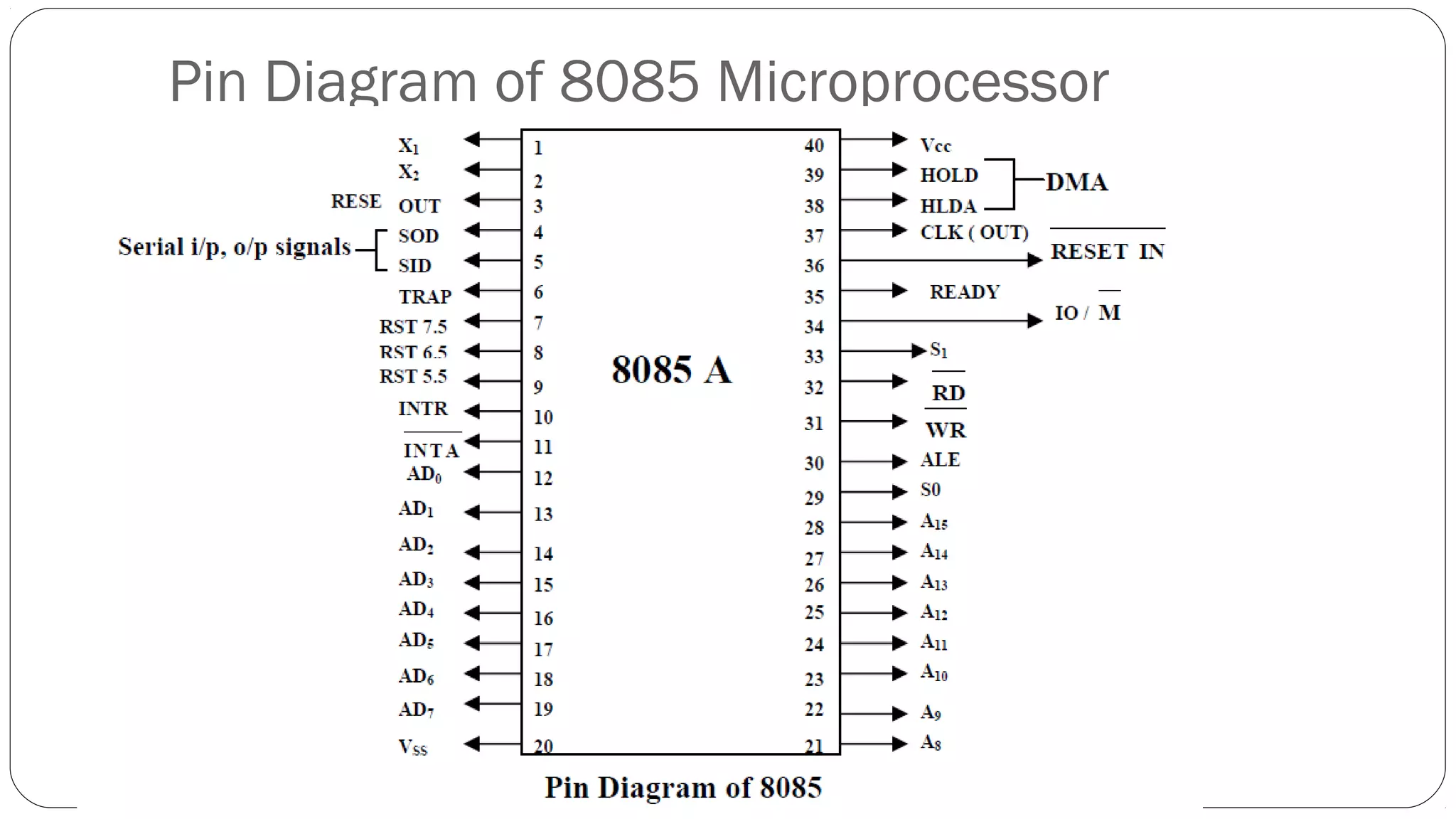

The 8085 microprocessor is an 8-bit CPU with 40 pins that can address up to 64KB of memory and operate at speeds up to 3MHz. It has various internal registers like the accumulator, flag register, instruction register and program counter. It uses an ALU to perform arithmetic and logical operations. The 8085 has an 8-bit data bus and 16-bit address bus to interface with external memory and I/O devices. It uses control signals like ALE, RD, WR and I/O/M to control data transfers. The pinout includes power, clock, interrupt pins and reset signals.