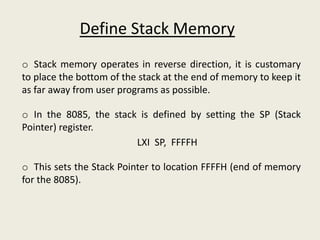

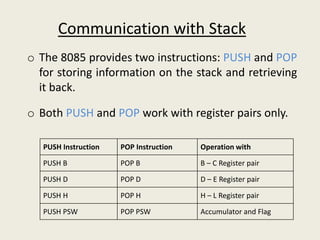

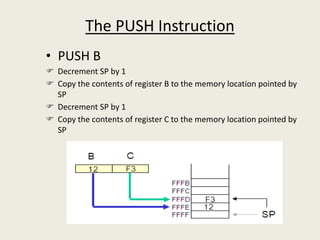

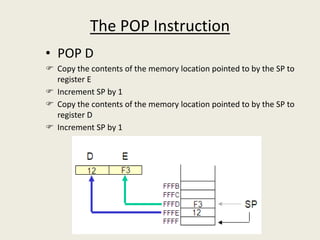

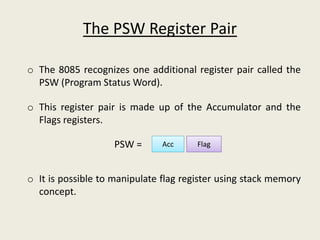

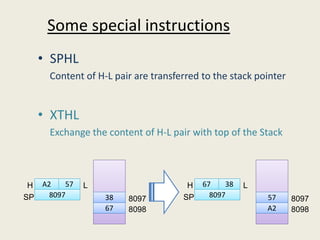

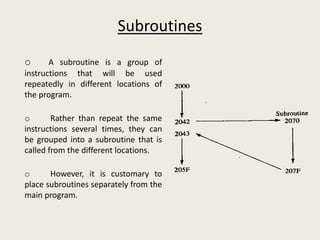

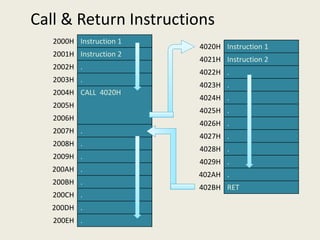

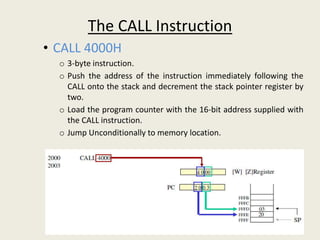

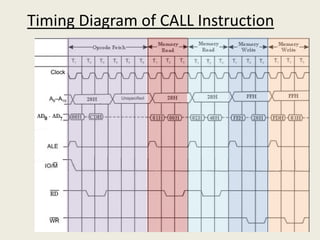

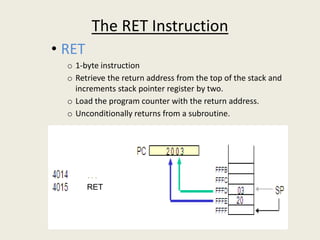

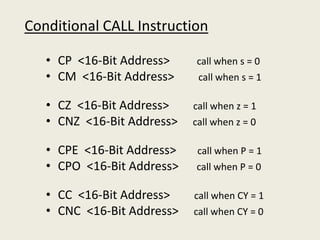

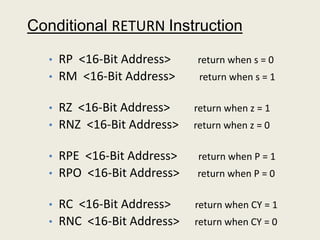

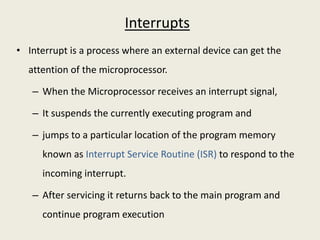

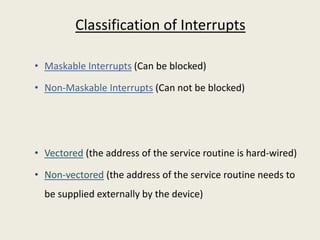

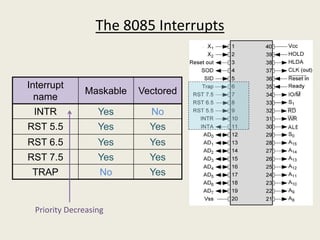

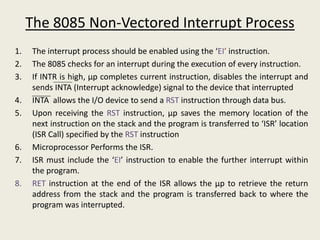

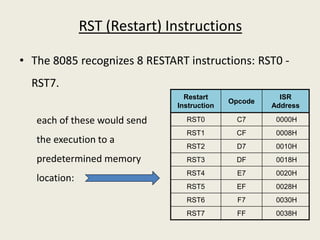

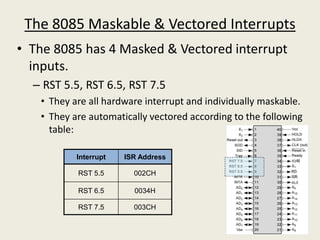

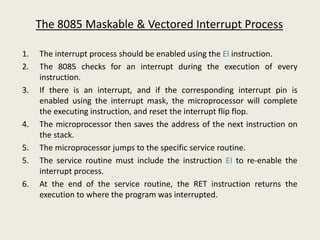

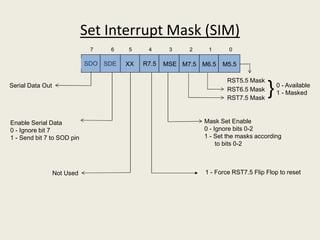

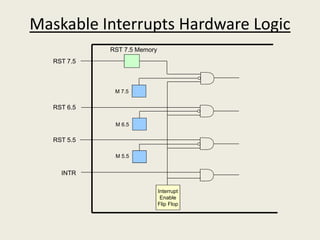

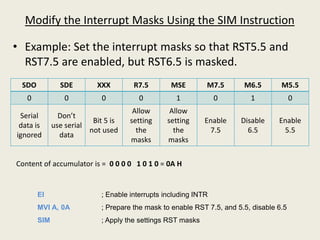

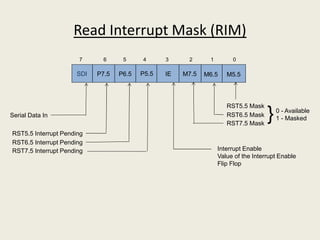

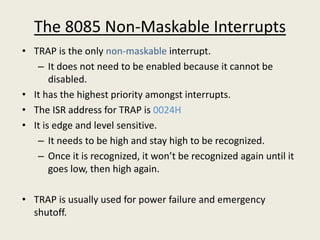

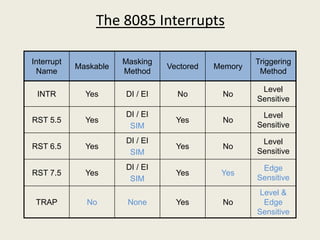

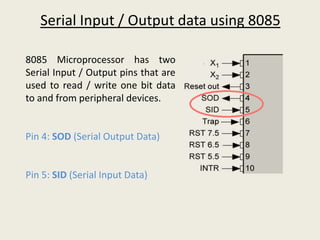

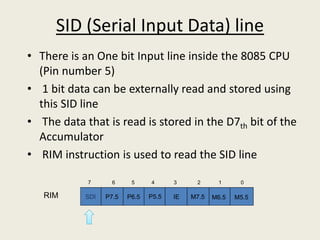

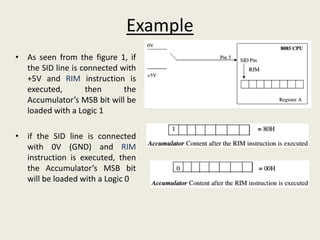

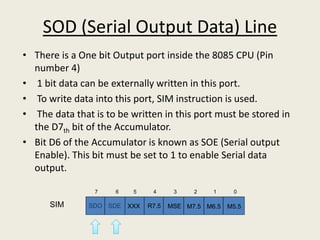

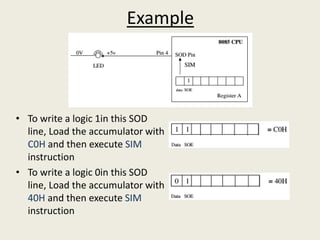

The document discusses stack and subroutine operations, interrupts, and serial communication in 8085 microprocessors. It describes the LIFO structure of the stack and how it uses PUSH and POP instructions. It also explains subroutines using CALL and RET instructions. For interrupts, it covers maskable, non-maskable, vectored and non-vectored interrupts and their priorities. It provides details on interrupt handling instructions. Finally, it discusses serial input/output using SID and SOD pins and RIM/SIM instructions.