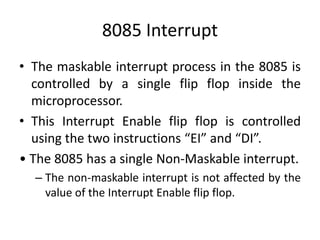

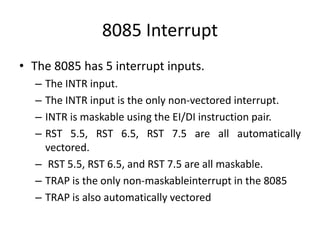

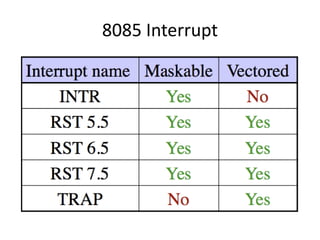

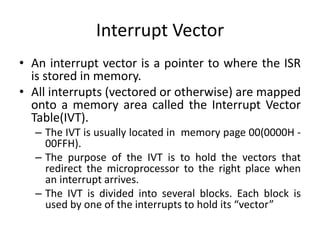

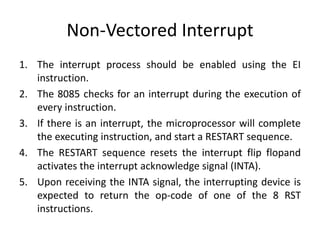

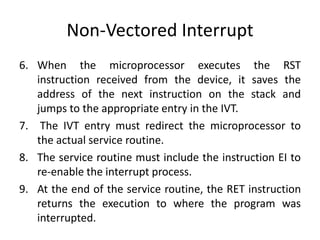

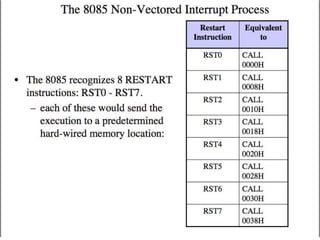

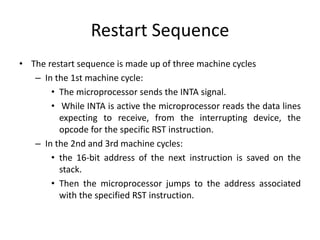

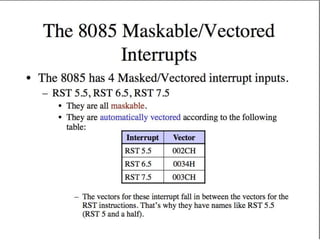

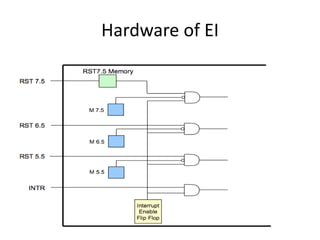

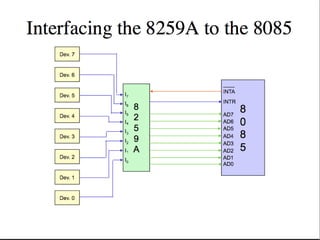

The document discusses interrupts in microprocessors. It defines an interrupt as an asynchronous signal from an I/O device that gets the processor's attention. Interrupts can be maskable, which can be delayed, or non-maskable, which cannot. The 8085 interrupt controller supports 5 interrupt lines, including one non-maskable TRAP line. Interrupts are handled through an interrupt vector table that redirects the processor to interrupt service routines.