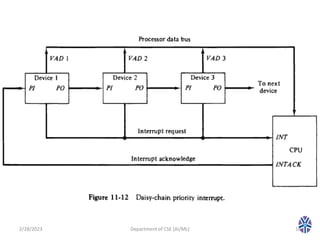

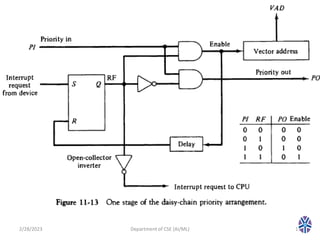

This document summarizes a session on input-output organization and memory hierarchy topics from a computer organization and architecture course. It discusses priority interrupts, including software polling and hardware daisy chaining and parallel priority approaches. It also covers direct memory access and topics to be covered in the next session on direct memory access.