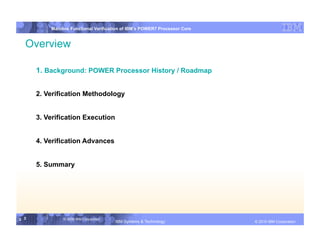

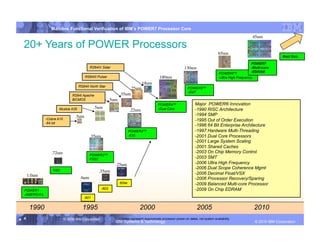

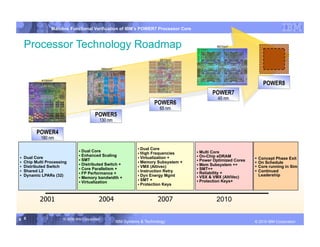

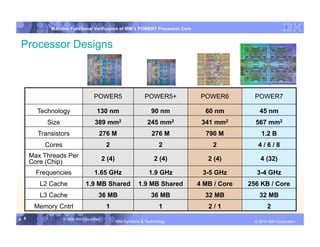

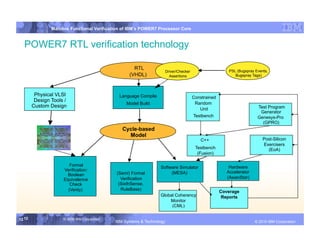

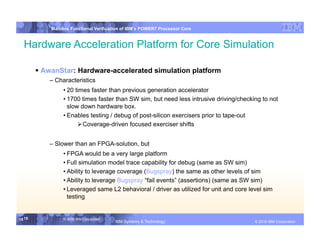

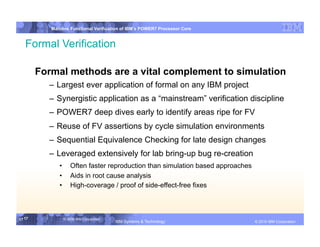

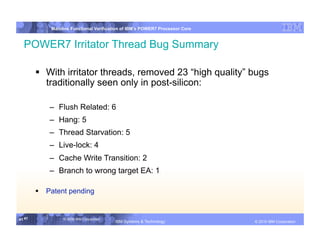

This document provides an overview of IBM's mainline functional verification of its POWER7 processor core. It first gives background on the history and roadmap of POWER processors. It then outlines the verification methodology, execution, advances, and concludes with a summary. The POWER7 is IBM's next generation processor that features a multi-core design, on-chip eDRAM, power optimization, and memory subsystem improvements. It follows over 20 years of POWER processors and continues IBM's leadership in this area.