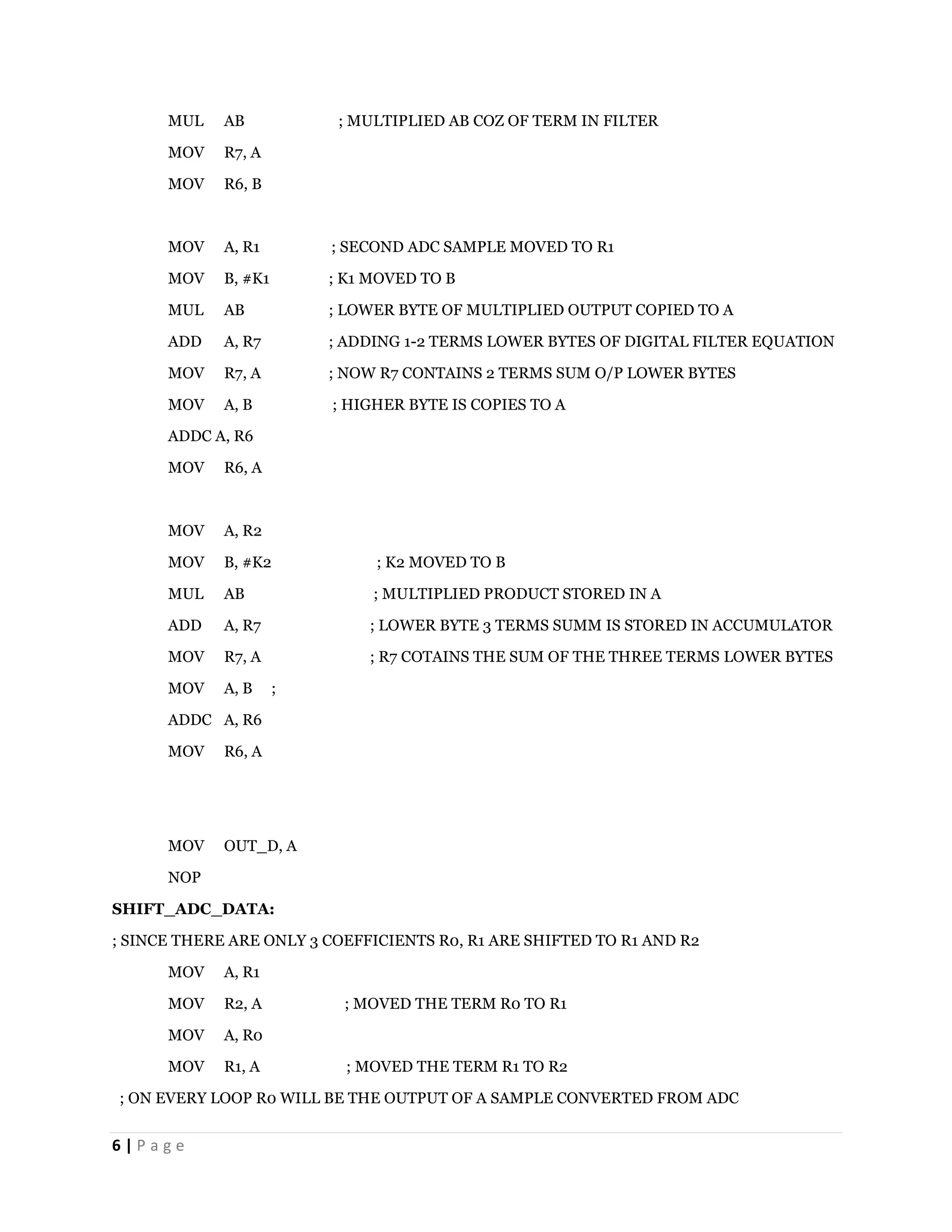

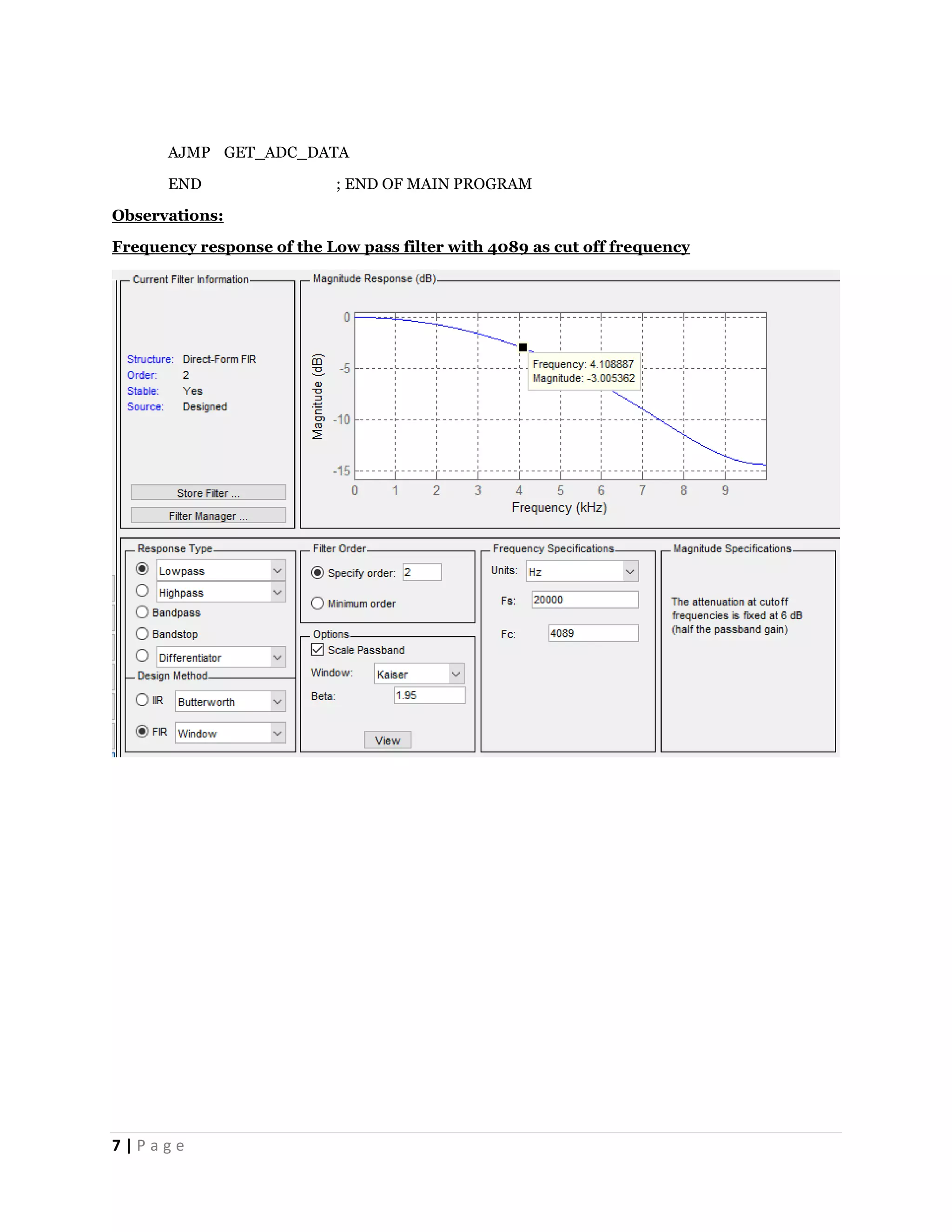

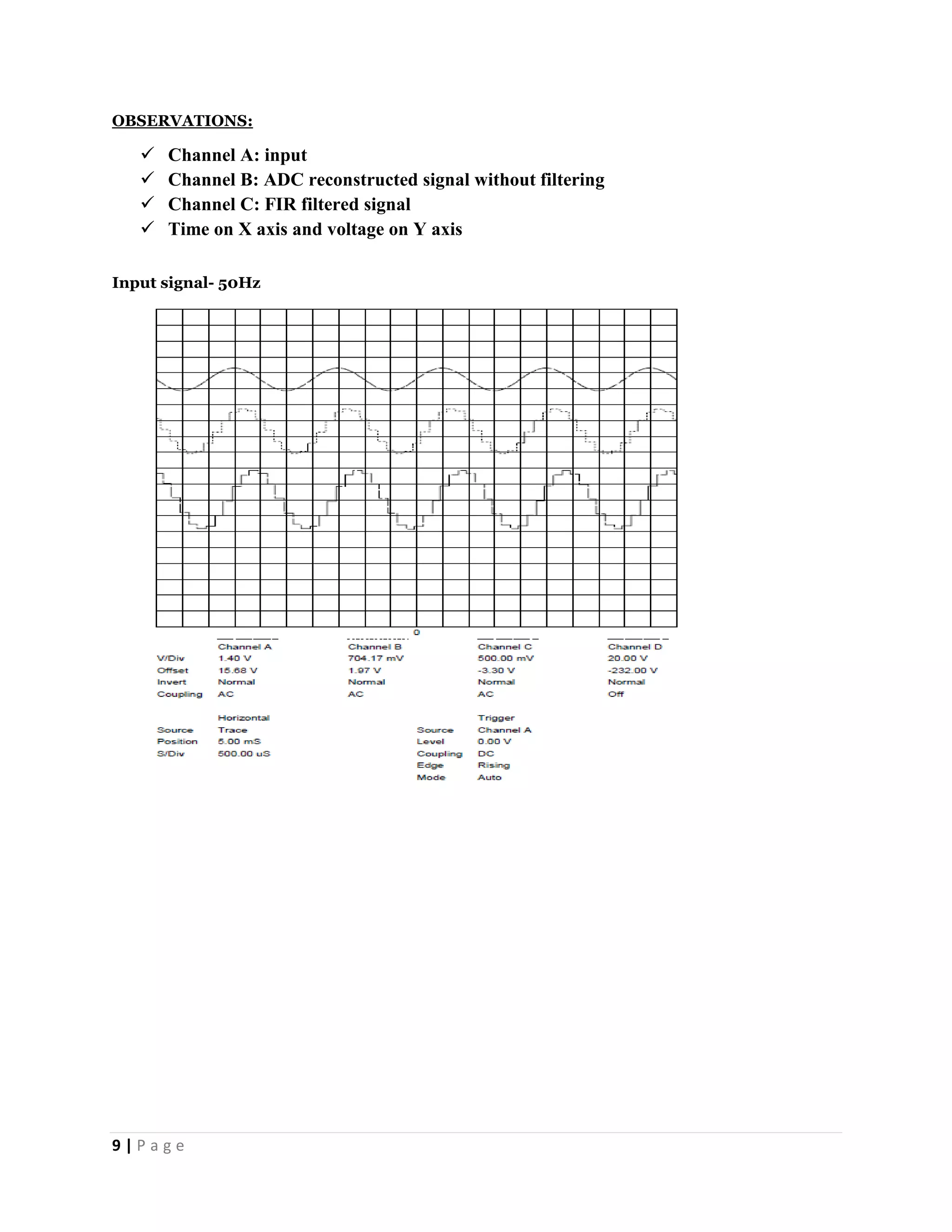

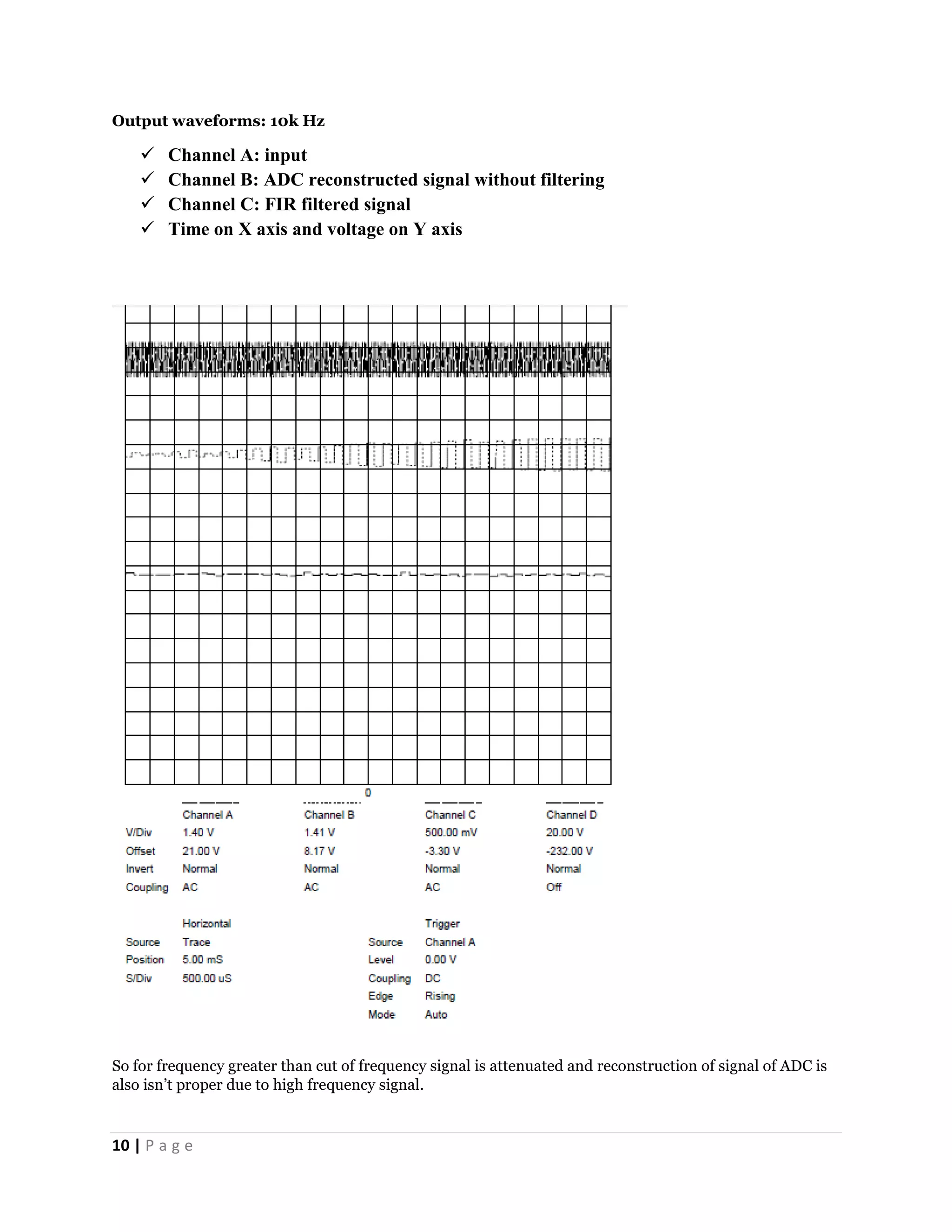

This document describes an experiment to design low pass and notch filters with a second order FIR structure using a microcontroller, ADC, DAC, and other components. The circuit and assembly code are presented. Observations of input and output signals at different frequencies are shown, demonstrating that low frequencies are filtered as intended while higher frequencies above the cutoff are not reconstructed properly. It is concluded that the FIR filter order should be higher and cutoff frequency lower for more accurate results.

![2 | P a g e

Digital FIR filter

A Finite Impulse Response (FIR) filter is a type of signal processing filter whose impulse response ( or

response to any finite length input ) is of finite duration, because it settles to zero in finite time. The impulse

response of an Nth-order discrete-time FIR filter lasts for N+1 samples, and then dies to zero.

For a discrete-time FIR filter, the output is a weighted sum of the current and a finite number of previous

input values. The operation is described by the following equation, which defines the output

sequence y[n] in terms of its input sequence x[n] :

𝑌[𝑛] = 𝐵𝑜 ∗ 𝑥[𝑛] + 𝐵1 ∗ 𝑥[𝑛 − 1] + 𝐵2 ∗ 𝑥[𝑛 − 2] + ⋯ … . . 𝐵𝑁 ∗ 𝑥[𝑛 − 𝑁]

𝑦[𝑛] = ∑ 𝐵𝑖 ∗ 𝑥[𝑛 − 𝑖]𝑁

𝐼=0

x[n] ----------- input signal

y[n] ----------- output signal

bi ----------- filter co-efficients

N ----------- filter order](https://image.slidesharecdn.com/experiment2firfiltere2group13-180724202952/75/Low-pass-digital-filter-using-FIR-structure-of-2nd-order-3-2048.jpg)