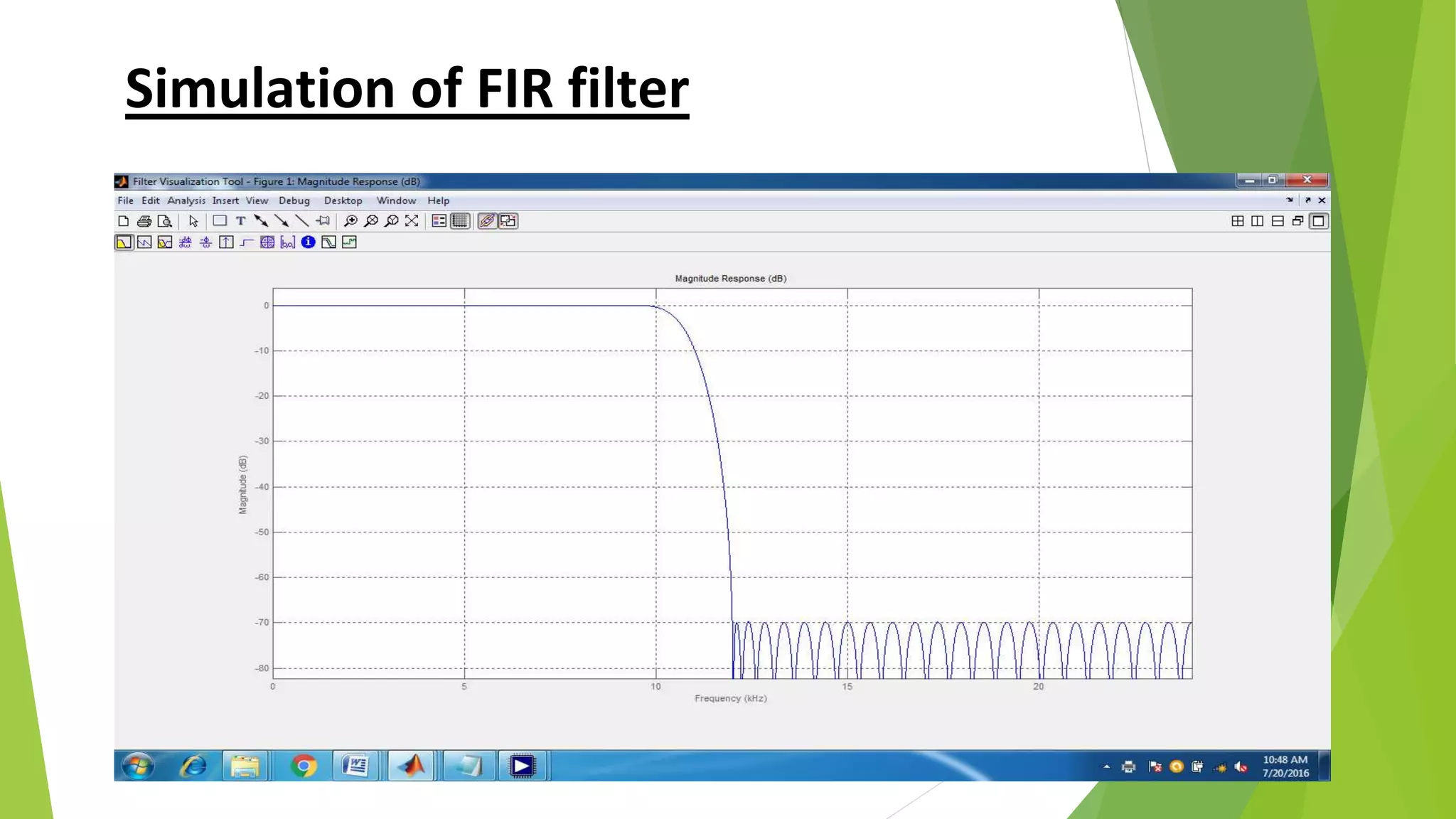

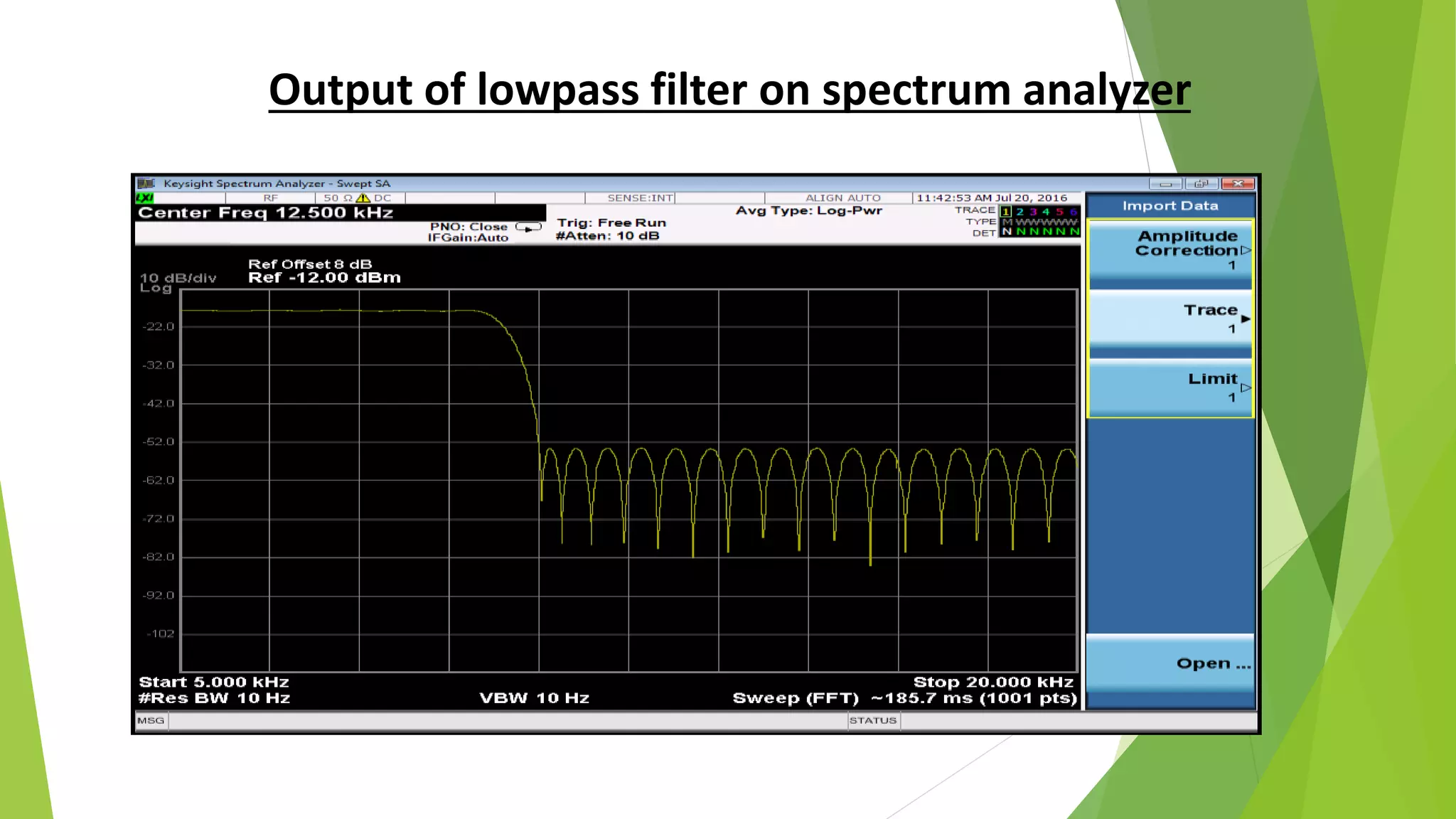

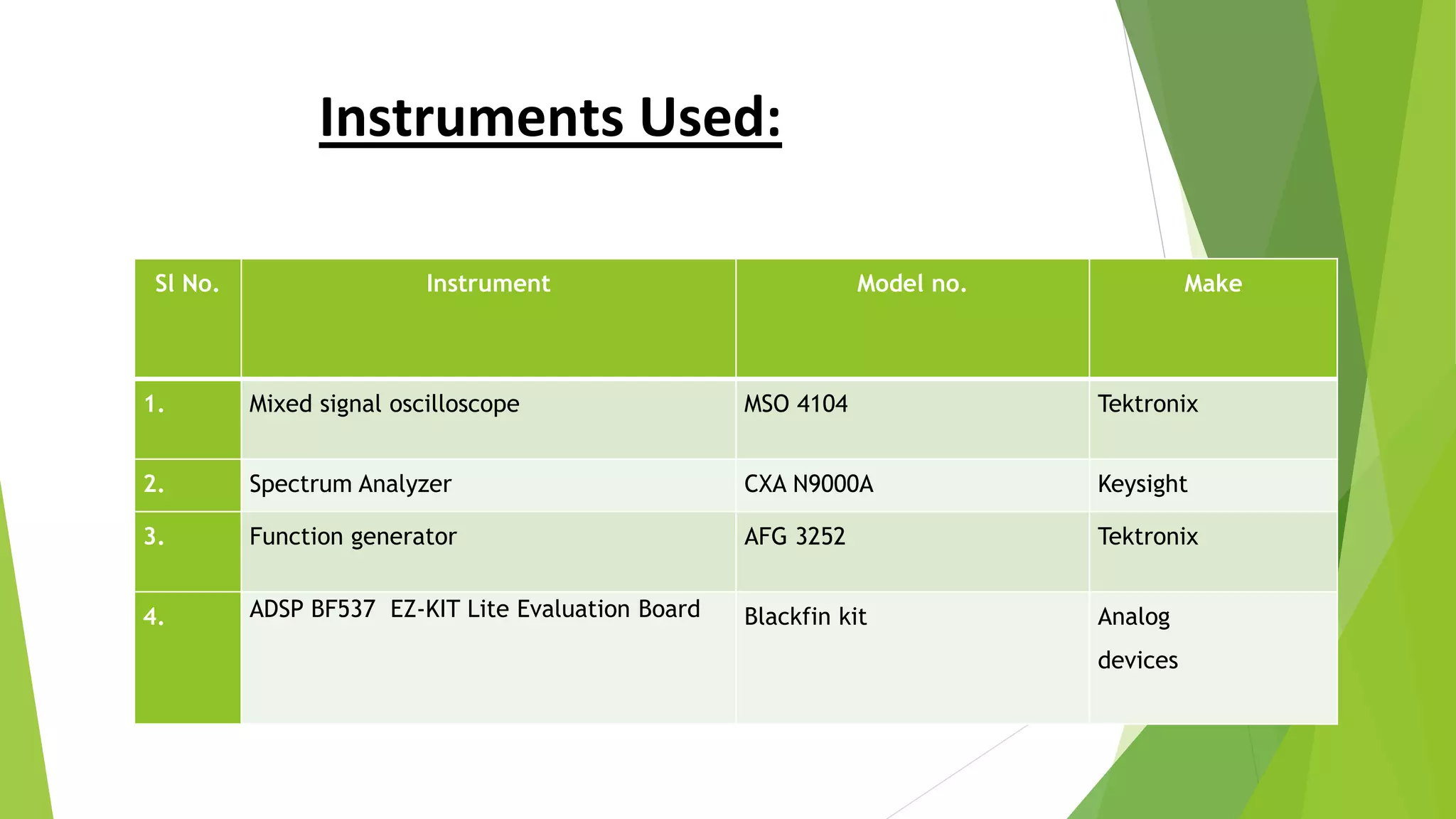

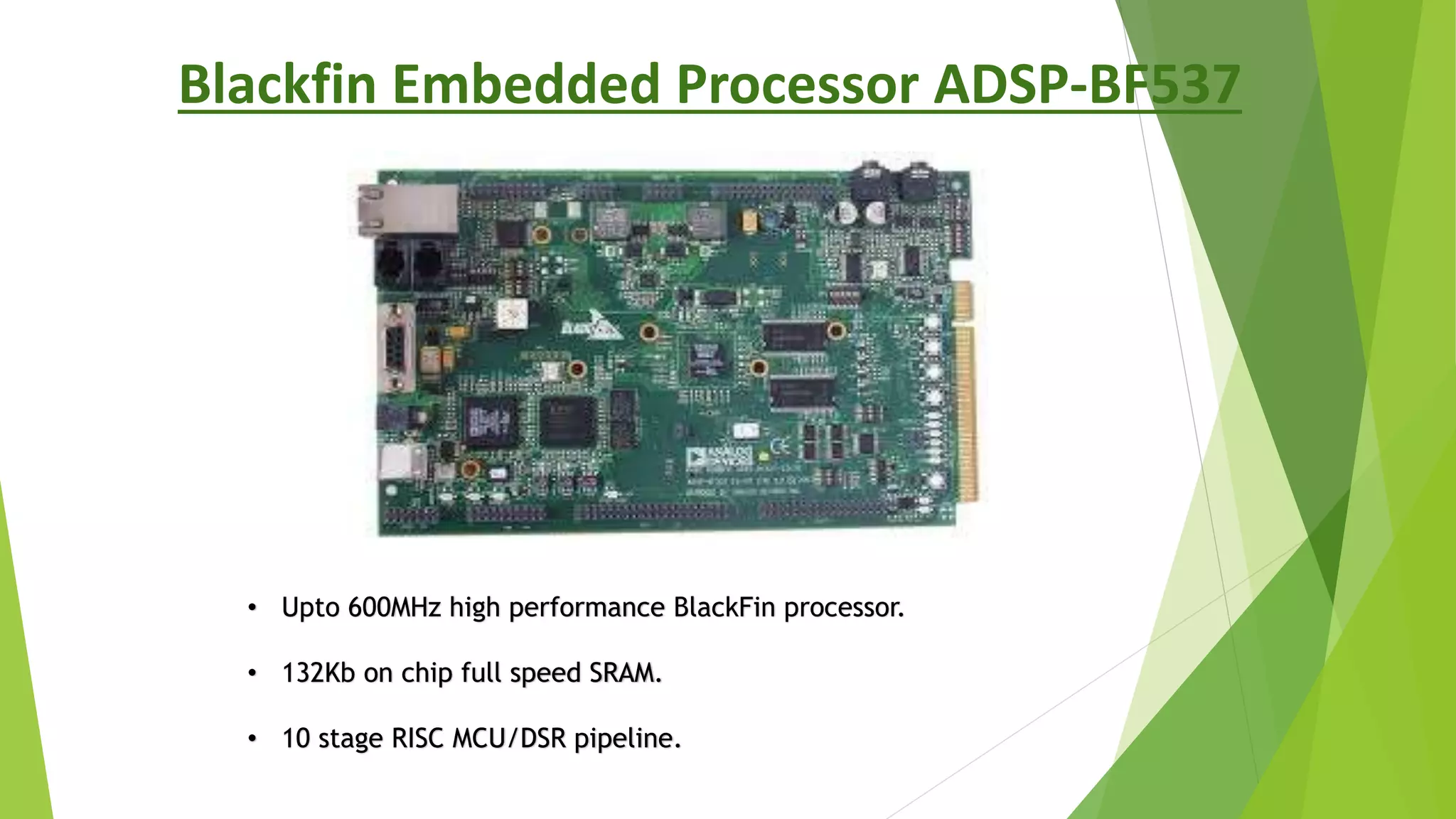

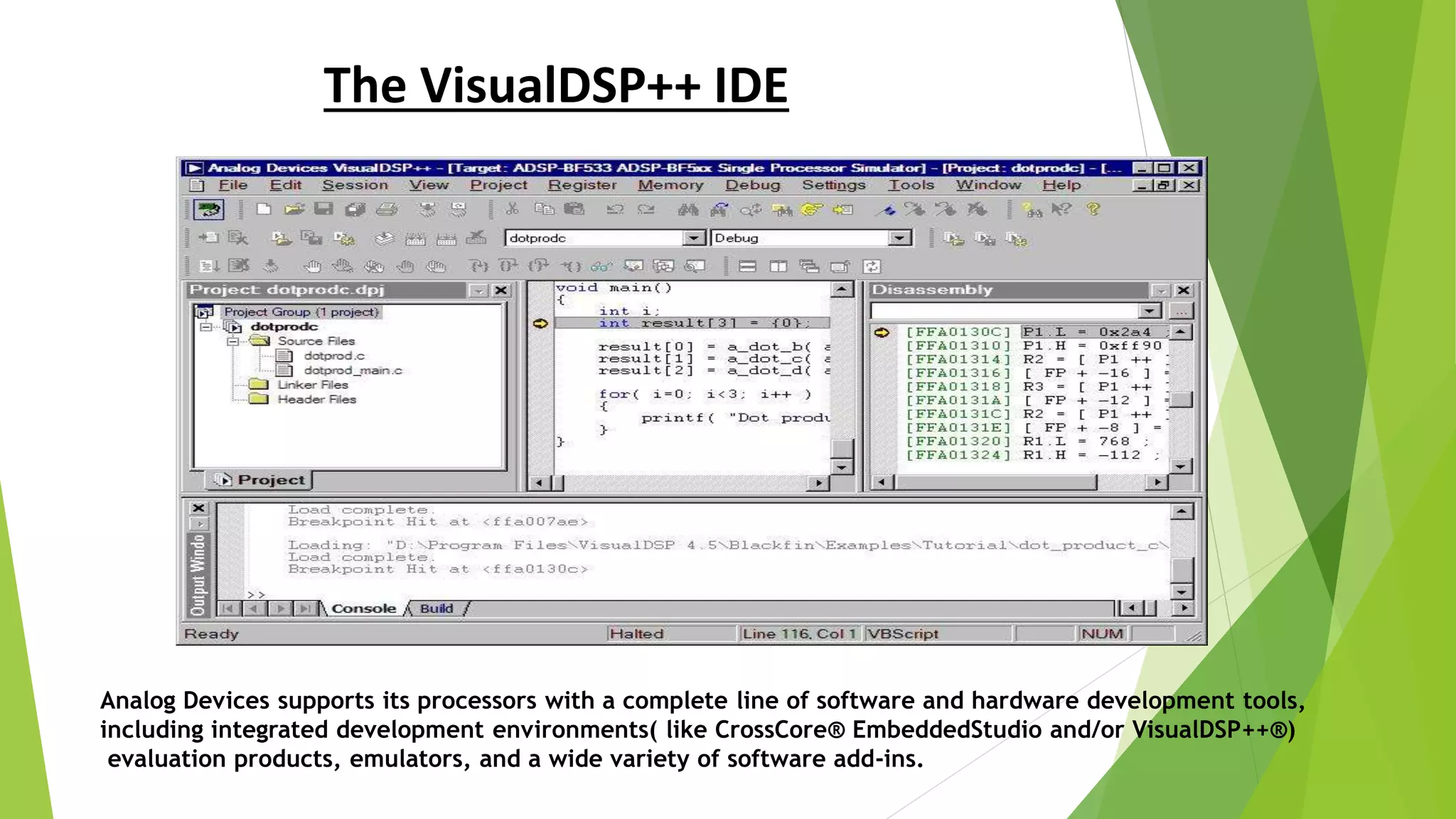

The document describes a project to implement a finite impulse response (FIR) filter on an ADSP-BF537 digital signal processor. It provides background on FIR filters and their properties. The project involved generating filter coefficients in Matlab, programming the FIR algorithm on the DSP board using tools like VisualDSP++, and simulating the lowpass filter output on a spectrum analyzer. Key instruments used included an oscilloscope, spectrum analyzer, function generator, and an evaluation board with the Blackfin DSP processor.

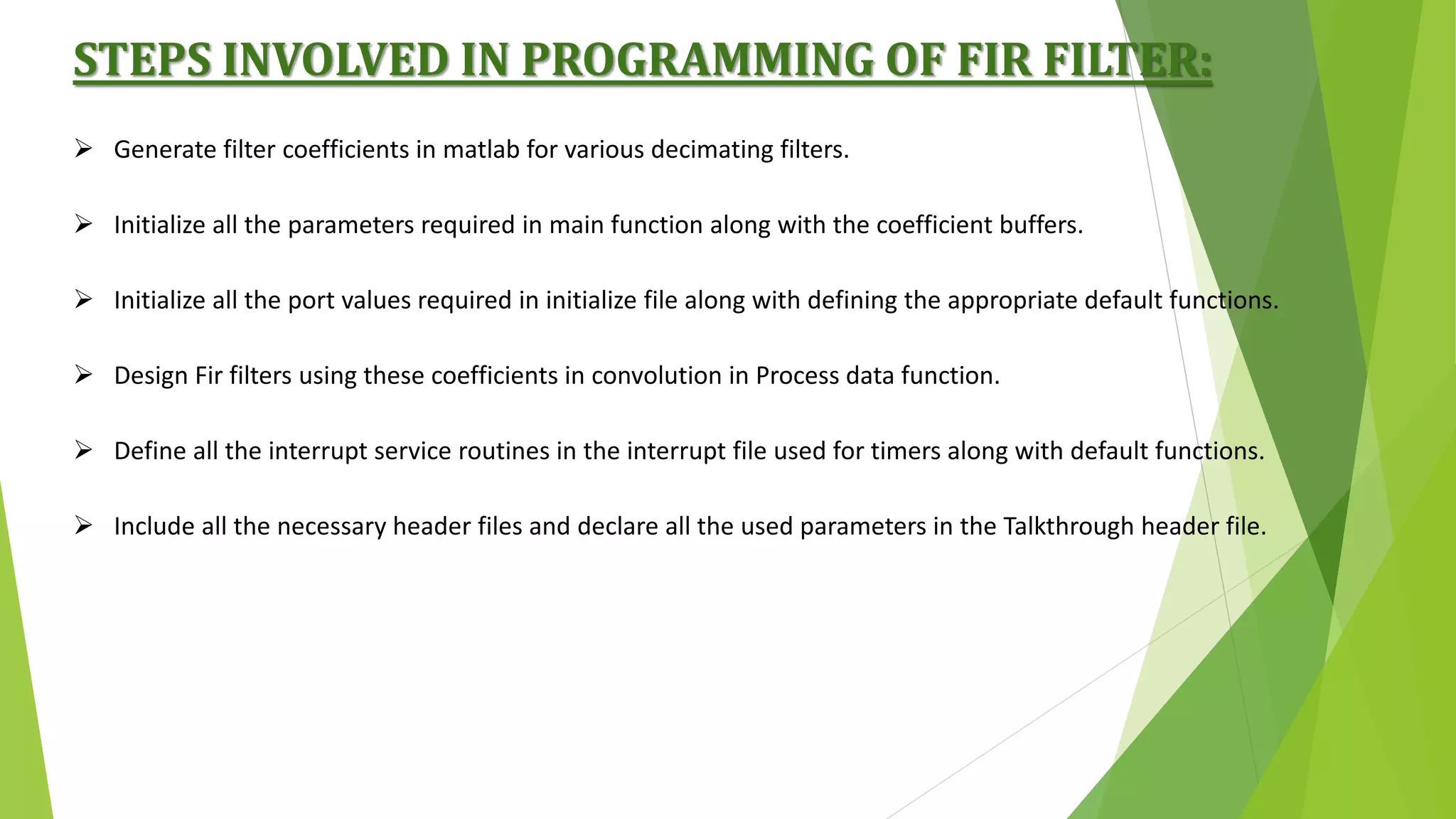

![Algorithm for implementing filter

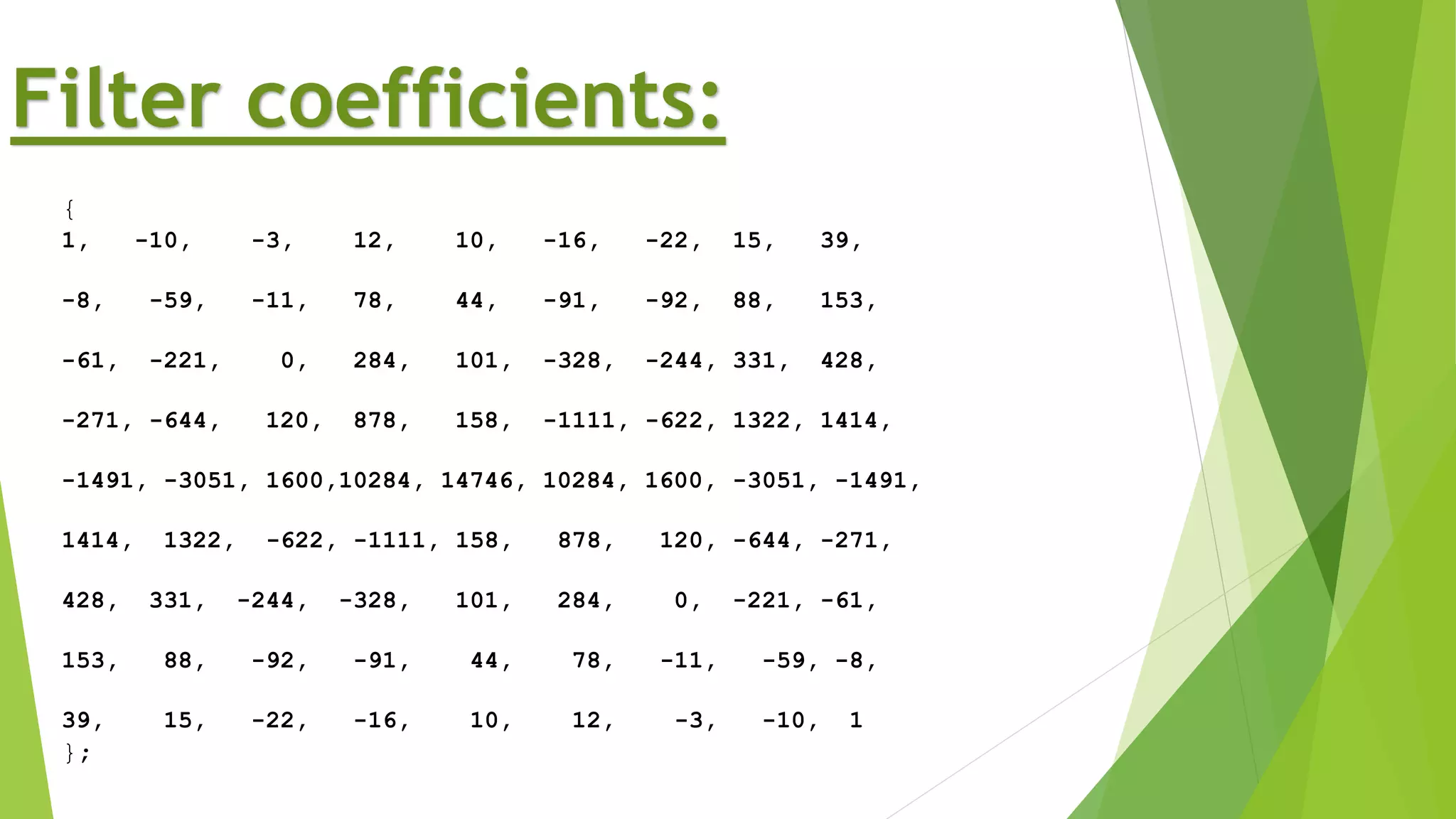

Create an array h[i] storing the coefficients.

Create another array x[n] to store the sampled signals.

REPEAT:

Store the current sample at x[0].

Multiply the corresponding elements of the x[n] and h[i].

Add all the values of x[n]*h[i].

Send the sum to the output buffer.

Shift the values of the array x[n] by one element and store new sample at

x[0].](https://image.slidesharecdn.com/80532fdf-74a7-4183-974f-63520bb65746-170222090537/75/INDUSTRIAL-TRAINING-REPORT-12-2048.jpg)