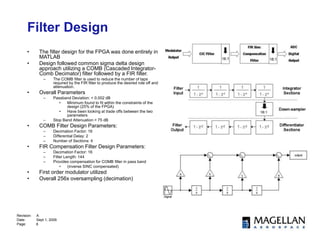

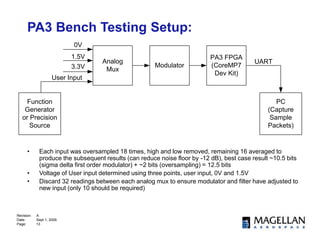

This document describes the implementation of a sigma delta analog-to-digital converter (ADC) design in an FPGA. It discusses the motivation to use an FPGA-based design instead of a traditional radiation-hardened ADC. The design constraints and process are described, including using MATLAB to design filters, simulating the design, and hand coding the filters in VHDL. Preliminary test results on a prototype show the design meets the accuracy goals and is viable to prototype further.