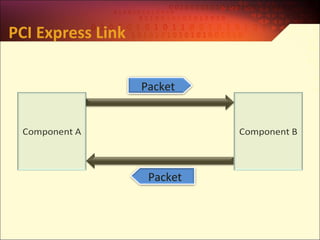

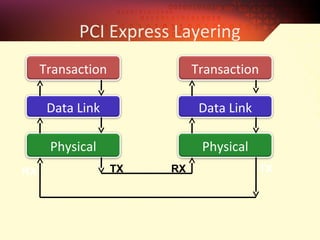

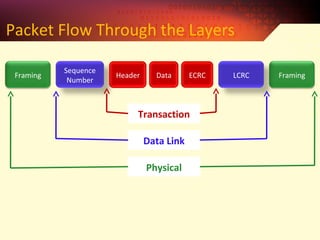

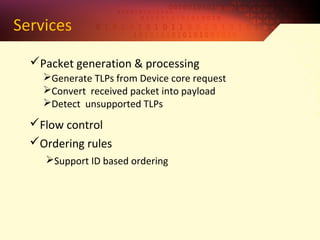

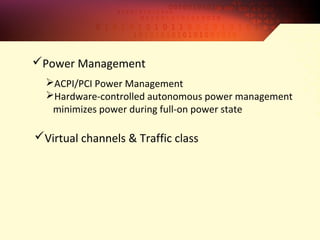

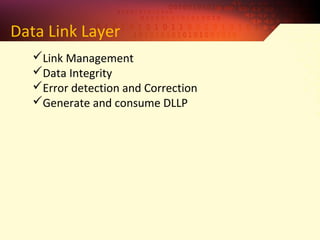

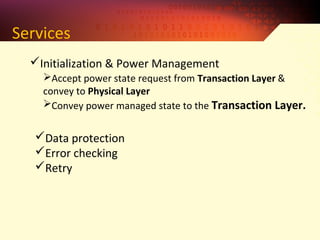

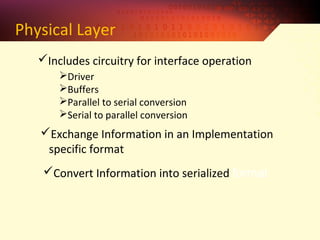

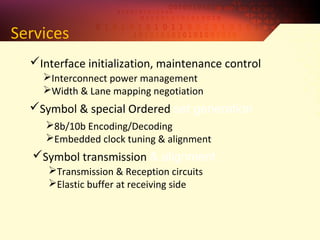

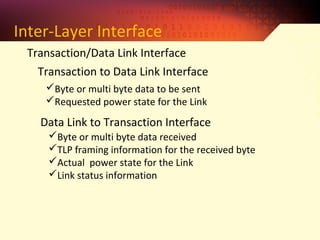

PCI Express is a high-performance interconnect that supports various usages through its advanced features like power management, quality of service, hot-plugging, and error handling. It operates across three layers - transaction, data link, and physical layers. The transaction layer handles packet assembly and addressing while the data link layer manages link initialization and data integrity. The physical layer implements the electrical interface through encoding, decoding, and transmission/reception circuits.