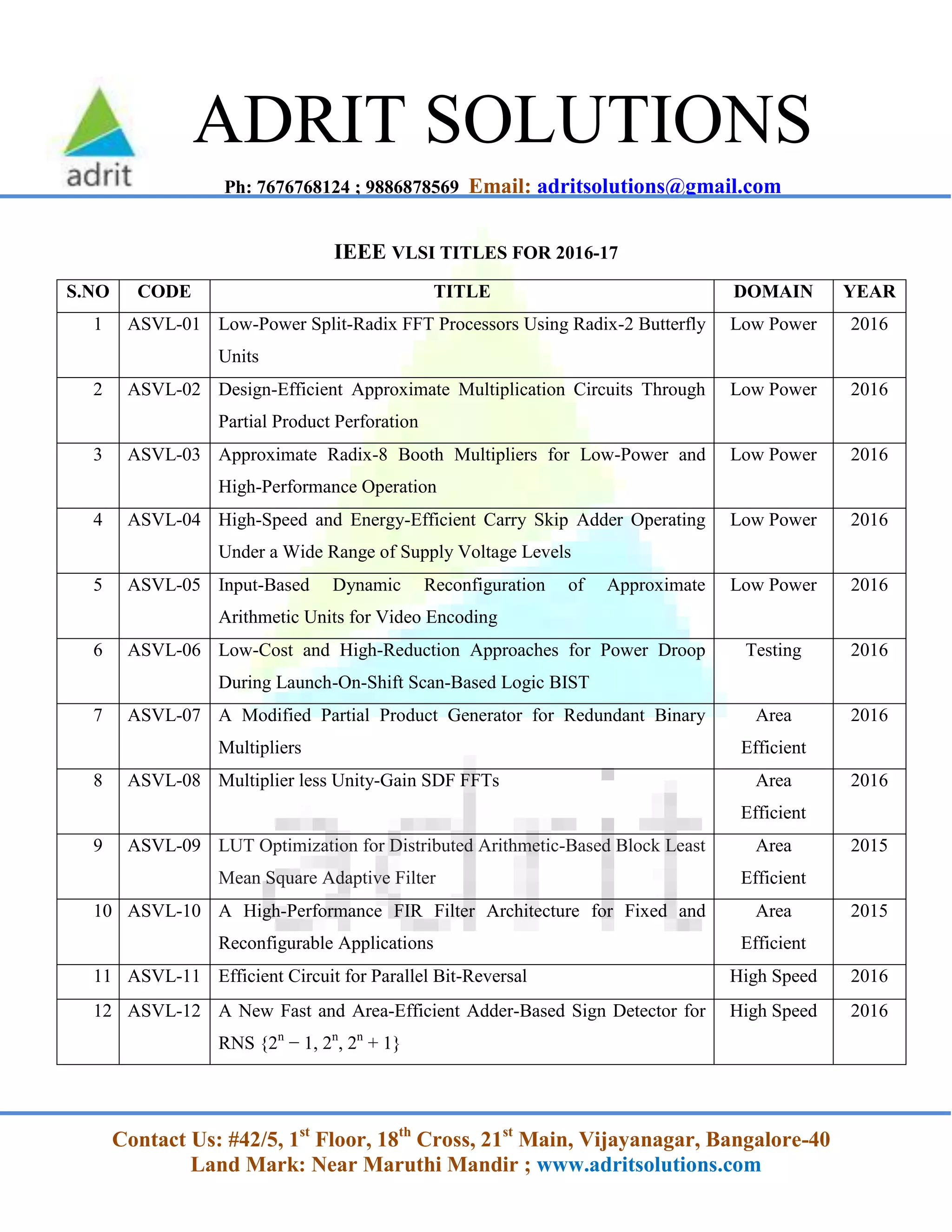

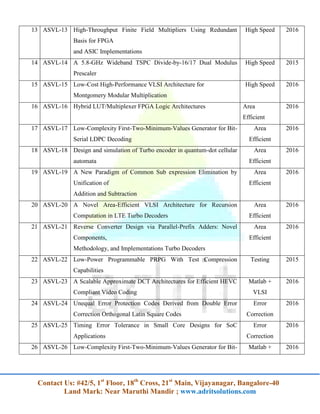

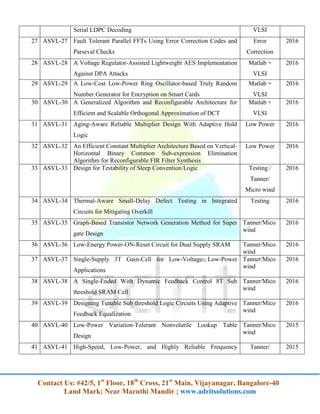

This document contains details of 49 IEEE VLSI titles from 2014-2016 related to various domains like low power, area efficient, high speed, testing, error correction and matlab+VLSI. It provides the title code, title, domain and year for each title. It also contains contact details of ADRIT SOLUTIONS including address, phone number, email and website. The titles are focused on developing efficient VLSI architectures and circuits for applications like signal processing, encryption, filtering and testing.