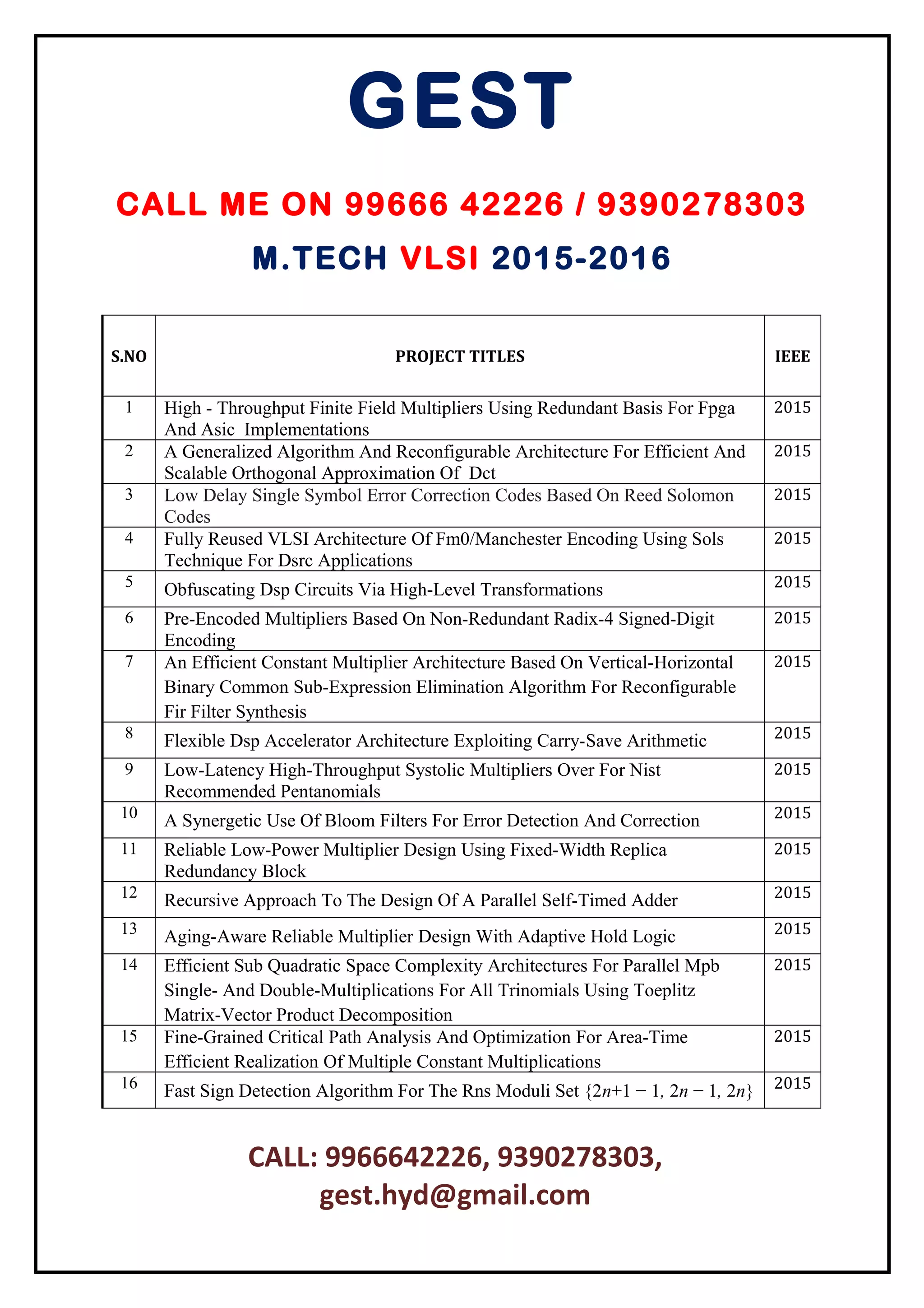

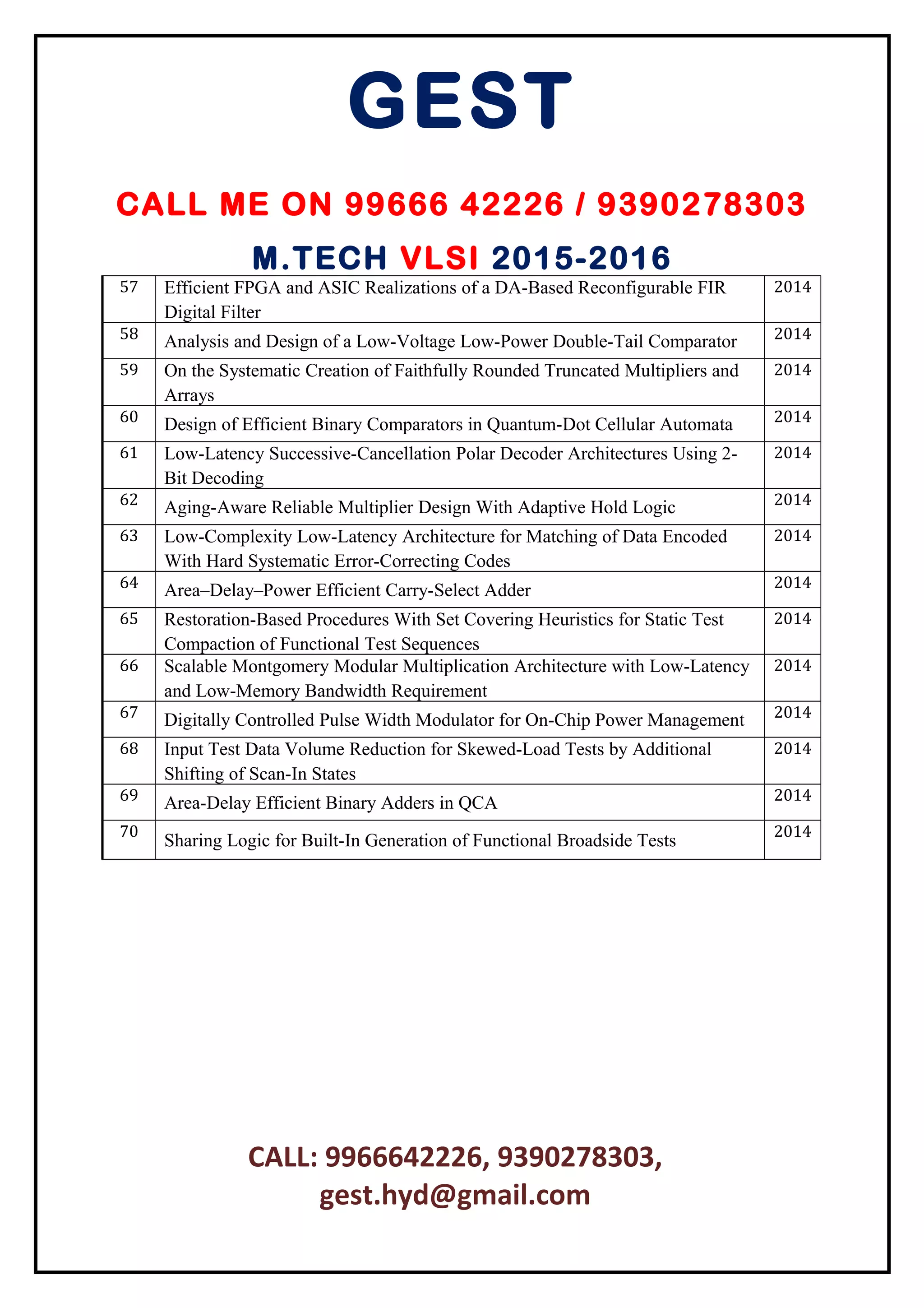

The document lists 70 M.Tech VLSI projects from 2015-2016, including their titles and years of completion. It provides contact information for GEST, including phone numbers 99666 42226 and 9390278303, and an email of gest.hyd@gmail.com. The projects cover a range of topics in VLSI design including multipliers, DSP circuits, error correction codes, and testing.