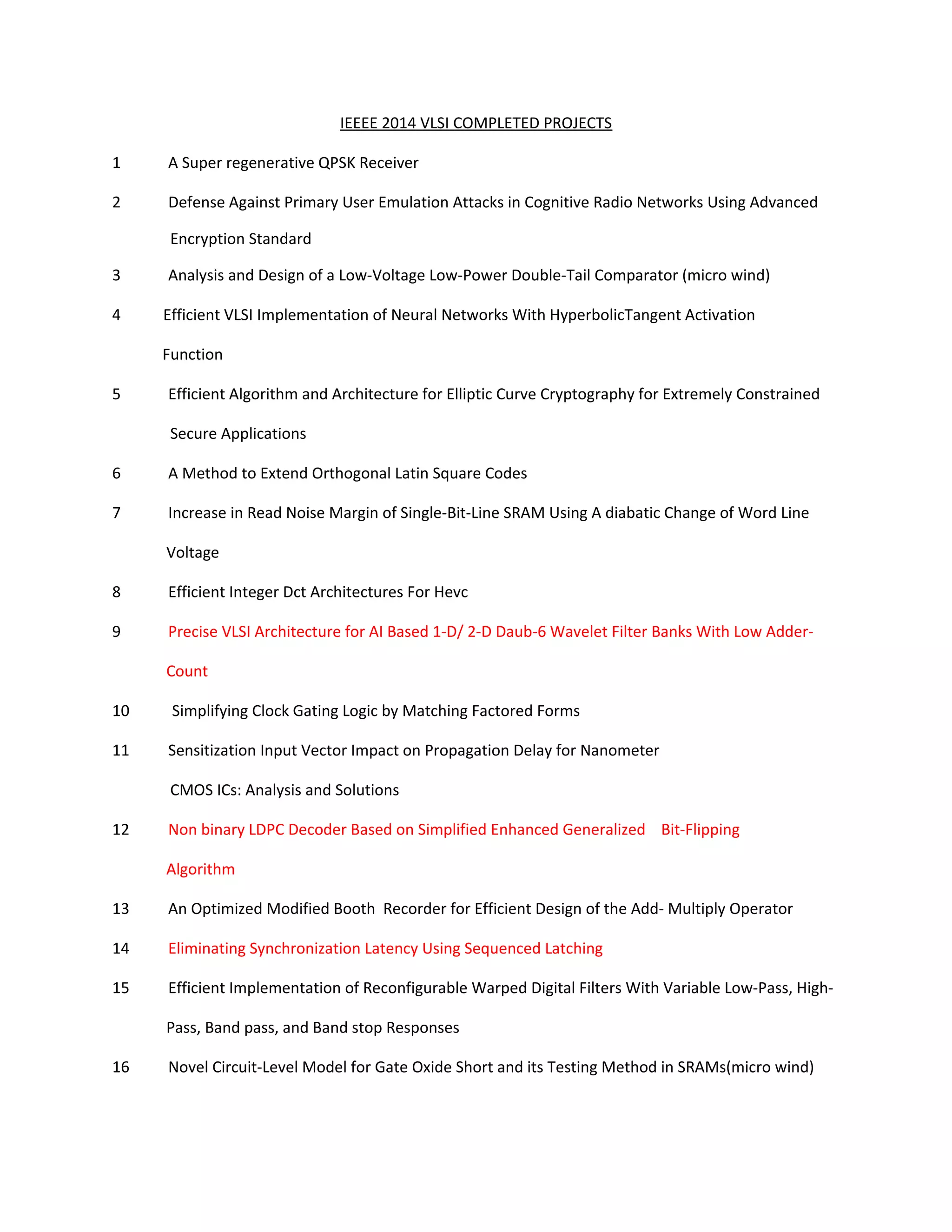

The document lists completed VLSI projects from IEEE 2014, covering a broad range of topics such as super regenerative QPSK receivers, low-power circuit designs, and cryptographic architectures. Key highlights include techniques for efficient digital filter implementations, advanced coding methods, and innovative hardware designs for enhanced performance and power reduction. Overall, the projects emphasize the application of novel algorithms and architectures in various fields of electronic engineering.