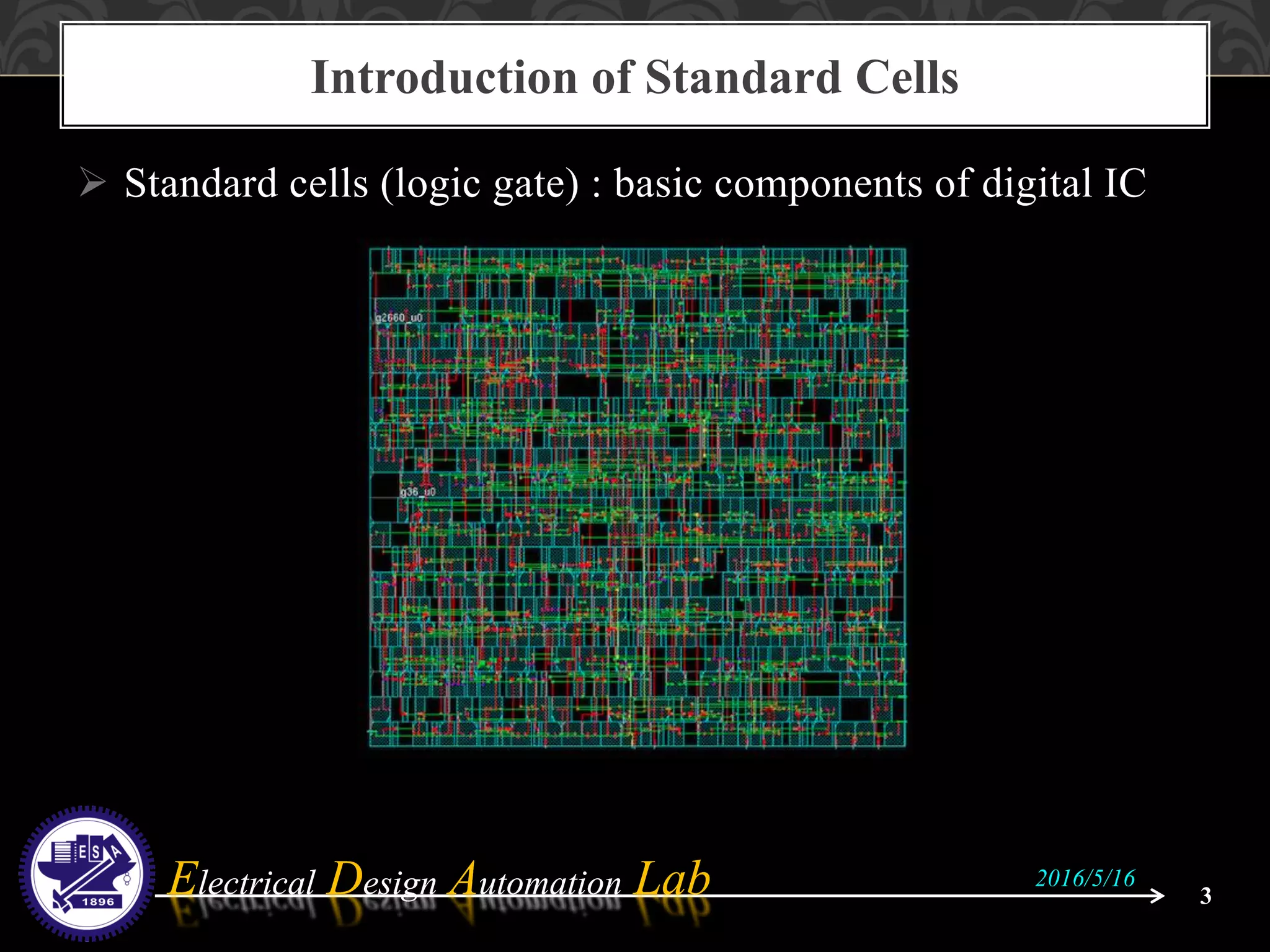

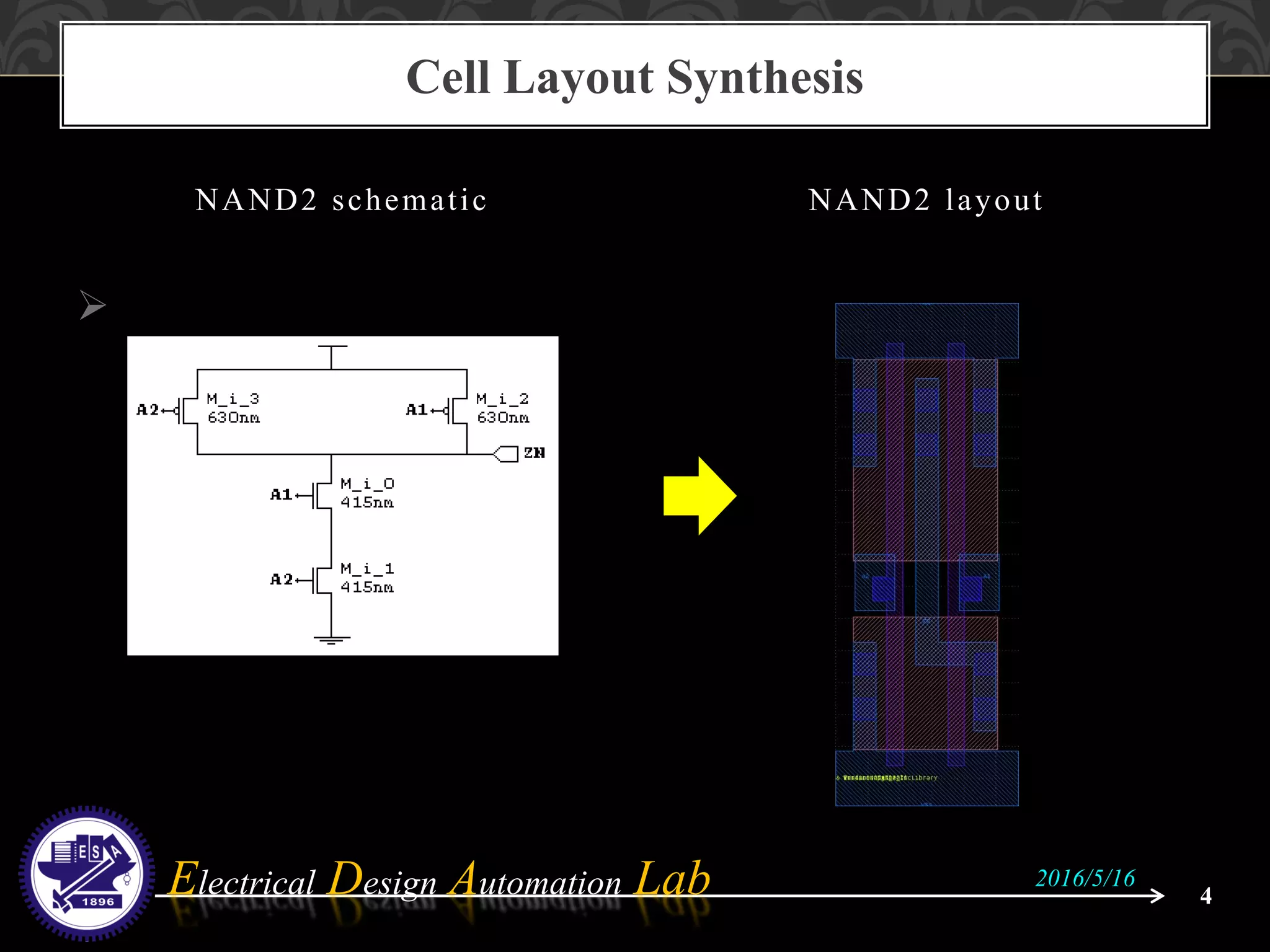

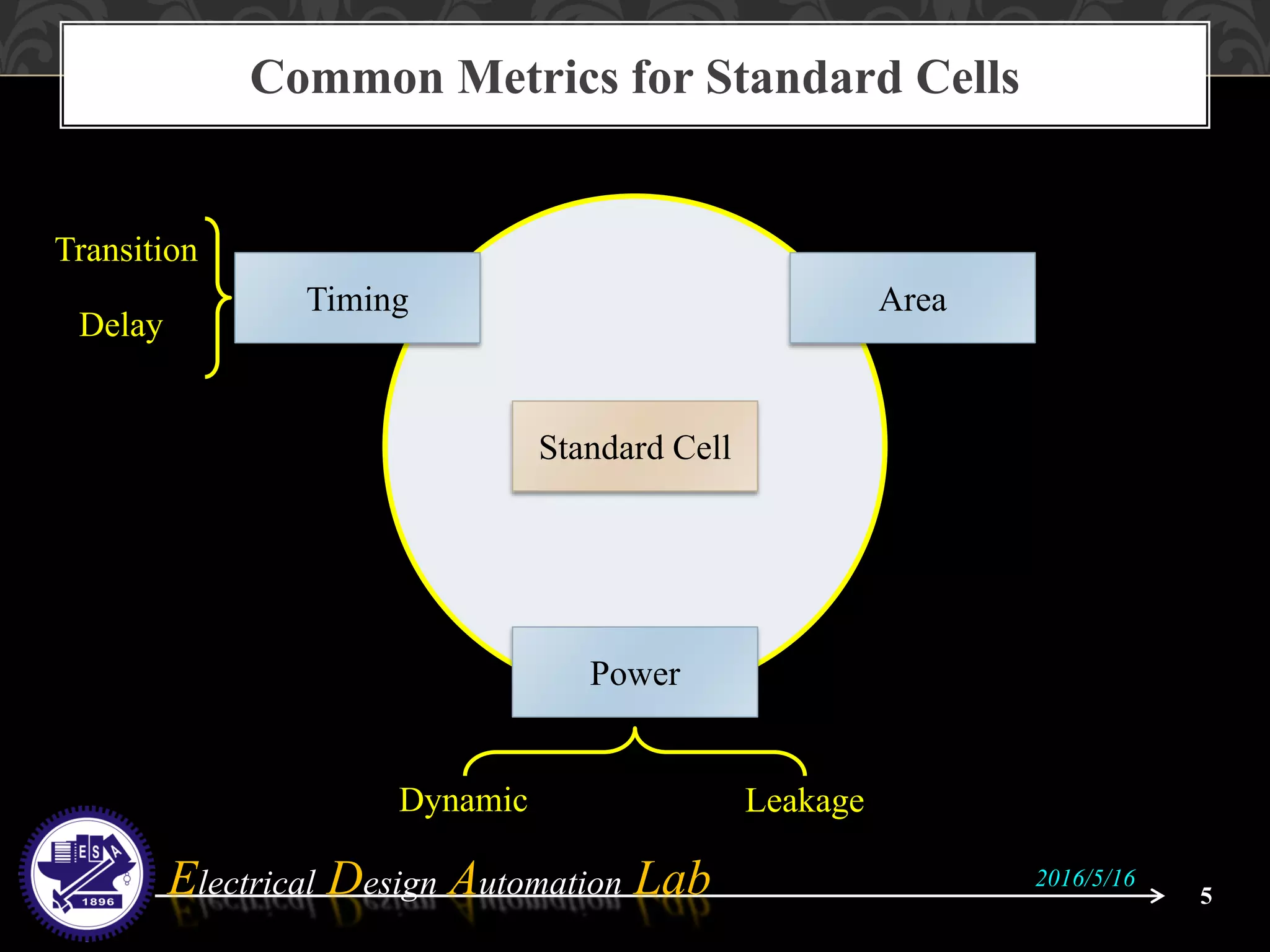

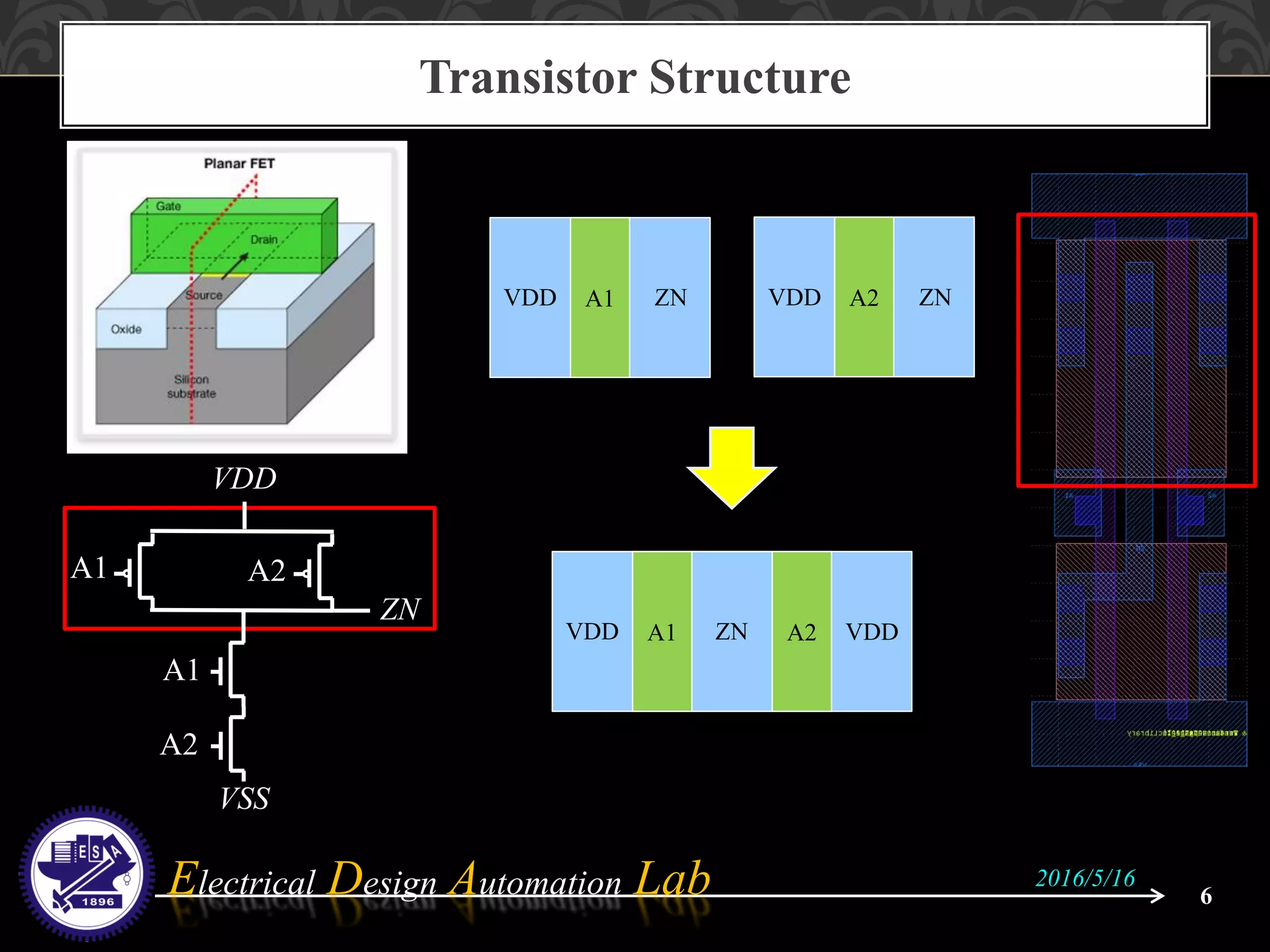

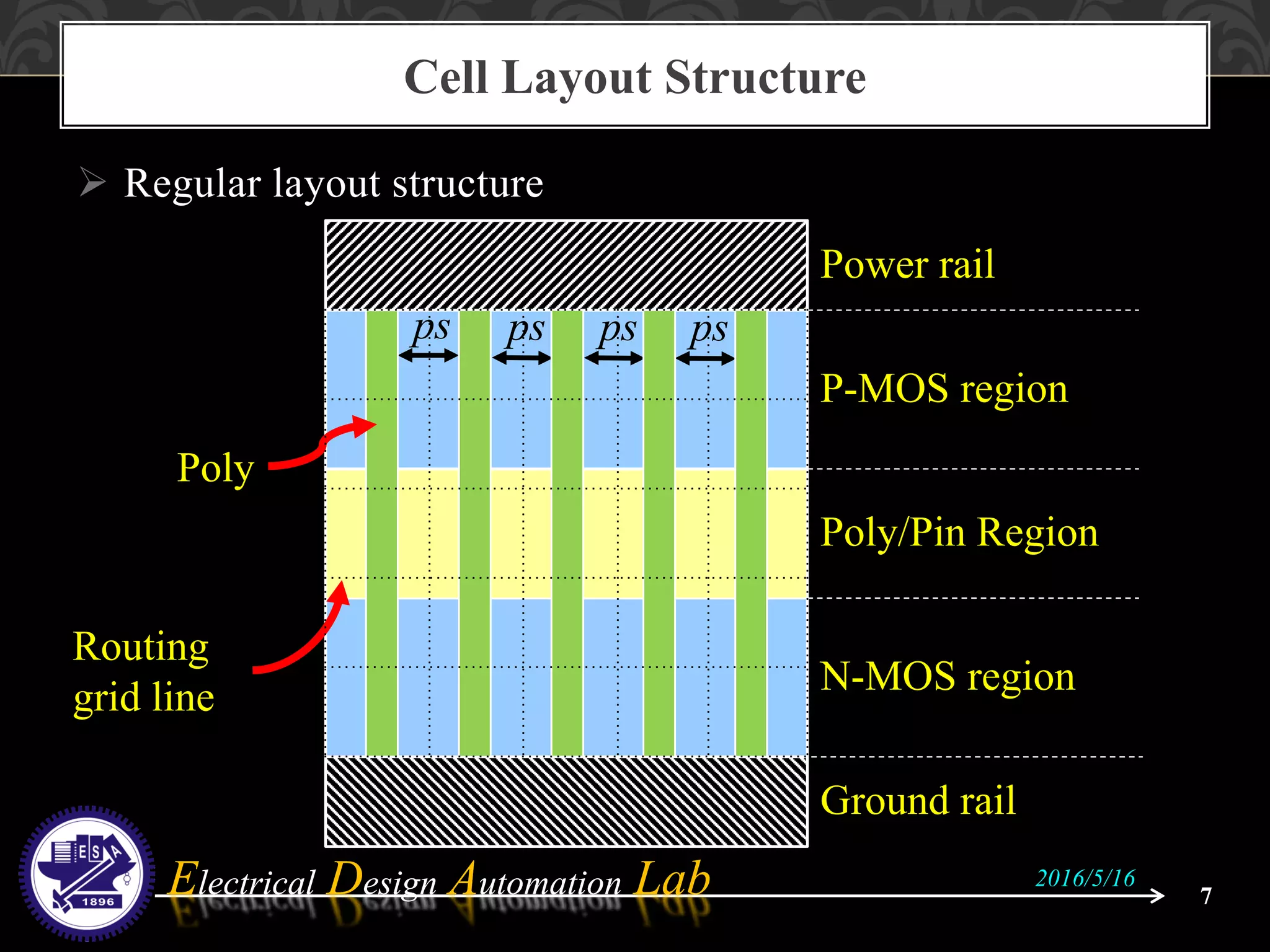

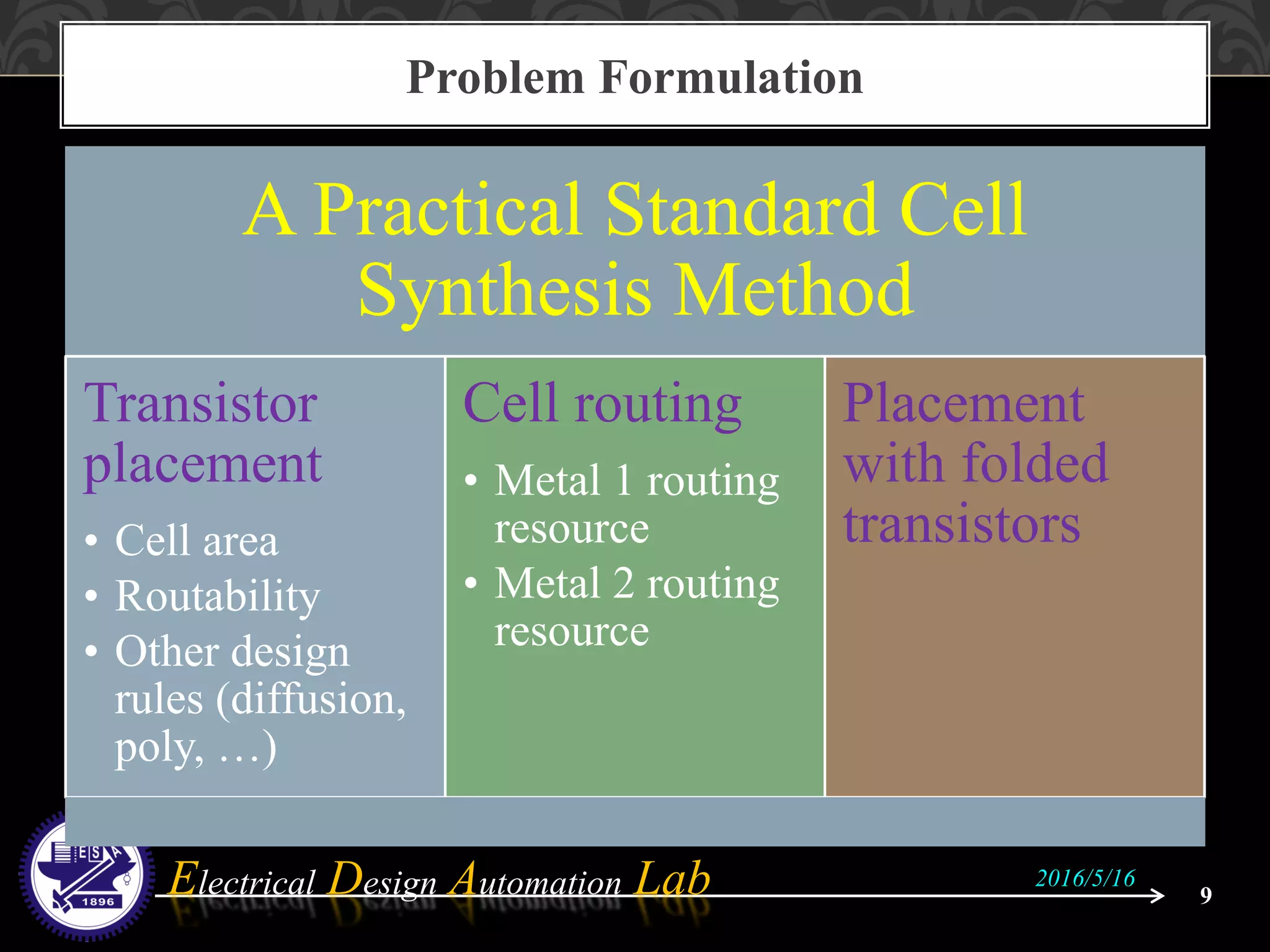

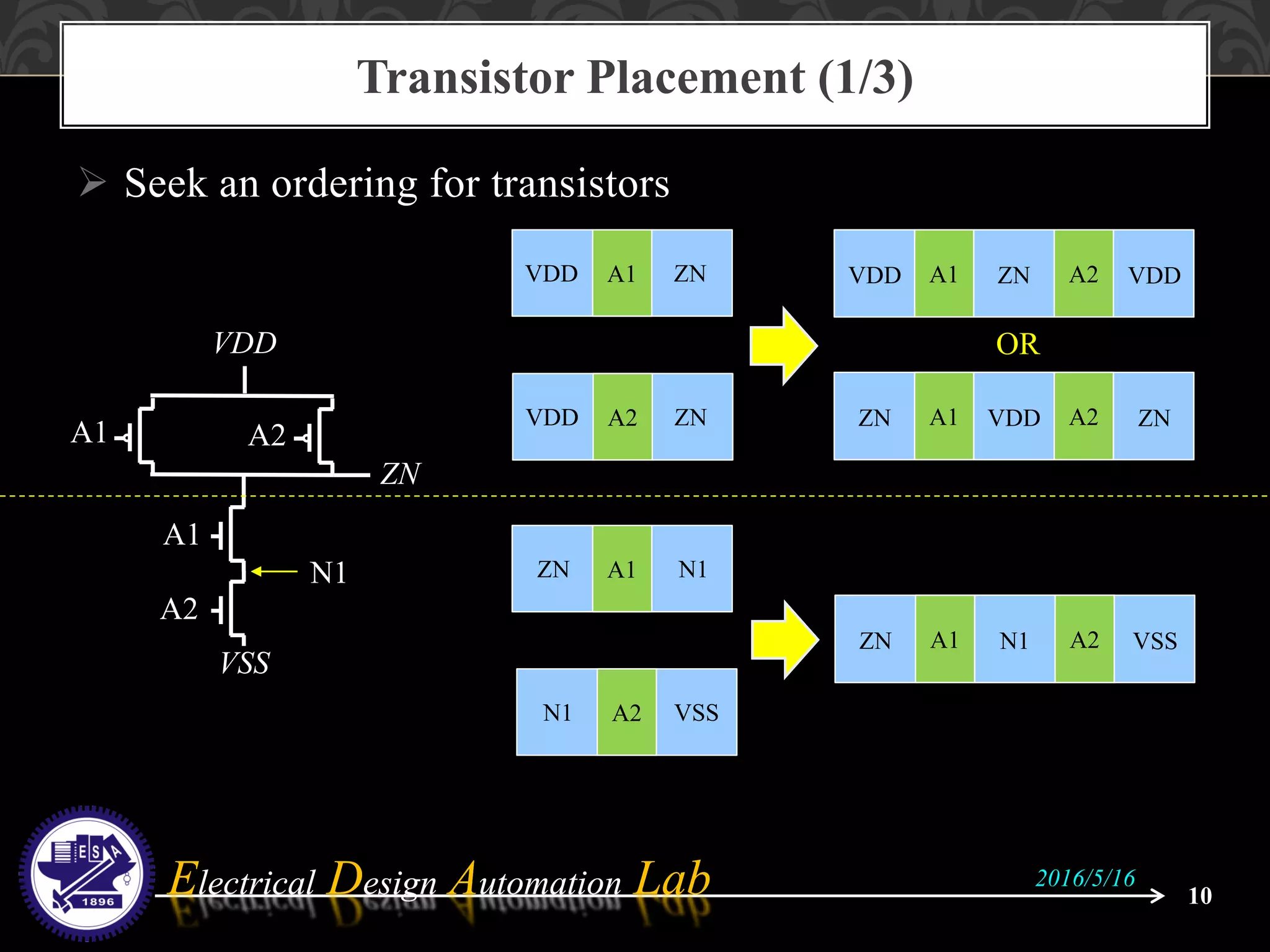

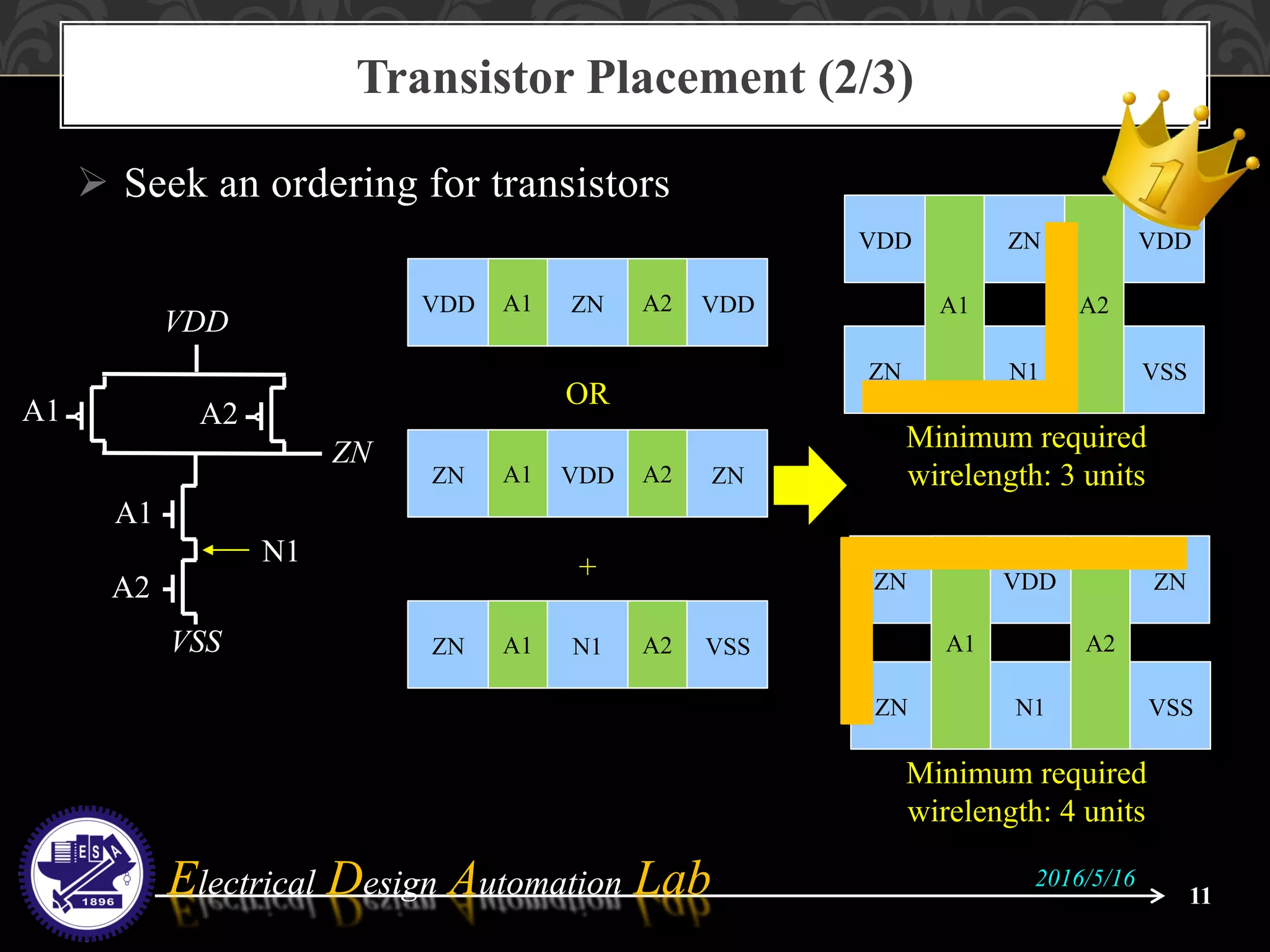

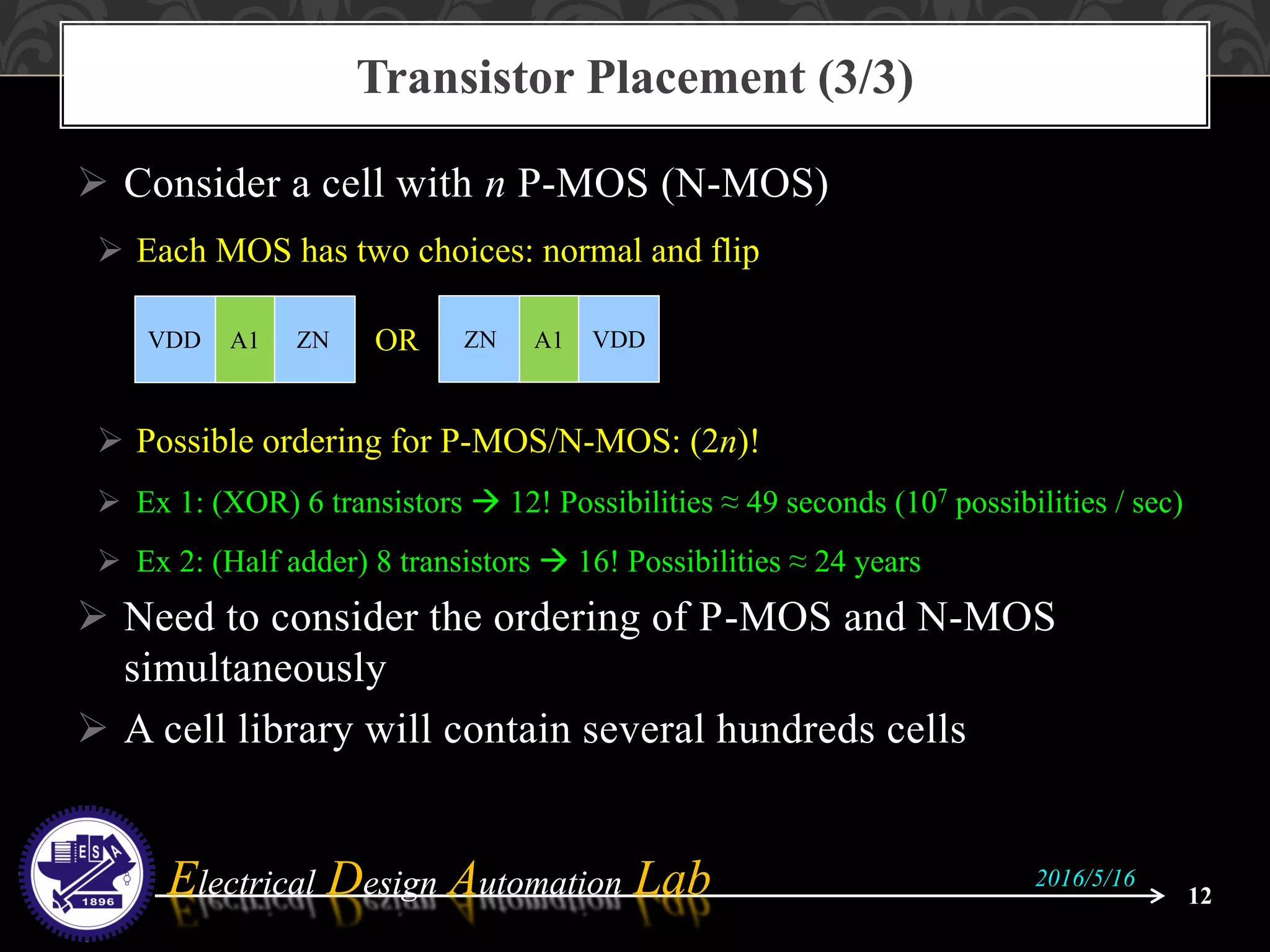

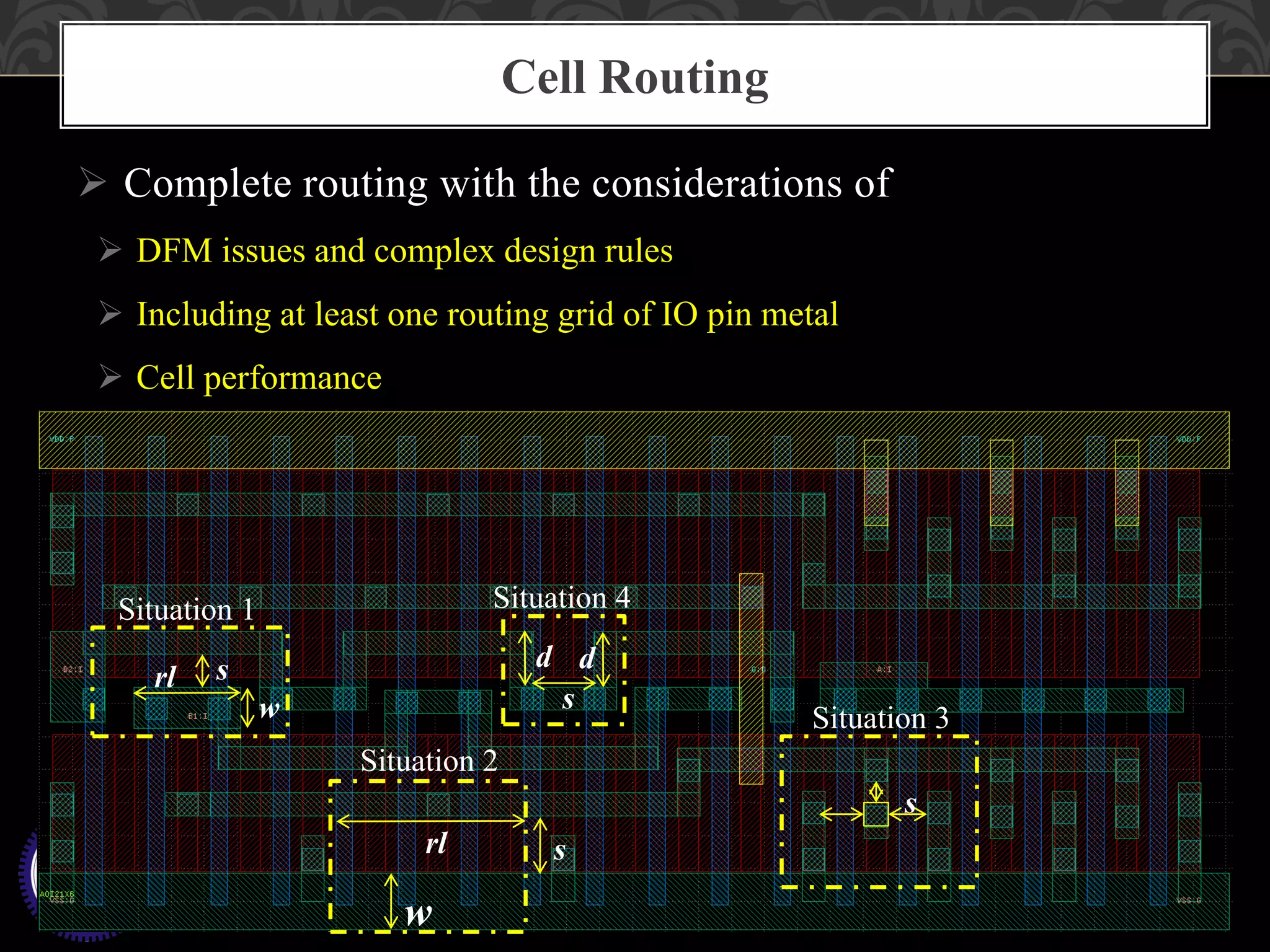

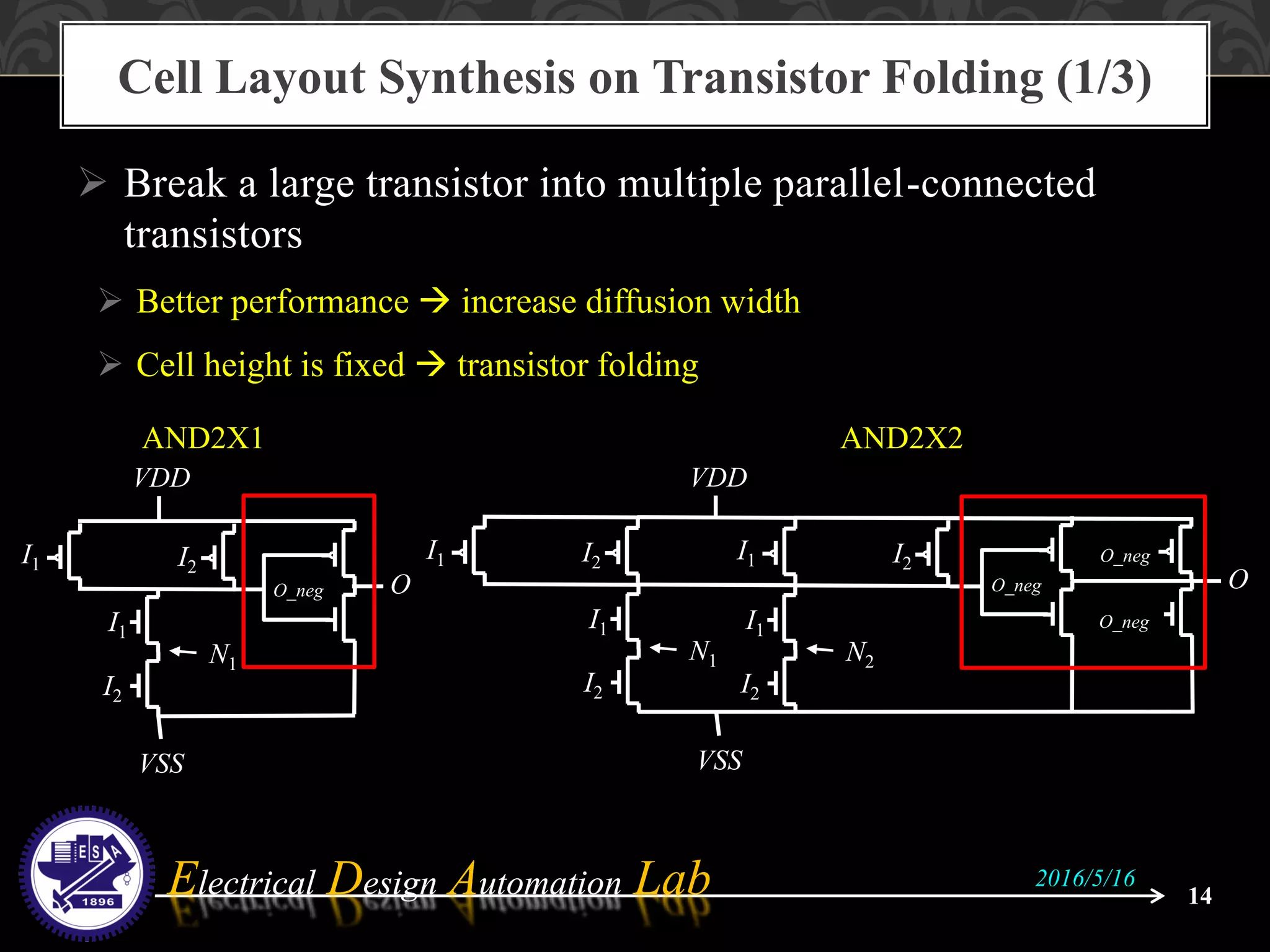

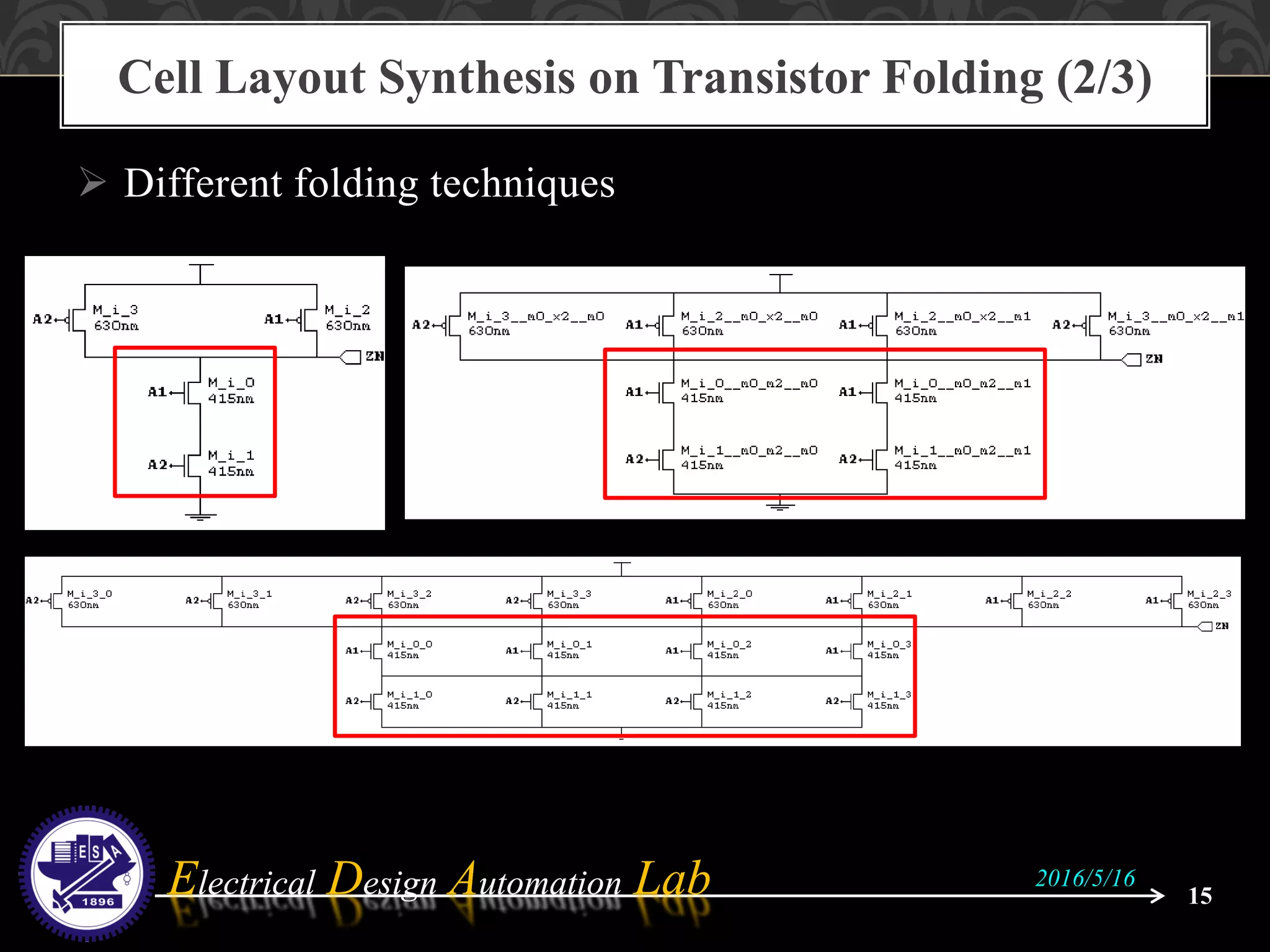

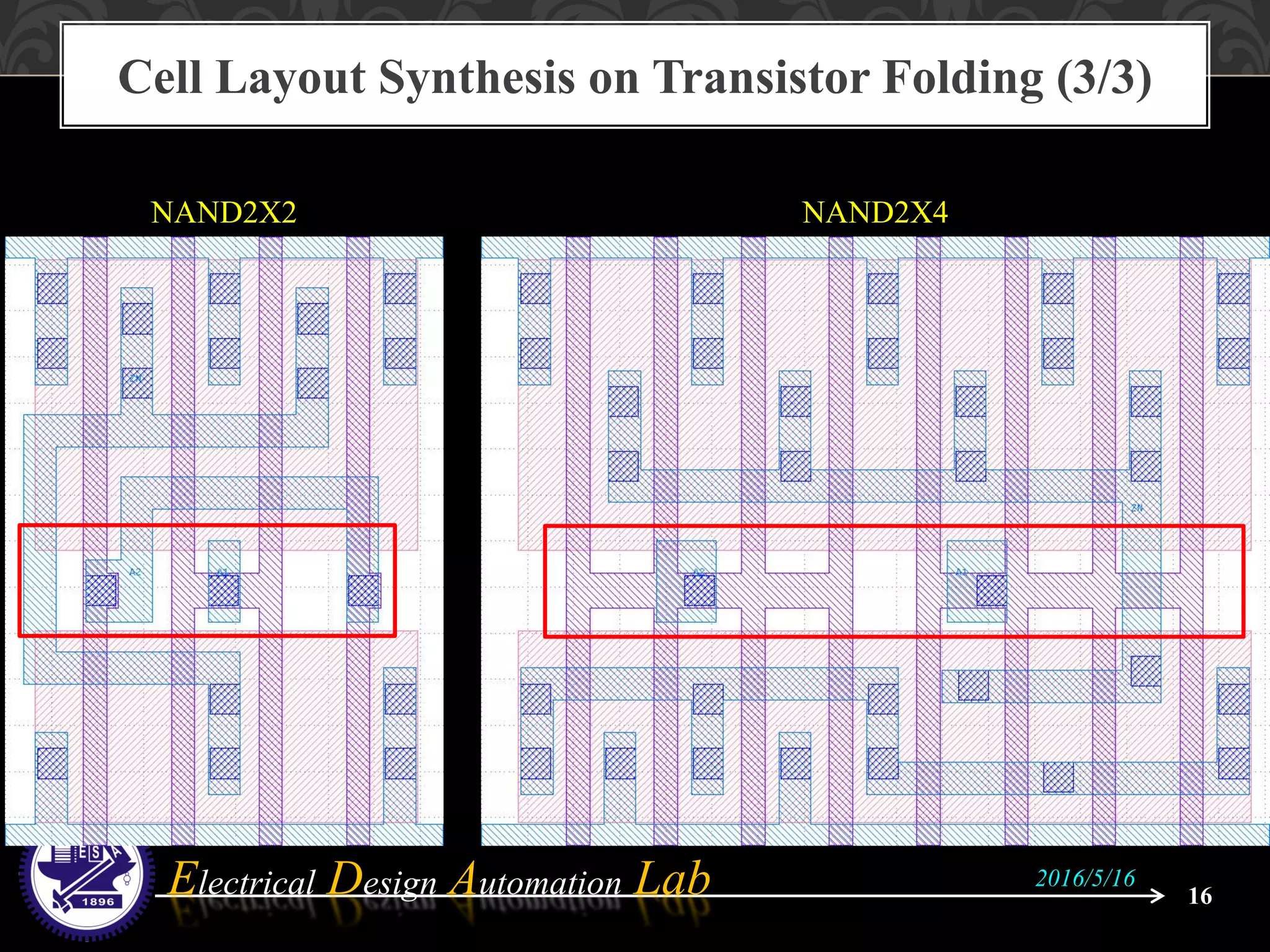

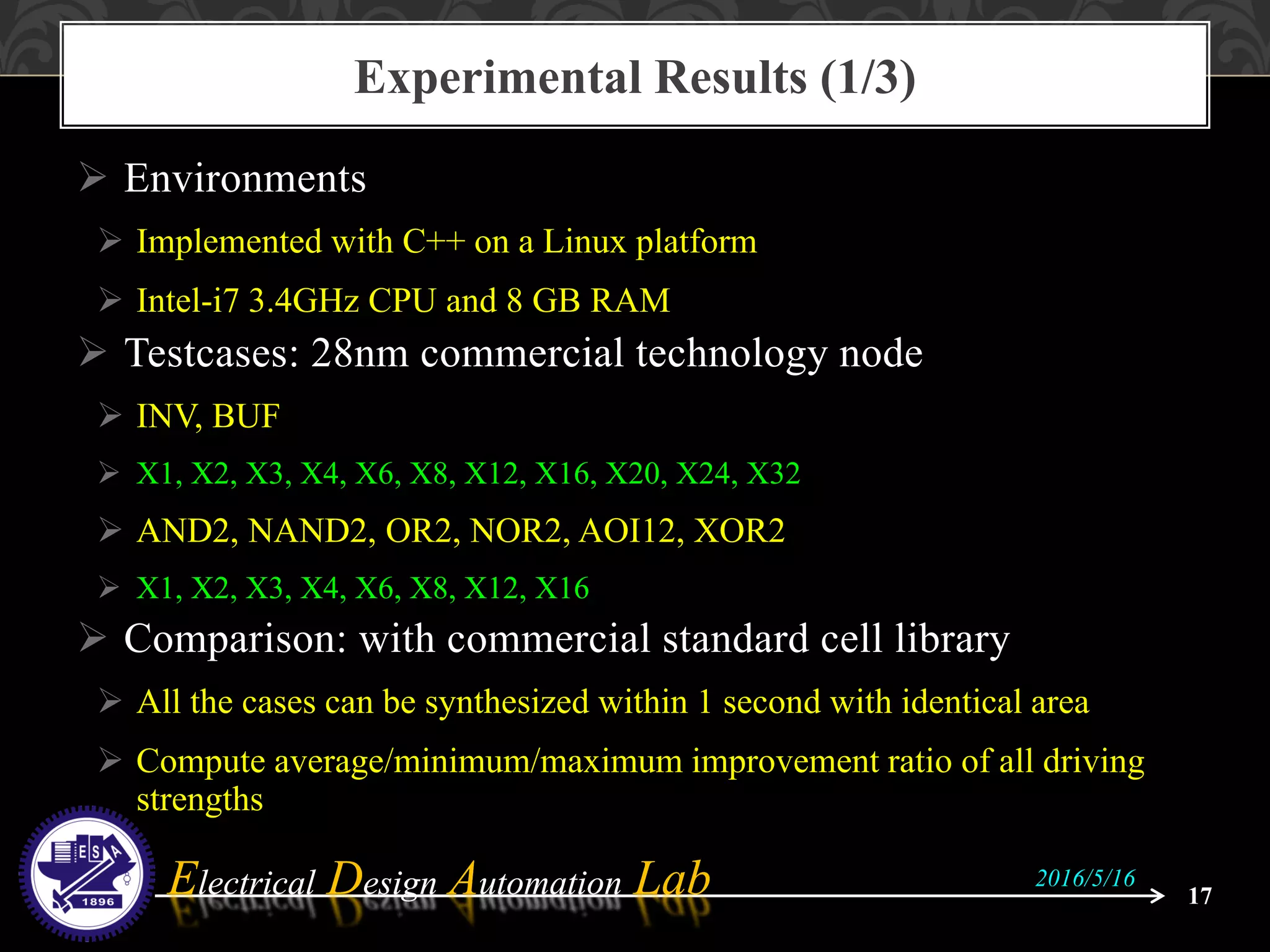

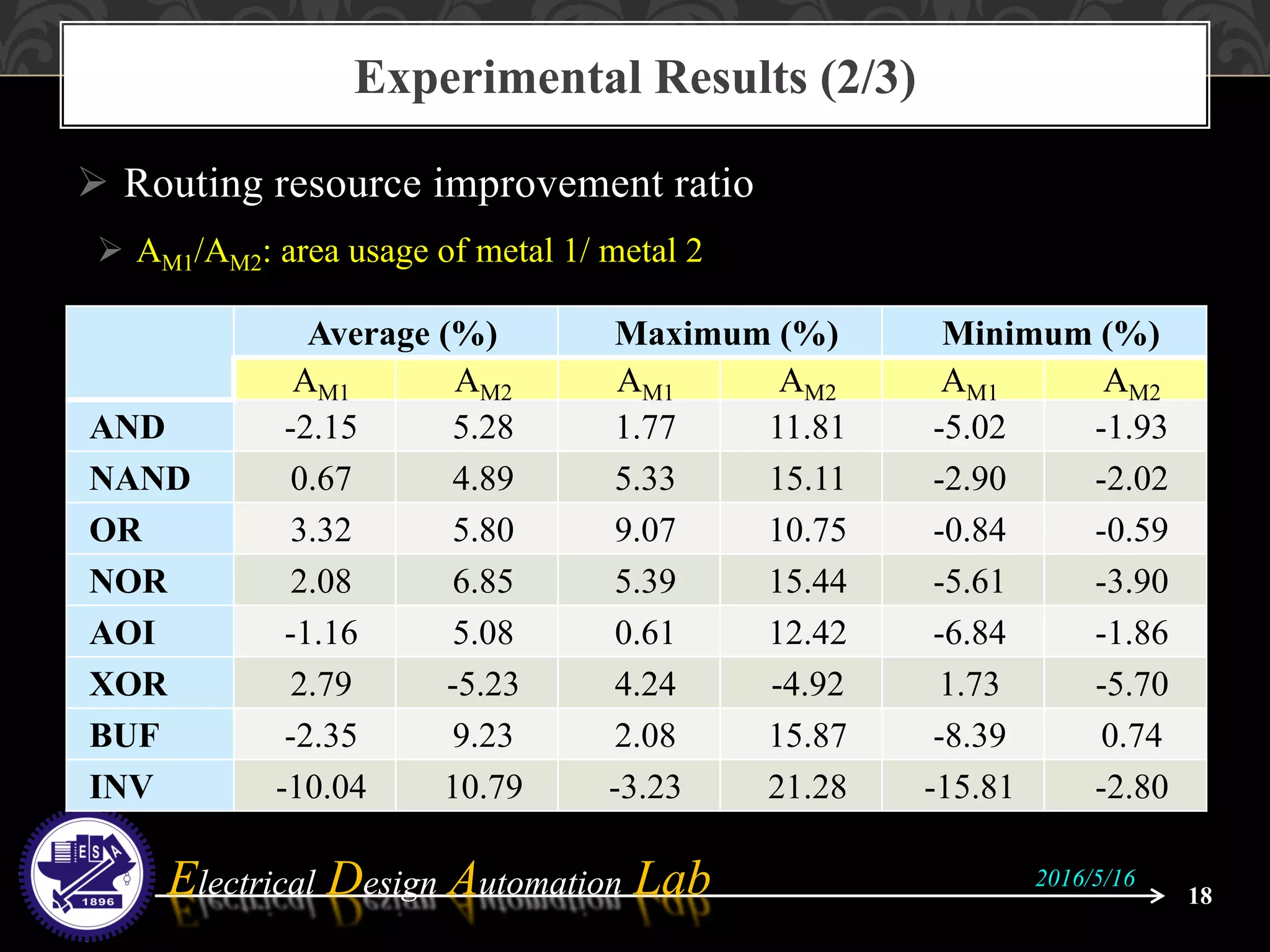

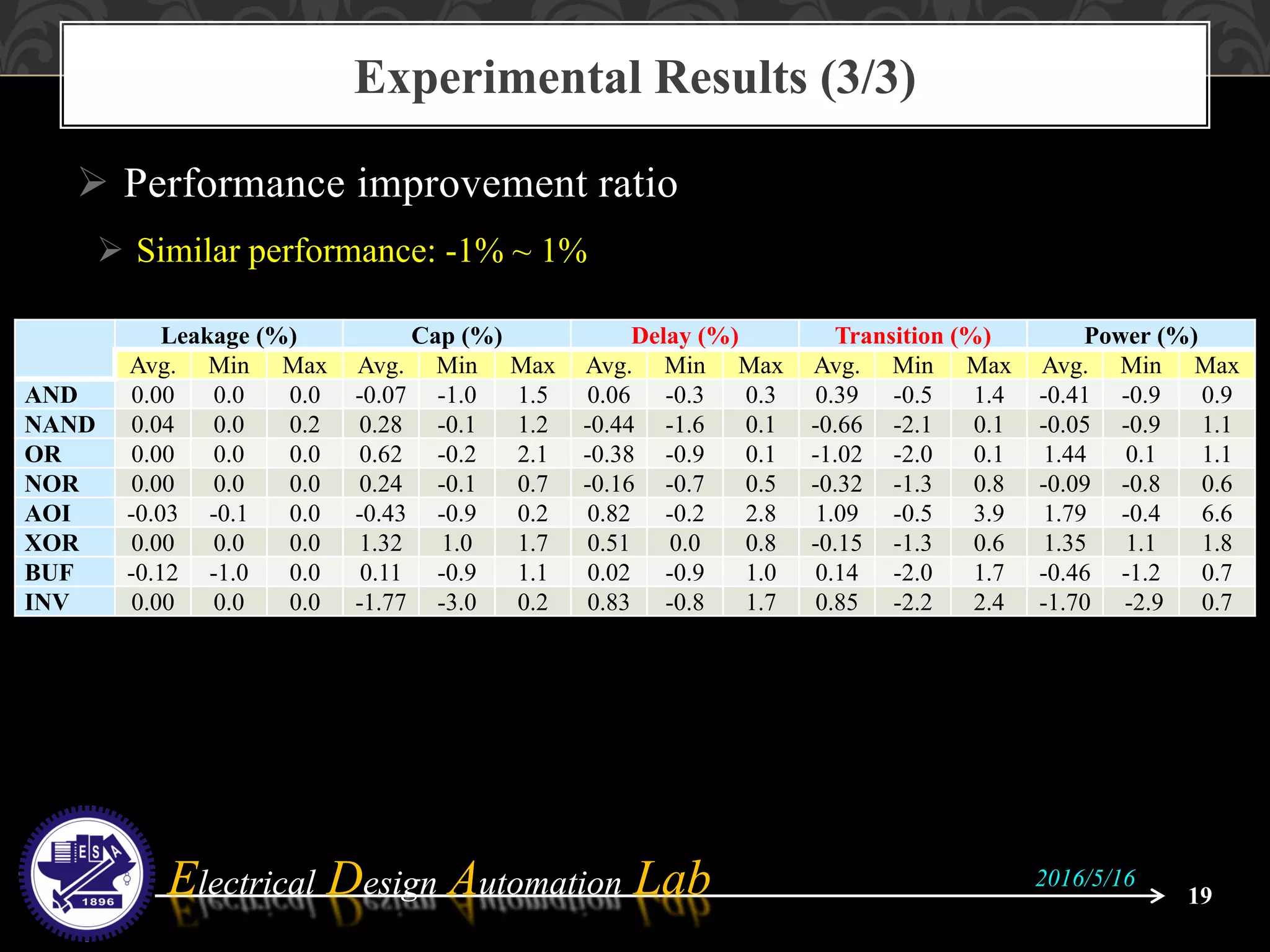

This document summarizes a presentation on standard cell layout synthesis for advanced technology nodes. It discusses the challenges of standard cell design at smaller process nodes. The presentation introduces standard cell basics and describes a cell layout synthesis flow involving transistor placement, cell routing, and transistor folding. It provides experimental results comparing the proposed flow to a commercial standard cell library, showing improvements in area and routing resources while maintaining similar performance. Future work areas discussed include routability estimation during transistor placement and new techniques for advanced process nodes.