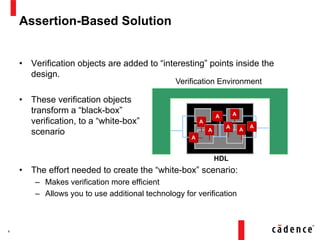

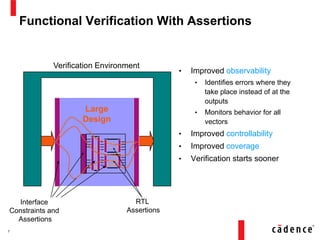

1) Assertion-based verification introduces assertions into a design to improve observability and controllability during simulation and formal analysis.

2) Assertions define expected behavior and can detect errors by monitoring signals within a design.

3) An assertion-based verification methodology leverages assertions throughout the verification flow from module to system level using various tools like simulation, formal analysis, and acceleration for improved productivity, quality, and reduced verification time.

![Assertion Example

6

A description out of the spec

“After interrupt is asserted, acknowledge must come”

intr

iack

0 1 2 3 4 5

always @(posedge intr)

begin

repeat (3) @(posedge clk);

fork: pos_pos

begin

@(posedge iack)

$display("Assertion Success",$time);

disable pos_pos;

end

begin

repeat (4) @(posedge clk);

$display("Assertion Failure",$time);

disable pos_pos;

end

join

end // always

PSL : // psl ackn_protocol : assert always

{ rose(intr)} |=> {[*2];iack }! @(posedge clk);

SVA : ackn_protocol : assert property (@(posedge clk)

$rose(intr) |=> ##2 iack);](https://image.slidesharecdn.com/kawarpal-dvclub-130422122838-phpapp02/85/Finding-Bugs-Faster-with-Assertion-Based-Verification-ABV-6-320.jpg)

![Recommended PSL and SVA Subset

14

Operators PSL SVA Notes

Sequence Delimiters

Consecutive Repetition: zero or more cycles

Consecutive Repetition: one or more cycles

Consecutive Repetition

Non-Consecutive Repetition

Sequence Concatenation (non-overlapping)

Signal Edge Detection

Previous Values of Signals

always

never

Boolean Liveness

interrupt

{...}

[*]

[+]

[*count] [*range]

[=count] [=range]

;

rose(), fell()

prev(sig, n)

always

never

eventually!

abort

not

disable iff

SVA is implicitly always by default

Boolean Overlapping Implication ->

Boolean Non-Overlapping Implication -> next Avoid nested “-> next”

(...)

[*0:$]

[*1:$]

[*count] [*range]

[*=count] [*=range]

##1

$rose(), $fell()

$past(sig, n)

Sequence Strong Interpretation ! SVA only has a strong form

SVA only has sequence form

Sequence Non-Overlapping Implication

Sequence Overlapping Implication

|=>

|->

|=>

|->

80% of assertions can be written with 20% of language

onehot, onehot0 $onehot, $onehot0Built-in Functions](https://image.slidesharecdn.com/kawarpal-dvclub-130422122838-phpapp02/85/Finding-Bugs-Faster-with-Assertion-Based-Verification-ABV-14-320.jpg)